数字电路后端设计中的一些概念.docx

《数字电路后端设计中的一些概念.docx》由会员分享,可在线阅读,更多相关《数字电路后端设计中的一些概念.docx(8页珍藏版)》请在冰豆网上搜索。

数字电路后端设计中的一些概念

数字电路后端设计中的一些概念

天线效应:

小尺寸的MOS管的栅极与很长的金属连线接在一起,在刻蚀过程中,这根金属线有可能象一根天线一样收集带电粒子,升高电位,而且可以击穿MOS管的栅氧化层,造成器件的失效。

这种失效是不可恢复的。

不仅是金属连线,有时候多晶硅也可以充当天线。

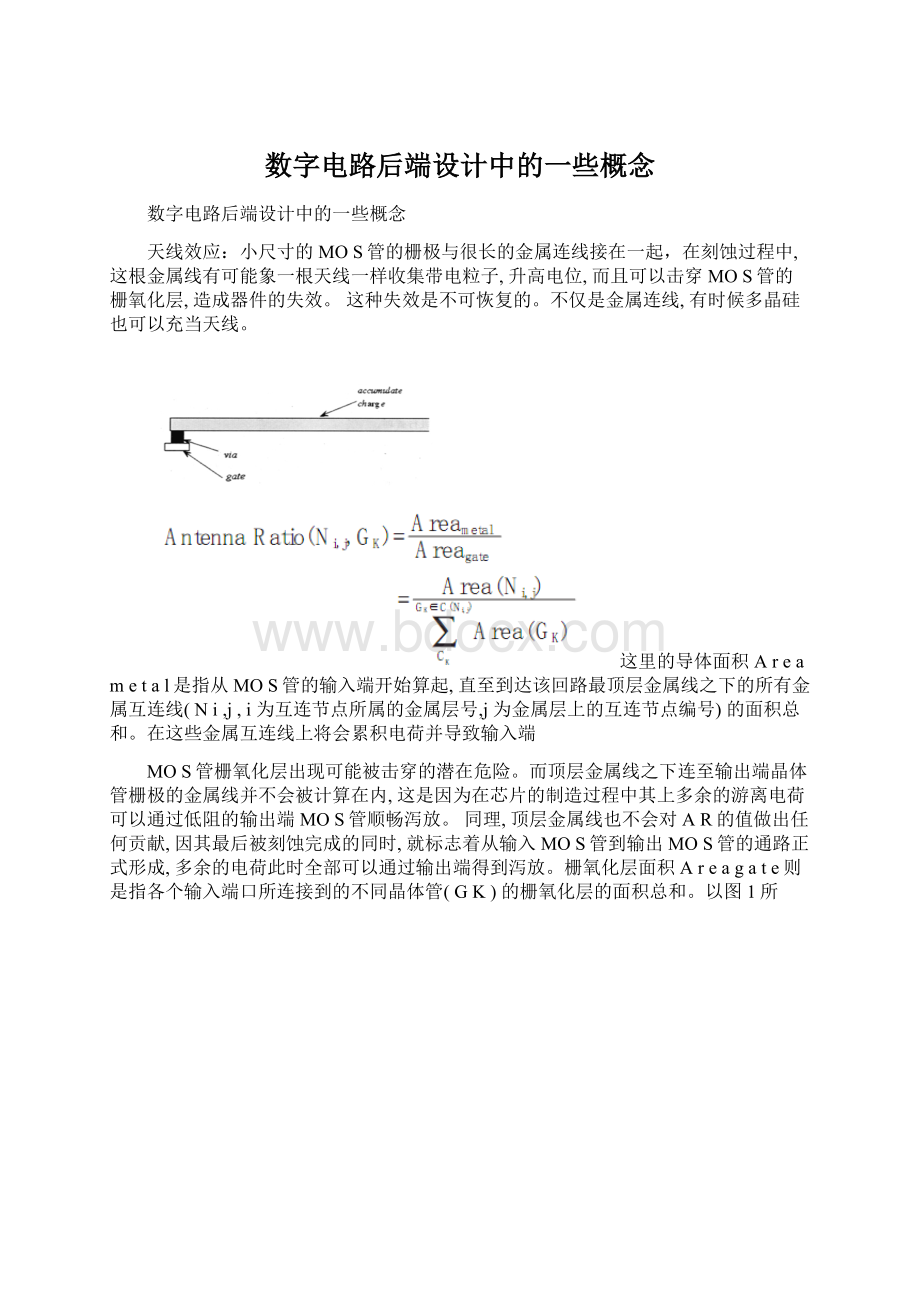

这里的导体面积Areametal是指从MOS管的输入端开始算起,直至到达该回路最顶层金属线之下的所有金属互连线(Ni,j,i为互连节点所属的金属层号,j为金属层上的互连节点编号)的面积总和。

在这些金属互连线上将会累积电荷并导致输入端

MOS管栅氧化层出现可能被击穿的潜在危险。

而顶层金属线之下连至输出端晶体管栅极的金属线并不会被计算在内,这是因为在芯片的制造过程中其上多余的游离电荷可以通过低阻的输出端MOS管顺畅泻放。

同理,顶层金属线也不会对AR的值做出任何贡献,因其最后被刻蚀完成的同时,就标志着从输入MOS管到输出MOS管的通路正式形成,多余的电荷此时全部可以通过输出端得到泻放。

栅氧化层面积Areagate则是指各个输入端口所连接到的不同晶体管(GK)的栅氧化层的面积总和。

以图1所

EM(电迁移):

电迁移是指金属材料中存在大电流的情况下,金属离子在电流作用下出现宏观移动的现象,日常生活中的家用电线等金属导线由于没有良好的散热能力,稍大的电流强度就会导致保险丝熔断而断路,因而从不出现电迁移现象。

集成电路芯片中的金属连线则不同:

它们有良好的散热环境,通常能够承受高达105A/cm2(约为普通家用电线承受极限的100倍)以上的电流强度和由此导致的大约1000C的高温。

在高温下,金属离子变得“活泼”了,大量

电子的猛烈撞击就很容易推动它们发生宏观迁移,这种迁移现象是电流造成的,因而称为电迁移。

在集成电路芯片中出现电迁移时,金属离子会在阳极附近堆积,严重时会形成小丘或突起,同时,在阴极附近的导线内出现空洞,见下图:

冗余通孔(doublevias):

热循环现象会导致铜互连线产生空隙,从而降低在较长互连线中产生的拉应力。

这些空隙最有可能在通孔的底部形成,从而使通孔成为引发良率和可靠性问题的首要因素。

这个问题可以通过以提高成品率为目的的布局来解决。

设计人员应尽可能在同一层面走线,以避免不必要的通孔。

然而,当必须放置通孔时,优化布局与布线工具能够插入一些冗余的通孔,即在只需一个通孔时放置两个或三个通孔,如下图所示。

这样,即使在某一通孔出现了空隙时,也能够保持接触,从而提高了成功接触的概率,因此可在设计进入实际生产中提高成品率。

金属脱落(Metalliftoff):

为了向芯片内部提供充足的电流,工/0PAD单元和芯片中的电源环(powerring)往往采用很宽的金属布线,但宽金属也会受到热效应影响的限制。

当芯片在正常工作时,I/OPAD单元和电源环上都会流过很大的电流,电流的热效应使金属逐渐变热。

当金属变热后,大块金属的侧边惯性阻止了侧边膨胀,从而导致了金属中部发生膨胀,这使得金属的中间区域向上膨起,这种现象叫金属脱落(Inetalliftoff)。

在芯片的长期工作中,这种膨胀现象反复发生,最终导致金属破坏芯片的绝缘层和钝化层,以致外界的杂质进入芯片,与芯片内部的材料发生反应,从而造成芯片的失效。

对于金属来说,尺寸越小,侧边惯性越小,所以这种现象对较窄的金属线影响很小,但对于宽金属线却会造成致命的损害。

因此现在的芯片制造厂商都会对金属线的宽度有一个最大值的限制,如目前TSMC0.18um工艺的这个值都是35um,而在TSMCgonm工艺这个值为12um。

在芯片的版图里,如果碰到超出这个限制值的宽金属,现在通用的解决方法是在宽金属上开槽(slot),这个方法可以有效地缓解金属热胀冷缩所造成的破坏。

由于金属开槽设计与金属的间距,膨胀系数有关,因此金属开槽的设计规则。

芯片制造厂商在设计规则中都有详细的规定。

金属密度:

金属密度(metaldensity)是除了天线效应和金属脱落外,可制造性设计中另一个重要的内容。

0.18um以上的工艺往往都设定了金属密度的最小值,但是对最大值没有限定。

但进入90nm工艺后,金属密度的最大值也进入了考虑的范畴,如下表所示。

规定金属密度最小值的原因是为了解决金属过刻的问题,而规定金属密度最大值,主要出于两个目的:

1.减少关键区域(criticalarea,CA)。

Critiealarea被定义为容易受杂质影响的区域,容易产生电路短路(short)或者开路(open)。

某个区域的金属密度越大,受杂质影响的几率越大。

2.避免金属侵蚀(MetalErosion)。

在化学机械抛光CMP过程中,由于金

属的材料相对隔离介质较软,容易产生碟形的凹槽(dishing),当金属密度太大或者金属太宽的时候,dishing进一步严重时就产生金属侵蚀。

金属侵蚀的影响就比较大了,金属层的RC参数变差,电流能力变差,电压降(IRdrop)变大,可能产生开路(oPen)等等。

所以对于宽金属要开槽,除了metalliftoff的考虑,metalerosion也是原因之一。

65纳米下时钟树性能指标的选择:

ARM9核时钟树生成时有一些约束条件,比如要求时钟偏斜小于100皮秒。

时钟偏斜要求是时钟树各项性能中最重要的,之所以选择100ps是出于设计以及工艺原因的,主要是由于65纳秒工艺库本身特性引起的。

在65纳米工艺下,由于mos元件阈值电压的降低,标准单元的速度都相对90纳米得到了提升。

对满足建立时间来说,这是好的现象;但对于保持时间来说就起到了相反的作用,因为数据的传输更快了,更容易出现保持时间的违规现象。

如公式Tclk1+Tcq+min(Tlogic)>Tclk2+Thold,得到△假使最严格情况,min(Tlogic)=0,即两个寄存器之间直接相连,完全没有多余的逻辑,此时有,△否则,在形成时钟之后在时序分析时一定会产生大量的保持时间违规现象,用人工方法去修复由于时钟设计不合理而导致的保持时间违规的话是极其费时得不偿失的。

必须通过时钟树生成中的约束来解决。

如果我们进一步忽略保持时间Thold的话,可得,△由于如前所述,65纳米工艺,标准单元的速度变快了,如果Tcq↓,所以△↓。

即时钟偏斜的允许最大值变小了。

观察了ARM9核采用的65纳米标准单元库后可以发现,一般65纳米工艺库中的寄存器元件的Tcq在快速拐角下(BestCorner)大约是100ps左右,而90纳米工艺的库中,Tcq一般是130ps左右。

很明显,65纳米工艺下时钟树的偏斜要求变得更高了,因此本次ARM核的时钟约束必须应该比90纳米的设计要严格一些。

本次ARM9核时钟树的约束必须要覆盖如上图中可能出现的最坏情况,课题在进行约束时直接定义其为100ps。

超深亚微米工艺的缺点:

硅基CMOS工艺集成电路性能的提高主要是通过对器件尺度以及电源电压进行合理的按比例缩小,但这一缩小不是无限的。

随着器件沟道长度、氧化层厚度以及电源电压的缩小,诸如短沟道效应(short

channeleffect,SCE)、漏感应势垒降低效应(Drain-InducedBarrier.Lowering,DIBL)、穿通效应(punch-through)以及热载流子效应(HCE,

hotcarriereffect)、量子隧道穿透等“次级”效应将会越来越难于克服。

漏感应势垒降低效应、量子隧道穿透等效应的增强将增大晶体管的漏电流,进而

增加器件的静态功耗。

当静态功耗在总功耗中达到一定比例,并且器件的输出电导大于其跨导时,晶体管尺寸缩小就达到了极限。

Clockgate: