时分复用解复用实验.docx

《时分复用解复用实验.docx》由会员分享,可在线阅读,更多相关《时分复用解复用实验.docx(17页珍藏版)》请在冰豆网上搜索。

时分复用解复用实验

固定及变速率时分复用、解复用实验

第一部分固定速率时分复用/解复用实验

一、实验目的

1.掌握固定速率时分复用/解复用的同步复接/分接原理。

2.掌握帧同步码的识别原理。

3.掌握集中插入帧同步码时分复用信号的帧结构特点。

二、实验容

1.搭建一个理想信道固定速率时分复用数字通信系统,使系统正常工作。

2.搭建一个理想信道固定速率时分解复用数字通信系统,使系统正常工作。

3.用示波器观察集群信号(FY_OUT)、位同步信号(BS)及帧同步信号(FS),熟悉它们的对应关系。

4.观察信号源发光管与终端发光管的显示对应关系,直接观察时分复用与解复用的实验效果。

三、实验仪器

示波器,RC-GT-II型光纤通信实验系统。

四、基本原理

1.同步复接/分接原理

固定速率时分复用/解复用通常也称为同步复接/分接。

在实际应用中,通常总是把数字复接器和数字分接器装在一起做成一个设备,称为复接分接器(缩写为Muldex)。

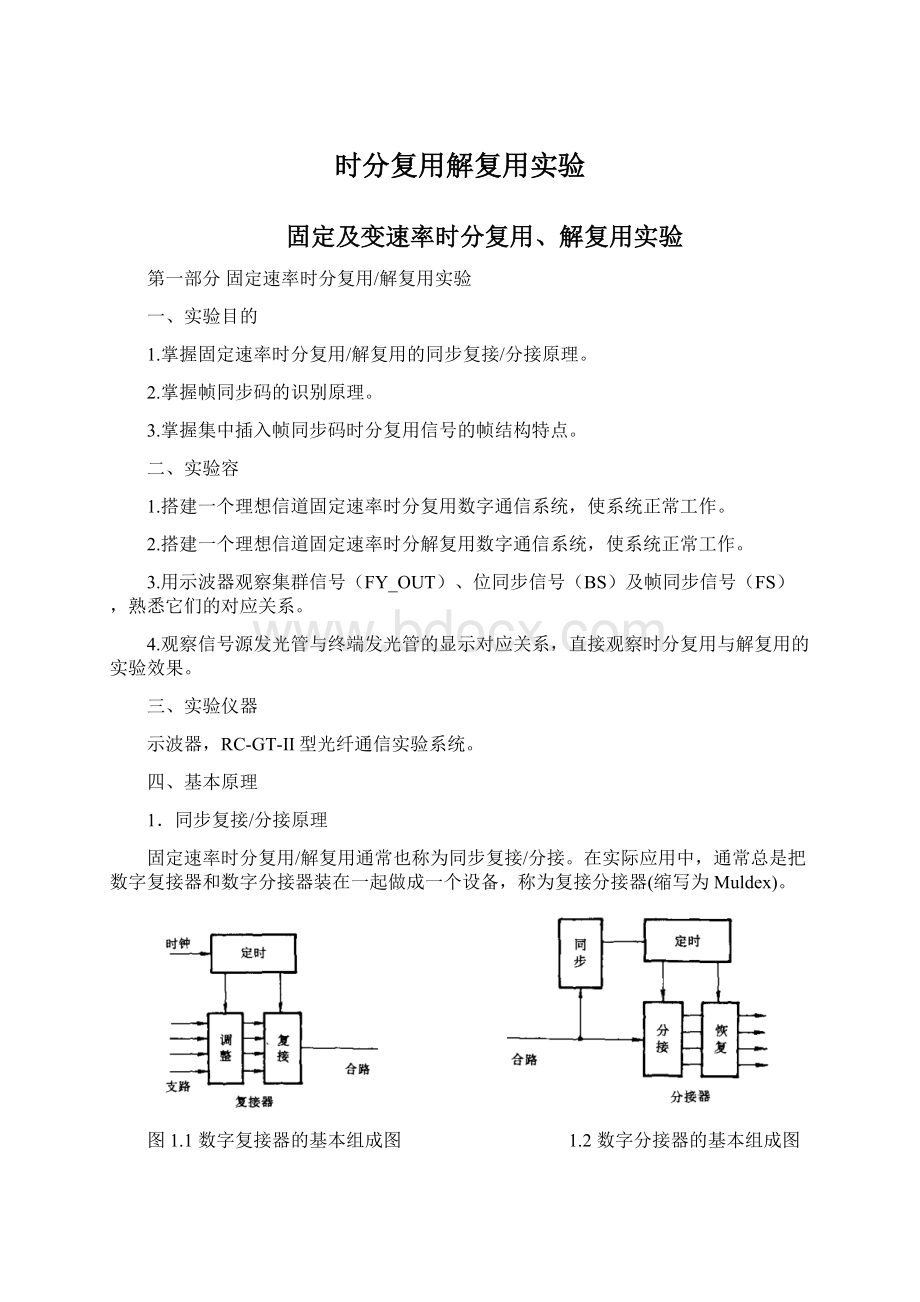

图1.1数字复接器的基本组成图 1.2数字分接器的基本组成图

数字复接器的基本组成如图1.1所示。

数字复接器的作用是把两个或两个以上的支路数字信号按时分复接方式合并成为单一的合路数字信号。

数字复接器由定时、调整和复接单元所组成。

定时单元的作用是为设备提供统一的基准时间信号,备有部时钟,也可以由外部时钟推动。

调整单元的作用是对各输入支路数字信号进行必要的频率或相位调整,形成与本机定时信号完全同步的数字信号。

复接单元的作用是对已同步的支路信号进行时间复接以形成合路数字信号。

数字分接器的基本组成如图1.2所示。

数字分接器的作用是把一个合路数字信号分解为原来支路的数字信号。

数字分接器由同步、定时、分接和恢复单元所组成。

定时单元的作用是为分接和恢复单元提供基准时间信号,它只能由接收的时钟来推动。

同步单元的作用是为定时单元提供控制信号,使分接器的基准时间与复接器的基准时间信号保持正确的相位关系,即保持同步。

分接单元与复接单元相对应,分接单元的作用是把输入的合路数字信号(高次群)实施时间分离。

分接器的恢复单元与复接器的调整单元相对应,恢复单元的作用是把分离后的信号恢复成为原来的支路数字信号。

将低次群复接成高次群的方法有三种;逐比特复接;按码字复接:

按帧复接。

在本实验中,由于速率固定,信息流量不大,所以我们所应用的方式为按码字复接,下面我们把这种复接方式作简单介绍。

按码字复接:

对本实验来说,速率固定,信息结构固定,每8位码代表一“码字”。

这种复接方式是按顺序每次复接1个信号的8位码,输入信息的码字轮流被复接。

复接过程是这样的:

首先取第一路信息的第一组“码字”,接着取第二路信息的第一组“码字”,再取第三信息的第一组“码字”,轮流将3个支路的第一组“码字”取值一次后再进行第二组“码字”取值,方法仍然是:

首先取第一路信息的第二组码,接着取第二路信息的第二组码,再取第三路信息的第二组码,轮流将3个支路的第二组码取值一次后再进行第三组码取值,依此类推,一直循环下去,这样得到复接后的二次群序列(d)。

这种方式由于是按码字复接,循环周期较长,所需缓冲存储器的容量较大,目前应用的很少。

图1.3按码字复接示意图

(a)第一路信息;(b)第二路信息;(c)第三路信息;(d)复接后

2.本实验所用的同步复接模块的结构原理

本实验所用到的固定速率时分复用端的原理方框图如图1.4所示。

这些模块产生三路信号时分复用后的FY_OUT信号,信速率约为128KB,帧结构如图1.5所示。

帧长为24位,其中首位无定义,第2位到第8位是帧同步码(7位巴克码1110010),另外16位为2路数据信号,每路8位。

此FY_OUT信号为集中插入帧同步码时分复用信号。

同时通过发光二极管来指示码型状态:

发光二极管亮状态表示1码,熄状态表示0码。

本实验中用到的电路,除并行码产生器和8选一电路是由分立器件组成的外,其他电路全都在两片大规模集成电路XC95XL144TQ100-5(以下简称CPLD)部。

下面对时钟信号源、分频器、八选一、调整器及复接器等单元作进一步说明。

(1)时钟信号源

时钟是由晶振X1(20.48MHz)提供,它也是整个系统的时钟信号源。

20.48MHz时钟经CPLD分频得到本实验所需的时钟信号CLK1,FCLK1=4.096KHz。

图1.4复用器原理方框图

图1.5帧结构

(2)分频器

分频器一首先进行16分频,输出信号频率为256kHz。

然后采用另一分频器二完成÷2、÷4、÷8、÷16运算,输出BS、S1、S2、S3等4个信号。

BS为位同步信号,频率为128kHz。

S1、S2、S3为3个选通信号,作为八选一的选通信号,频率分别为BS信号频率的1/2、1/4和1/8。

分频器三是一个二一十进制加计数器,对BS信号进行24分频,分别输出选通信号S4、S5,这两个信号的频率相等、等于BS信号频率的1/24。

其中S5作为帧同步时钟FS。

分频器输出的S1、S2、S3、S4、S5等5个信号的波形如图1.6(a)和1.6(b)所示。

图1.6分频器输出信号波形

(3)八选一

采用8路数据选择器74LS151,它含了8路传输数据开关、地址译码器和三态驱动器,其真值表如表1-1-1所示。

U100、U101和U102的地址信号输入端A、B、C并连在一起并分别接S1、S2、S3信号,它们的8个数据信号输入端x0~x7分别与K100、K101、K102输出的8个并行信号连接。

由表1.1可以分析出U100、U101、U102输出信号都是码速率为128KB、以8位为周期的串行信号。

表1.174151真值表

C

B

A

INH

DIS

Z

0

0

0

0

0

x0

0

0

1

0

0

x1

0

1

0

0

0

x2

0

1

1

0

0

x3

1

0

0

0

0

x4

1

0

1

0

0

x5

1

1

0

0

0

x6

1

1

1

0

0

x7

Φ

Φ

Φ

1

0

0

Φ

Φ

Φ

Φ

1

高阻

(4)调整器

调整器的作用是将输入的3路串行信号进行速率及时隙调整,以达到复接的时序要求。

(5)复接器

如图1.3中所示,三路串行信号a,b,c经复接口后的复接输出信号FY_OUT见波形d。

复接器主要有两种复接电路:

一种为同步复接电路,一种为异步复接电路,在固定速率时分复用时,由于被复接的三个支路是同步的信号,所以本实验采用的是同步复接电路,而异步复接电路将在变速率时分复用实验中进行细述。

图1.7复接波形示意图

在本实验中,送入复接器的三路信号为同频同相的信号,且帧长一样,我们所使用的复接方式为按码字复接,即一次复接8位码,示意图如图1.7所示。

其中:

F1、F2、F3分别为复接时钟,D1、D2、D3为调整后的三路数据,FY_OUT为复接后的信号。

FS信号可用作示波器的外同步信号,以便观察FY_OUT的帧结构。

FS信号、FY_OUT信号之间的相位关系如图1.8所示,图中FY_OUT的无定义位为0,帧同步码为1110010,数据1为11110000,数据2为00001111。

FS信号的低电平、高电平分别为8位和16位数字信号时间,其上升沿比NRZ-OUT码第一位起始时间超前一个码元。

图1.8FS、FY-OUT波形

3.本实验所用的同步分接模块的结构原理

分接端原理方框图如图1.9所示。

它输入单极性非归零信号(帧结构如图1.10所示),由位同步信号提取电路和帧同步信号产生器产生位同步时钟信号(BS)和帧同步信号(FS),通过BS、FS这把两路数据信号从时分复用信号中分离出来,两个8位的并行数据信号,两个并行信号驱动16个发光二极管,左边8个发光二极管显示第一路数据,右边8个发光二极管显示第二路数据,二极管亮状态表示“1”,熄灭状态表示“0”。

两个串行数据信速率为数字源输出信速率的1/3。

图1.9分接端原理方框图

图1.10FY_OUT信号帧结构

本实验用到的电路中,除了显示电路是由分立器件组成的外,其他电路全都在两片大规模集成电路XC95XL144TQ100-5(以下简称CPLD)部。

各组成模块功能说明:

1)位同步提取器(全数字锁相环):

位同步提取器的作用是:

从输入的FY_IN信号中提取位同步信息,通过数字锁相环产生本地的位同步时钟信号BS,该位同步信号(BS)为整个解复用电路的主要时钟信号。

数字锁相的原理方框图如图1.11所示,它由稳定度振荡器、分频器、相位比较器和控制器组成。

其中,控制器包括图中的扣除门、附加门和“或门”。

高稳定度振荡器产生的信号经整形电路变成周期性脉冲,然后经控制器再送入分频器,输出位同步脉冲序列。

若接收码元的速率为F(波特),则要求位同步脉冲的重复速率也为F(赫)。

这里晶振的振荡频率设计在nF(赫),由晶振输出经整形得到重复频率为nF(赫)的窄脉冲(图1.11中的b(b’))。

如果接收端晶振输出经n次分频后,不能准确地和收到的码元信号同频同相,这时就要根据相位比器输出的误差信号,通过控制器对分频器进行调整。

从经微分、调整后的码元信息中就可以获得接收码元所有过零点的信息,其工作波形如图1.12所示。

得到接收码元的相位后,再将它加于相位比较器去比较。

首先,先不管图中的迟延3,设接收信号为不归零脉冲(波形a),我们将每个码元的宽度分两个区,前半码元称为“滞后区”,即若位同步脉冲波形b落入此区,表示位同步脉冲的相位滞后于接收码元的相位;同样,后半码元称为“超前区”。

接收码元经微分调整,并经迟延4电路后,输出如波形e所示的脉冲。

当位同步脉冲波形b(它是由n次分频器d端的输出,取其上升沿而形成的脉冲)位于超前区时,波形e和分频器d端的输出波形d使与门A有输出,该输出再经过迟延1就产生一超前脉冲(波形f)。

若位同步脉冲波形b’(图中的虚线表示)落于滞后区,分频器c端的输出波形(c端波形和d端波形为反相关系)如波形c’所示,则与门B有输出,再经过迟延2产生一滞后脉冲(波形g)。

这样,无论位同步脉冲超前或滞后,都会分别送出超前或滞后脉冲对加于分频器的脉冲进行扣除或附加,因而达到相位调整的目的。

图1.12波形图

现在讨论图中的迟延3的作用。

同波形图看到,位同步脉冲帅分频器d端输出波形(波形d)的正沿而形成的,所以相位调整的最后结果应该合波形d的正沿对齐窄脉冲e(即d的正沿位于窄脉冲之)。

若d端产输出波形最后调整到如波形图d'所示的位置,则A、B两个与门都有输出;先是通过与门B输出一个滞后脉冲,后是通过与门A输出一超前脉冲。

这样调整的结果使位同步信号的相位稳定在这一位置,这是我们所需要的。

然而,如果d端的输出波形调整到波形图d’’的位置,这时,A、B两个与门出都有输出,只是这时是先通过A门输出一超前脉冲,而后通过B门输出一滞后脉冲。

如果不采取措施,位同步信号的相位也可以稳定在这一位置,则输出的位同步脉冲(波形b)就会与接收码元的相位相差180°。

克服这种不正确锁定的办法,是利用在这种情况下A门先有输出的这一特点。

当A门先有输出时,这个输出一方面产和超前脉冲对锁相环进行调整;另一方面,这个输出经迟延3产生一脉冲将与门B封闭,不会再产生滞后脉冲。

这样通过A六不断输出超前脉冲,就可以高速分频器的输出的相位,直到波形d的正沿对齐窄脉冲(波形e)为止。

2)帧同步电路

图1.13帧同步电路组成框图

帧同步电路如图1.13可知,整个帧同步电路主要由分频器、帧同步码识别器、脉冲生成器和同步保护器四大部分组成。

各组成电路的作用分别如下:

分频器:

主要是将位同步信号进行24分频得到与信源的帧同步信号同频的准帧同步信号,然后送入脉冲生成器进行相位调整。

帧