vhdl实验报告9176339.docx

《vhdl实验报告9176339.docx》由会员分享,可在线阅读,更多相关《vhdl实验报告9176339.docx(26页珍藏版)》请在冰豆网上搜索。

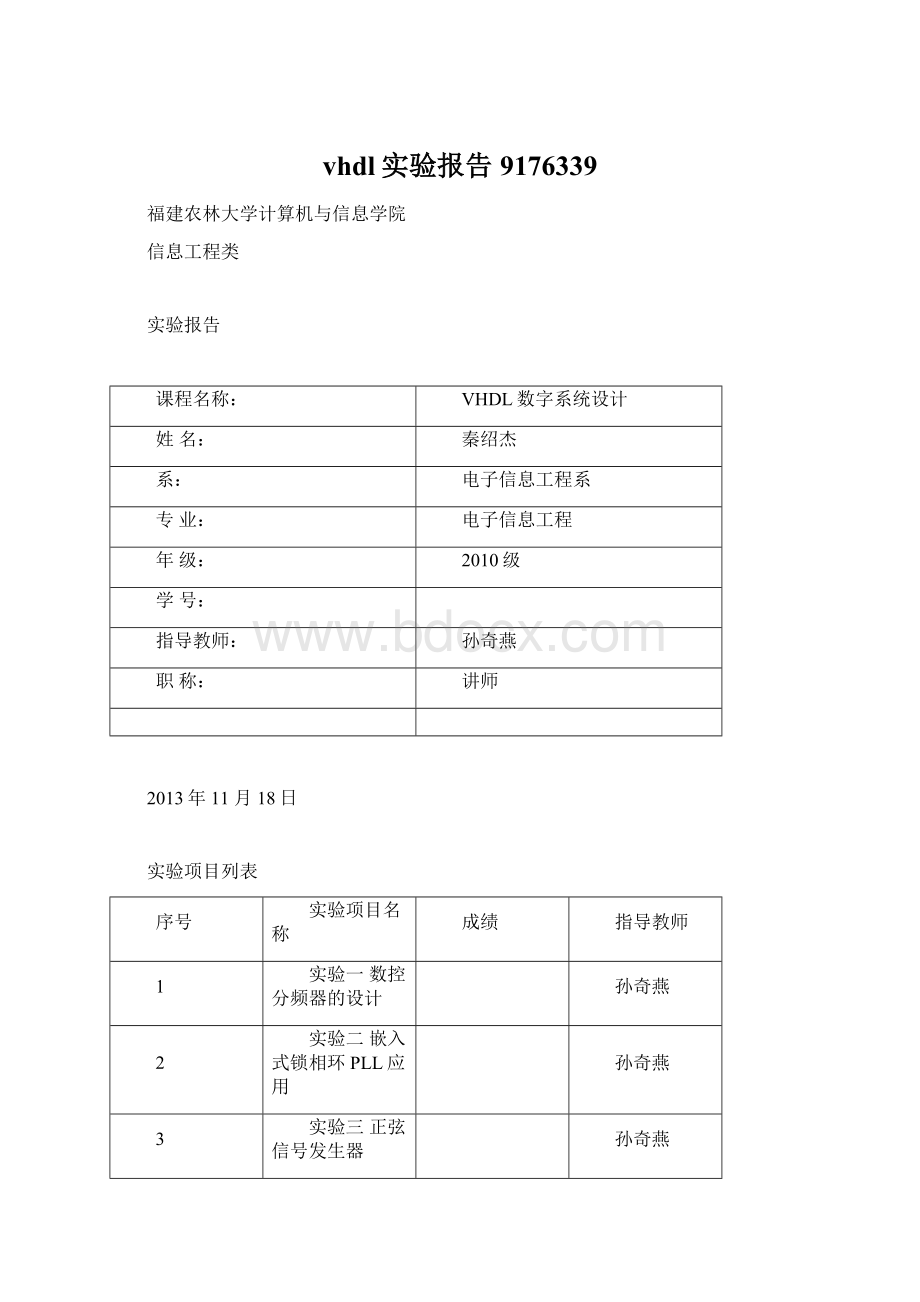

vhdl实验报告9176339

福建农林大学计算机与信息学院

信息工程类

实验报告

课程名称:

VHDL数字系统设计

姓名:

秦绍杰

系:

电子信息工程系

专业:

电子信息工程

年级:

2010级

学号:

指导教师:

孙奇燕

职称:

讲师

2013年11月18日

实验项目列表

序号

实验项目名称

成绩

指导教师

1

实验一数控分频器的设计

孙奇燕

2

实验二嵌入式锁相环PLL应用

孙奇燕

3

实验三正弦信号发生器

孙奇燕

4

实验四频率计

孙奇燕

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

福建农林大学计算机与信息学院信息工程类实验报告

系:

电子信息工程系专业:

电子信息工程年级:

2010级

姓名:

秦绍杰学号:

实验课程:

VHDL数字系统设计

实验室号:

__田C407实验设备号:

36实验时间:

11.12

指导教师签字:

成绩:

实验一数控分频器的设计

1.实验目的和要求

学习数控分频器的设计、分析和测试方法。

2.实验原理

信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相接即可,详细设计程序如例1所示。

数控分频器的仿真波形如图1所示:

输入不同的CLK频率和预置值D,给出如图1的时序波形。

图1当给出不同输入值D时,FOUT输出不同频率(CLK周期=50ns)

3.主要仪器设备(实验用的软硬件环境)

实验的硬件环境是:

微机一台

GW48EDA实验开发系统一套

电源线一根

十芯JTAG口线一根

USB下载线一根

USB下载器一个

示波器

实验的软件环境是:

QuartusII9.0软件

4.操作方法与实验步骤

(1)创建工程,并命名位test。

(2)打开QuartusII,建立VHDL文件,并输入设计程序。

保存为DVF.

(3)选择目标器件。

Acex1k—EP1K100QC208-3。

(4)启动编译。

(5)建立仿真波形图。

(6)仿真测试和波形分析。

(7)引脚锁定编译。

(8)编程下载。

(9)硬件测试

5.实验内容及实验数据记录

在实验系统上硬件验证例5-20的功能。

可选实验电路模式1(第一章图4);键2/键1负责输入8位预置数D(PIO7-PIO0);CLK由clock0输入,频率选65536Hz或更高(确保分频后落在音频范围);输出FOUT接扬声器(SPKER)。

编译下载后进行硬件测试:

改变键2/键1的输入值,可听到不同音调的声音。

6.实验数据处理与分析

1)实验代码

【例1】

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDVFIS

PORT(CLK:

INSTD_LOGIC;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

FOUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREoneOFDVFIS

SIGNALFULL:

STD_LOGIC;

BEGIN

P_REG:

PROCESS(CLK)

VARIABLECNT8:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFCNT8=""THEN

CNT8:

=D;--当CNT8计数计满时,输入数据D被同步预置给计数器CNT8

FULL<='1';--同时使溢出标志信号FULL输出为高电平

ELSECNT8:

=CNT8+1;--否则继续作加1计数

FULL<='0';--且输出溢出标志信号FULL为低电平

ENDIF;

ENDIF;

ENDPROCESSP_REG;

P_DIV:

PROCESS(FULL)

VARIABLECNT2:

STD_LOGIC;

BEGIN

IFFULL'EVENTANDFULL='1'THEN

CNT2:

=NOTCNT2;--如果溢出标志信号FULL为高电平,D触发器输出取反

IFCNT2='1'THENFOUT<='1';ELSEFOUT<='0';

ENDIF;

ENDIF;

ENDPROCESSP_DIV;

END;

2.)实验仿真

2.1输入代码

2.2编译测试

2.3引脚锁定

2.4软件仿真结果

2.5VHDL文本输入法时序仿真波形

●错误波形

●调试后得到正确波形

3)硬件相关部分的测试

2)硬件测试结果

可以听到不同的蜂鸣器声音,改变CLK的选择项可以变换声音的频率。

7.质疑、建议、问题讨论

建议:

在编程时,可以使用结构化的思想,这样程序检查起来比较方便,调试时也较方便,只要一个模块一个模块进行调就可以,利用结构化编程的优势。

总结:

经过本次实验学会了数控分频器的设计、分析和测试方法,根据按键输入的FPGA数值,数码管进行显示,以及时钟频率改变蜂鸣器的音调来体现数控分频的,理解了分频的概念。

知道了信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,明白了实现的方法是将计数溢出位与预置数加载输入信号相接即可。

对软件工程的一些错误理解有了重新的认识。

在设计过程中,遇到了很多问题,在解决这些问题的过程中,对它们有了重新的正确认识。

福建农林大学计算机与信息学院信息工程类实验报告

系:

电子信息工程系专业:

电子信息工程年级:

2010级

姓名:

秦绍杰学号:

实验课程:

VHDL数字系统设计

实验室号:

__田C407实验设备号:

36实验时间:

11.12

指导教师签字:

成绩:

实验二嵌入式锁相环PLL应用

1.实验目的和要求

学习使用Cyclone器件中的嵌入式锁相环,为以后的设计作准备。

2.实验原理

锁相环路(PLL)亦称自动相位控制(APC)电路,它是一种利用相位误差消除频率误差的反馈控制系统。

如图1所示,由鉴相器(相位比较器)、环路滤波器(低通滤波器)和压控振荡器三个基本部件组成。

3.主要仪器设备(实验用的软硬件环境)

实验的硬件环境是:

微机一台

GW48EDA实验开发系统一套

电源线一根

十芯JTAG口线一根

USB下载线一根

USB下载器一个

示波器

实验的软件环境是:

QuartusII9.0软件

4.操作方法与实验步骤

1.打开QuartusII,创建一新工程,工程名称为PLLs,顶层实体名为GW_PLL。

2.建立PLL模块

3.创建顶层文件并仿真PLL模块

4.实测PLL模块

5.实验内容及实验数据记录

调用PLL的LPM模块创建GW_PLL.vhd的顶层文件编译并仿真。

修改PLL的输出频率,再次编译仿真。

步骤如下:

(一)建立PLL模块

1、首先创建一新工程,工程名称为PLLs,顶层实体名为GW_PLL。

2、在QuartusII的Tools菜单中选择MegaWizardPlug-InManager,对弹出的界面选择Createanewcustom…项,定制一个新的模块。

在弹出的对话框,在左栏选择I/O项下的ALTPLL,再选Cyclone器件和VHDL语言方式,最后输入设计文件存放的路径和文件名,如d:

\PLLs\PLL50.vhd。

单击Next按钮后弹出图1所示的窗口。

2、在图1所示窗口中首先设置参考时钟频率inclk0为50MHz,注意,这个时钟频率不能低于16MHz,接着在图1所示的窗口中选择锁相环的工作模式(选择内部反馈通道的通用模式)。

单击Next按钮后即进入图2所示的窗口。

在此窗口主要选择PLL的控制信号,如PLL的使能控制pllena;异步复位areset;锁相输出locked等。

为了简便,在此消去所有控制信号。

选择第一个输出时钟信号c0相对于输入时钟的倍频因子是2,图3所示的窗口中选中Usethisc1,即选择另一输出时钟端c1,相对输入时钟的倍频因子是1/2,时钟相移和时钟占空比不变,保持原来默认的数据。

4、连续点击“Next”完成设计。

(二)创建顶层文件并仿真PLL模块(参考《EDA技术与VHDL》第7章)

下例是调用了锁相环PLL50模块的顶层设计文件,,顶层文件用VHDL编写,保存为GW_PLL.vhd,用setastoplevelEntity设为顶层文件编译并仿真。

图1选择参考时钟为50MHz(输入频率不能小于16MHz)

图2选择控制信号

图3选择输出频率为75MHz

图4修改输出频率选择

(三)实测PLL模块

对于工程GW_PLL,选择器件为EP1C3TC144,锁相环的频率输入端只能是pin16和pin17脚,在此不仿锁在pin17上,恰好对应实验箱的clock2(clock5对应pin16),所以在实验中要用一短线将Clock0的50MHz信号引接到clock5的输入端(要拔去其上的短路帽,引过来的短线接靠左排上任一针上),输出可锁定于任何一I/O口上。

在此锁在GW48箱上右排座下端的标有“IO26”上,它对应pin67。

编译后下载,用频率计测试此端的频率输出,应该为75MHz。

6.实验数据处理与分析

1.实验代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYGW_PLLIS

PORT(CLK0:

INSTD_LOGIC;

FOUT0:

OUTSTD_LOGIC);

ENDGW_PLL;

ARCHITECTUREbehavOFGW_PLLIS

COMPONENTPLL50

PORT(inclk0:

INSTD_LOGIC:

='0';

c0:

OUTSTD_LOGIC);

ENDCOMPONENT;

BEGIN

u1:

PLL50PORTMAP(inclk0=>CLK0,c0=>FOUT0);

ENDbehav;

2.实验测试

设计同时输出3个不同频率的PLL模块。

波形如图17.4仿真波形图:

图17.4选择输出频率为75MHz

7.质疑、建议、问题讨论

通过本次实验,学会了如何建立模块,如何创建顶层文件以及对模块的仿真,虽然对PLL的相关知识了解的不多,但通过此次实验初步了解了什么是PLL以及相关的一些设置和操作,但在实践中明显还很是生疏,有待进一步的练习与实践;实验中也要特别注意时钟频率的设置以及一些细节方面,从而减少犯错的机会。

福建农林大学计算机与信息学院信息工程类实验报告

系:

电子信息工程系专业:

电子信息工程年级:

2010级

姓名:

秦绍杰学号:

实验课程:

VHDL数字系统设计

实验室号:

田C407实验设备号:

36实验时间:

11.12

指导教师签字:

成绩:

实验三正弦信号发生器

1