EDA复习题练习.docx

《EDA复习题练习.docx》由会员分享,可在线阅读,更多相关《EDA复习题练习.docx(15页珍藏版)》请在冰豆网上搜索。

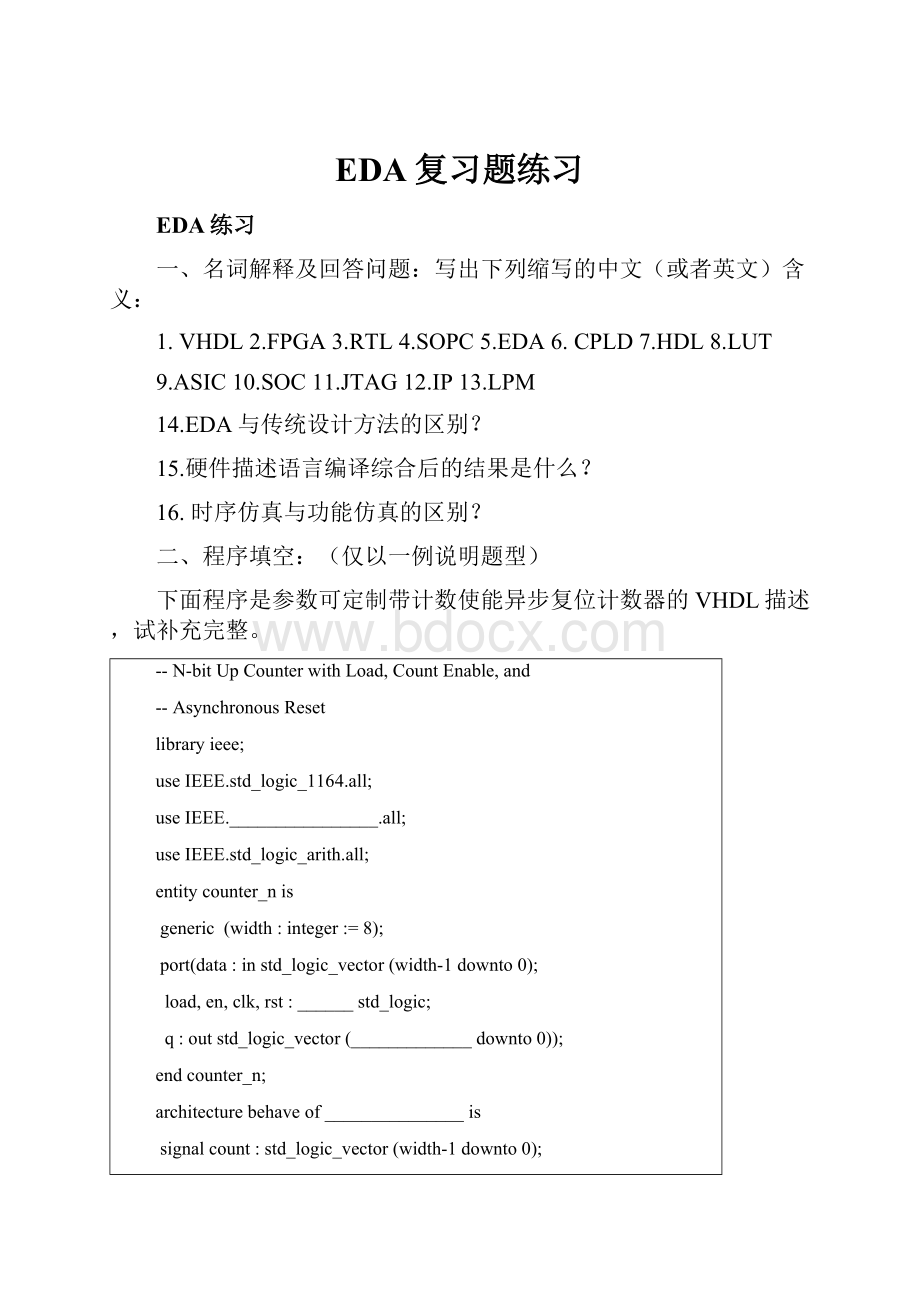

EDA复习题练习

EDA练习

一、名词解释及回答问题:

写出下列缩写的中文(或者英文)含义:

1.VHDL2.FPGA3.RTL4.SOPC5.EDA6.CPLD7.HDL8.LUT

9.ASIC10.SOC11.JTAG12.IP13.LPM

14.EDA与传统设计方法的区别?

15.硬件描述语言编译综合后的结果是什么?

16.时序仿真与功能仿真的区别?

二、程序填空:

(仅以一例说明题型)

下面程序是参数可定制带计数使能异步复位计数器的VHDL描述,试补充完整。

--N-bitUpCounterwithLoad,CountEnable,and

--AsynchronousReset

libraryieee;

useIEEE.std_logic_1164.all;

useIEEE.________________.all;

useIEEE.std_logic_arith.all;

entitycounter_nis

generic(width:

integer:

=8);

port(data:

instd_logic_vector(width-1downto0);

load,en,clk,rst:

______std_logic;

q:

outstd_logic_vector(_____________downto0));

endcounter_n;

architecturebehaveof_______________is

signalcount:

std_logic_vector(width-1downto0);

begin

process(clk,rst)

begin

ifrst='1'then

count<=_______________;――清零

elsif_______________________then――边沿检测

ifload='1'then

count<=data;

___________en='1'then

count<=count+1;

_____________;

endif;

endprocess;

________________

endbehave;

三、程序改错:

(仅以一例说明题型)

1LIBRARYIEEE;

2USEIEEE.STD_LOGIC_1164.ALL;

3

4ENTITYCNT10IS

5PORT(CLK:

INSTD_LOGIC;

6Q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

7ENDCNT10;

8ARCHITECTUREbhvOFCNT10IS

9SIGNALQ1:

STD_LOGIC_VECTOR(3DOWNTO0);

10BEGIN

11PROCESS(CLK)BEGIN

12IFRISING_EDGE(CLK)begin

13IFQ1<9THEN

14Q1<=Q1+1;

15ELSE

16Q1<=(OTHERS=>'0');

17ENDIF;

18ENDIF;

19ENDPROCESS;

20Q<=Q1;

21ENDbhv;

1.在MAX+PlusII中编译时,提示的第一条错误为:

Error:

Line12:

Filee:

\mywork\test\cnt10.vhd:

VHDLsyntaxerror:

IfstatementmusthaveTHEN,butfoundBEGINinstead

指出并修改相应行的程序(如果是缺少语句请指出大致的行数):

错误1行号:

程序改为:

错误2行号:

程序改为:

2.若编译时出现如下错误,请分析原因。

四、VHDL程序设计:

1、设计一数据选择器MUX,其系统模块图和功能表如下图所示。

试采用下面三种方式中的两种来描述该数据选择器MUX的结构体。

(a)用if语句。

(b)用case语句。

(c)用whenelse语句。

(d)用withselect语句。

2、课本4-2

3、课本例6-18、例6-19用其他方式实现。

4、设计一个3-8译码器

输入端口:

din输入端,位宽为3位

EN译码器输出使能,高电平有效

输出端口:

xout译码器输出,低电平有效

5、试描述一个带进位输入、输出的8位全加器

端口:

A、B为加数,CIN为进位输入,S为加和,COUT为进位输出

五、根据原理图写出相应的VHDL程序:

1、

2、

3、

4、

六、综合题(状态机)

1、用VHDL设计交通灯控制器

图a是一个十字路口交通灯控制示意图,H公路和V公路在路口各有两个红绿灯指示道路通行状况。

图a十字路口交通灯控制示意图

对应图a的交通灯控制器,拟用VHDL语言设计一电路模拟其控制逻辑,图b为该VHDL电路的设计模块图。

图b交通灯控制器电路设计模块图

图b中Timer模块为一定时电路,其实体说明如下:

Libraryieee;

Useieee.std_logic_1164.all;

Useieee.std_logic_unsigned.all;

Entitytimeris

Port(clk,reset,start_timer:

instd_logic;--时钟、复位、启动信号

Long,short:

outstd_logic);--20秒、4秒定时完成信号

Endtimer;

图c为Timer模块仿真波形,输入信号clk为频率1KHz的时钟信号,当复位信号reset高电平时定时器复位,启动信号start_timer为低电平时定时器清零,高电平时开始定时,定时4秒后short信号输出高电平,定时20秒后long信号输出高电平,定时器不再计数。

图cTimer模块仿真波形

问题1,请完成Timer模块的VHDL设计:

(实体说明部分已有,可不写)

图b中Controller模块的实体说明如下:

Libraryieee;

Useieee.std_logic_1164.all;

Entitycontrolleris

Port(clk,reset:

instd_logic;--时钟、复位信号

long,short:

instd_logic;--20秒、4秒定时完成信号

start_timer:

outstd_logic;--启动定时信号

h_light,v_light:

outstd_logic(1downto0));--H路、V路交通灯控制信号

Endcontroller;

其中H路、V路交通灯控制信号输出“00”表示绿灯、“01”表示黄灯、“11”表示红灯。

问题2:

Controller模块中状态迁移图如图d所示,请完成Controller模块的VHDL设计:

图dController模块状态迁移图

问题3:

根据图b的系统模块结构,完成整个交通灯电路顶层模块VHDL设计。

libraryieee;

useieee.std_logic_1164.all;

entityjtdis

port(clk,reset:

instd_logic;

h_light,v_light:

outstd_logic_vector(1downto0));

endjtd;

问题4:

在图e所示的交通灯顶层模块仿真波形图中完成输出信号h_light、v_light和controller中状态机当前状态信号c_s的仿真波形。

图e交通灯仿真波形图

2、根据如下所示状态图及其状态机结构图,回答问题

(1)试判断该状态机类型,并说明理由。

(2)请问如何消除状态机输出信号毛刺?

试列出至少两种方法,并说明理由。

(3)试由b、c两图中任选一图写出其完整的VHDL程序。

(4)已知一个简单的波形发生器的数字部分系统框图如下图所示:

图中DOWNCNT、MYROM都是在MAX+PlusII中使用MegaWizard调用的LPM模块,其VHDL描述中Entity部分分别如下:

ENTITYDOWNCNTIS

PORT

(

clock:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(5DOWNTO0)

);

ENDDOWNCNT;

ENTITYmyromIS

PORT

(

address:

INSTD_LOGIC_VECTOR(5DOWNTO0);

q:

OUTSTD_LOGIC_VECTOR(7DOWNTO0)

);

ENDmyrom;

试用VHDL描述该系统的顶层设计(使用例化语句)。

3、已知状态机状态图如图(a)所示;完成下列各题:

(1)试判断该状态机类型,并说明理由。

(2)根据状态图,写出对应于结构图(b),分别由主控组合进程和主控时序进程组成的VHDL有限状态机描述

(3)若已知输入信号如下图所示,分析状态机的工作时序,画出该状态机的状态转换值(current_state)和输出控制信号(outa);

(4)若状态机仿真过程中出现毛刺现象,应如何消除;试指出两种方法,并简单说明其原理。

4、用VHDL设计两层升降平台控制器

图a是一个两层的升降平台示意图,一层和二层各有一个按钮用来呼叫升降机。

图a两层升降平台示意图

对应图a的升降平台控制器,拟用VHDL语言设计一个电路模拟其控制逻辑,图b为该VHDL电路的设计模块图。

图b两层升降平台控制器设计模块图

图b中的cnt100模块用来控制升降台开关门延时,elev2为升降平台状态控制器。

升降台闸门由打开到关闭或由关闭到打开时,elev2模块向cnt100模块输出一个en计数使能信号(高电平有效)。

cnt100模块计数溢出(≥100)时cnt100输出cout信号为高电平,同时cnt100计数停止。

cnt100模块的实体描述如下所示:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT100IS

PORT(CLK,EN:

INSTD_LOGIC;--时钟、使能信号

COUT:

OUTSTD_LOGIC);--溢出信号

ENDCNT100;

问题1,请完成cnt100模块的VHDL设计(实体部分已给出,不用写),参考的仿真波形如图c所示。

图ccnt100仿真波形图

问题2,以下是elev2模块的VHDL描述:

请根据elev2的VHDL描述画出其状态迁移图。

libraryieee;

useieee.std_logic_1164.all;

entityelev2is

port(clk,rst:

instd_logic;--时钟、复位信号

cout:

instd_logic;--定时溢出信号

call:

instd_logic_vector(2downto1);--呼叫信号

arr:

instd_logic_vector(2downto1);--到达信号

door:

outstd_logic;--门控信号,低电平开门

up:

outstd_logic;--上升信号

down:

outstd_logic;--下降信号

en:

outstd_logic);--延时计数清零、使能信号

endelev2;

architecturebehavofelev2is

constantCL1:

std_logic_vector(2downto0):

="000";--一楼关门

constantOP1:

std_logic_vector(2downto0):

="100";--一楼开门

constantUP1:

std_logic_vector(2downto0):

="010";--一楼上升

constantDN2:

std_logic_vector(2downto0):

="001";--二楼下降

constantCL2:

std_logic_vector(2downto0):

="011";--二楼关门

constantOP2:

std_logic_vector(2downto0):

="111";--二楼开门

signalcontrol:

std_logic_vector(2downto0);--状态控制信号

begin

door<=notcontrol

(2);up<=control

(1);down<=control(0);

process(clk,rst,arr,call)

variableven:

std_logic;

begin

ifrst='1'thencontrol<=CL1;

elsifclk'eventandclk='1'then

casecontrolis

whenCL1=>ifcout='1'then--关门已完毕

ifcall

(1)='1'thencontrol<=OP1;en<='0';

elsifcall

(2)='1'thencontrol<=UP1;en<='1';

elsecontrol<=CL1;en<='1';endif;

elsecontrol<=CL1;en<='1';endif;

whenOP1=>ifcout='1'then--开门已完毕

ifcall

(1)='1'thencontrol<=OP1;en<='1';

elsecontrol<=CL1;en<='0';endif;

elsecontrol<=OP1;en<='1';endif;

whenUP1=>ifarr

(2)='1'thencontrol<=CL2;

elsecontrol<=UP1;endif;

whenDN2=>ifarr

(1)='1'thencontrol<=CL1;

elsecontrol<=DN2;endif;

whenCL2=>ifcout='1'then--关门已完毕

ifcall

(2)='1'thencontrol<=OP2;en<='0';

elsifcall

(1)='1'thencontrol<=DN2;en<='1';

elsecontrol<=CL2;en<='1';endif;

elsecontrol<=CL2;en<='1';endif;

whenOP2=>ifcout='1'then--开门已完毕

ifcall

(2)='1'thencontrol<=OP2;en<='1';

elsecontrol<=CL2;en<='0';endif;

elsecontrol<=OP2;en<='1';endif;

whenothers=>control<=CL1;

endcase;

endif;

endprocess;

endbehav;

问题3,根据图b所示升降平台模块图,写出升降平台控制器ELEV_TOP的VHDL顶层描述: