16位模型机的设计.docx

《16位模型机的设计.docx》由会员分享,可在线阅读,更多相关《16位模型机的设计.docx(20页珍藏版)》请在冰豆网上搜索。

16位模型机的设计

.

16位CPU的设计

要求:

此模型机的功能是将存储区的数据块复制到另一个存储区。

汇编代码如下:

START:

LOADIR1,0010H;源操作数地址送R1

LOADIR2,0030H;目的操作数地址送R2

LOADIR6,002FH;结束地址送R6

NEXT:

LOADR3,[R1];取数

STORE[R2],R3;存数

BRANCHGTISTART;如果R1>R6,则转向START

INCR1;修改源地址

INCR2;修改目的地址

BRANCHINEXT;转向NEXT

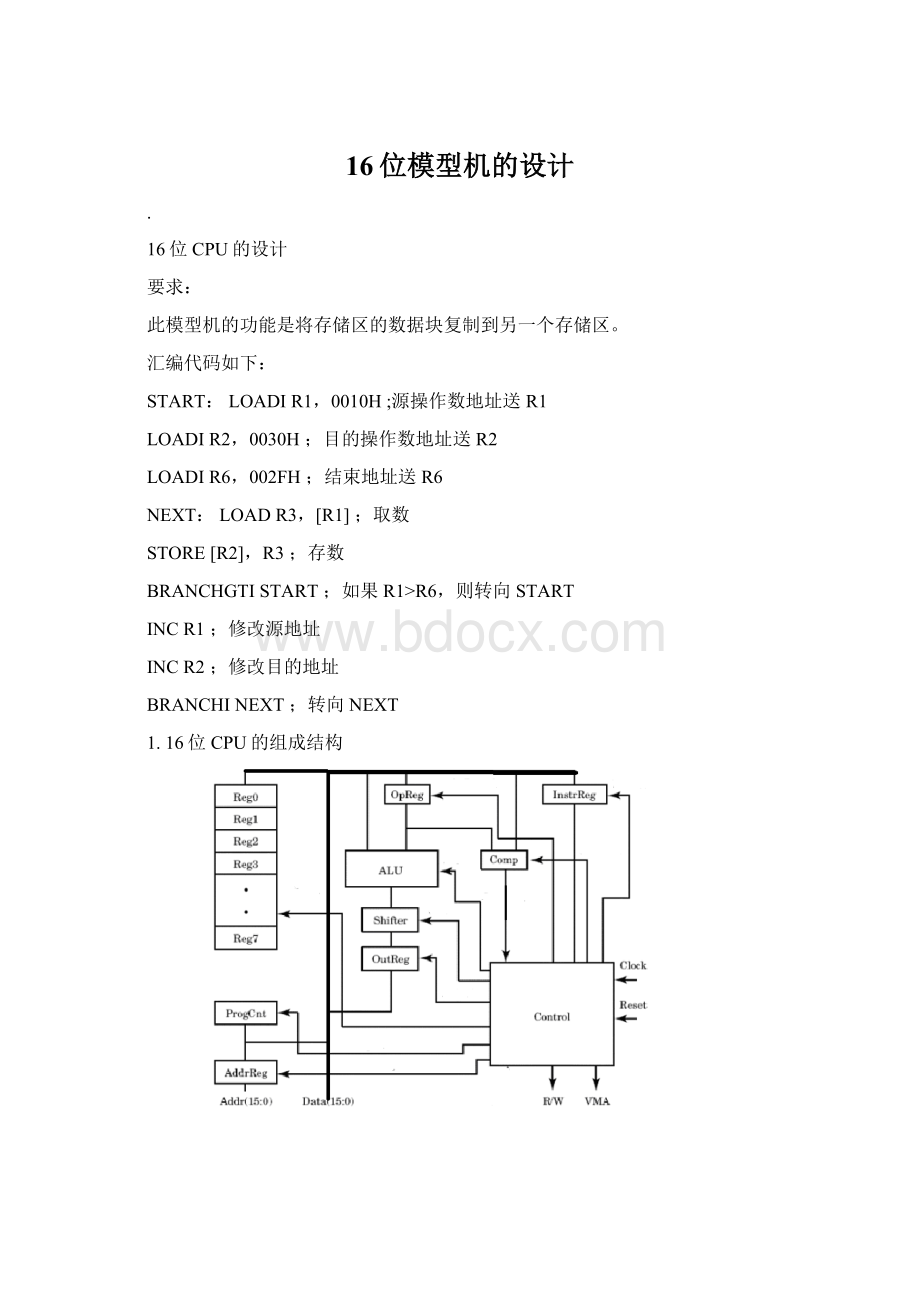

1.16位CPU的组成结构

2.指令系统的设计

一、指令格式

.'

.

单字指令格式1)

双字指令格式2)

二、指令操作码功能指令操作码00001LOAD装载数据到寄存器STORE00010将寄存器的数据存入到存储器LOADI将立即数装入到寄存器00100

BRANCHI

无条件转移到由立即数指定的地址00101

如果源寄存器内容大于目的寄存器的内容,则转移BRANCHGTI00110

到由立即数指定的地址寄存器内容加100111

指令INC

依据以上设计的指令系统,则完成数据块复制的程序如下:

地址机器码指令功能说明

LOADIR1,2001H0000H0010H源操作数地址送R1

0010H0001H

LOADIR20002H2002H,0030H目的操作数地址送R2

0030H0003H

LOADIR6,002FH2006H0004H结束地址送R6

002FH0005H

LOADR3,[R1]取数080BH0006H

存数,101AH0007HR3STORE[R2]如果0008H300EHR1BRANCHGTI0000大于R6,则转向地址0000

0000H0009H

修改源地址INCR13801H000AH

修改目的地址000BHINCR2

3802H

,实现循环2800H00006H000CH转向BRANCHI0006H

0006H

000DH

.'

.

3.VHDL设计

一、程序包:

说明运算器的功能、移动寄存器的操作、比较器的比较类型和用于CPU控制的状态类型。

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

packagecpu_libis

subtypet_shiftisunsigned(3downto0);

constantsh:

unsigned(3downto0):

=

constantsftl:

unsigned(3downto0):

=

constantsftr:

unsigned(3downto0):

=0;

constantrotl:

unsigned(3downto0):

=1;

constantrotr:

unsigned(3downto0):

=0;

subtypet_aluisunsigned(3downto0);

constantalupass:

unsigned(3downto0):

=

constantandOp:

unsigned(3downto0):

=

constantorOp:

unsigned(3downto0):

=0;

constantnotOp:

unsigned(3downto0):

=1;

constantxorOp:

unsigned(3downto0):

=0;

constantplus:

unsigned(3downto0):

=1;

constantalusub:

unsigned(3downto0):

=0;

constantinc:

unsigned(3downto0):

=1;

constantdec:

unsigned(3downto0):

=@0;

constantzero:

unsigned(3downto0):

=@1;

subtypet_compisunsigned2downto0);

constanteq:

unsigned(2downto0):

=

constantneq:

unsigned(2downto0):

=;

constantgt:

unsigned(2downto0):

=;

constantgte:

unsigned(2downto0):

=;

constantlt:

unsigned(2downto0):

=@;

constantlte:

unsigned(2downto0):

=A;

subtypet_regisstd_logic_vector(2downto0);

typestateis(reset1,reset2,reset3,reset4,reset5,reset6,execute,nop,load,store,move,

.'

.

load2,load3,load4,store2,store3,store4,move2,move3,move4,

incPc,incPc2,incPc3,incPc4,incPc5,incPc6,loadPc,loadPc2,loadPc3,loadPc4,

bgtI2,bgtI3,bgtI4,bgtI5,bgtI6,bgtI7,bgtI8,bgtI9,bgtI10,braI2,braI3,braI4,braI5,braI6,

loadI2,loadI3,loadI4,loadI5,loadI6,inc2,inc3,inc4);

subtypebit16isstd_logic_vector(15downto0);

endcpu_lib;

二、基本部件的设计

1)运算器的设计

功能

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

usework.cpu_lib.all;

entityaluis

port(a,b:

inbit16;sel:

int_alu;c:

outbit16);

endalu;

architecturert1ofaluis

begin

process(a,b,sel)

begin

caseselis

whenalupass=>c<=aafter1ns;

whenandop=>c<=aandbafter1ns;

whenorop=>c<=aorbafter1ns;

.'

.

whenxorop=>c<=axorbafter1ns;

after1ns;whennotop=>c<=nota

whenplus=>c<=a+bafter1ns;

whenalusub=>c<=a-bafter1ns;

wheninc=>c<=a+

whendec=>c<=a-

whenzero=>c<=

whenothers=>c<=

endcase;

endprocess;

endrt1;

2)比较器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

usework.cpu_lib.all;

entitycompis

port(a,b:

inbit16;sel:

int_comp;compout:

outbit);

.'

.

endcomp;

architecturert1ofcompis

begin

process(a,b,sel)

begin

caseselis

wheneq=>ifa=bthencompout<='1'after1ns;

elsecompout<='0'after1ns;

endif;

whenneq=>ifa/=bthencompout<='1'after1ns;

elsecompout<='0'after1ns;

endif;

whengt=>ifa>bthencompout<='1'after1ns;

elsecompout<='0'after1ns;

endif;

whengte=>ifa>=bthencompout<='1'after1ns;

elsecompout<='0'after1ns;

endif;

whenlt=>ifaelsecompout<='0'after1ns;

endif;

whenlte=>ifa<=bthencompout<='1'after1ns;

elsecompout<='0'after1ns;

endif;

whenothers=>compout<='0'after1ns;

endcase;

endprocess;

endrt1;

3)移位寄存器

.'

.

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

usework.cpu_lib.all;

entityshiftis

port(a:

inbit16;sel:

int_shift;y:

outbit16);

endshift;

architecturert1ofshiftis

begin

process(a,sel)

begin

caseselis

whensh=>y<=aafter1ns;

whensftl=>y<=a(14downto0)&'0'after1ns;

whensftr=>y<='0'&a(15downto1)after1ns;

whenrotl=>y<=a(14downto0)&a(15)after1ns;

whenrotr=>y<=a(0)&a(15downto1)after1ns;

whenothers=>y<=

endcase;

endprocess;

endrt1;

4)寄存器

libraryieee;

useieee.std_logic_1164.all;

usework.cpu_lib.all;

entityregis

port(a:

inbit16;clk:

instd_logic;q:

outbit16);

endreg;

architecturert1ofregis

begin

.'

.

process

begin

waituntilclk'eventandclk='1';

q<=aafter1ns;

endprocess;

endrt1;

5)寄存器组

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

usework.cpu_lib.all;

entityregarrayis

port(data:

inbit16;sel:

int_reg;en,clk:

instd_logic;q:

outbit16);

endregarray;

architecturert1ofregarrayis

typet_ramisarray(0to7)ofbit16;

signaltemp_data:

bit16;

begin

process(clk,sel)

variableramdata:

t_ram;

begin

ifclk'eventandclk='1'thenramdata(conv_integer(sel)):

=data;

endif;

temp_data<=ramdata(conv_integer(sel))after1ns;

endprocess;

process(en,temp_data)

begin

ifen='1'thenq<=temp_dataafter1ns;

elseq<=ZZZZZZZZZZZZZZZZafter1ns;

endif;

.'

.

endprocess;

endrt1;

6)三态寄存器

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

usework.cpu_lib.all;

entitytriregis

port(a:

inbit16;en,clk:

instd_logic;q:

outbit16);

endtrireg;

architecturert1oftriregis

signalval:

bit16;

begin

process

begin

waituntilclk'eventandclk='1';

val<=a;

endprocess;

process(en,val)

begin

ifen='1'thenq<=valafter1ns;

elsifen='0'thenq<=ZZZZZZZZZZZZZZZZafter1ns;

elseq<=XXXXXXXXXXXXXXXXafter1ns;

endif;

endprocess;

endrt1;

.'

.

7)控制器

采用状态机实现

libraryIEEE;

useIEEE.std_logic_1164.all;

usework.cpu_lib.all;

entitycontrolis

port(clock,reset,compout:

instd_logic;instrReg:

inbit16;

progCntrWr,progCntrRd,addrRegWr,outRegWr,outRegRd:

outstd_logic;

shiftSel:

outt_shift;aluSel:

outt_alu;compSel:

outt_comp;

opRegRd,opRegWr,instrWr,regRd,regWr,rw,vma:

outstd_logic;

regSel:

outt_reg);

endcontrol;

architecturertlofcontrolis

signalcurrent_state,next_state:

state;

begin

process(current_state,instrReg,compout)

begin

progCntrWr<='0';progCntrRd<='0';addrRegWr<='0';

outRegWr<='0';

.'

.

outRegRd<='0';shiftSel<=sh;aluSel<=alupass;

compSel<=eq;

opRegRd<='0';opRegWr<='0';instrWr<='0';regSel<=

regRd<='0';regWr<='0';rw<='0';vma<='0';

casecurrent_stateis

whenreset1=>aluSel<=zeroafter1ns;shiftSel<=sh;next_state<=reset2;

whenreset2=>aluSel<=zero;shiftSel<=sh;outRegWr<='1';next_state<=reset3;

whenreset3=>outRegRd<='1';next_state<=reset4;

whenreset4=>outRegRd<='1';progCntrWr<='1';addrRegWr<='1';next_state<=reset5;

whenreset5=>vma<='1';rw<='0';next_state<=reset6;

whenreset6=>vma<='1';rw<='0';instrWr<='1';next_state<=execute;

whenexecute=>caseinstrReg(15downto11)is

when

when

when

whenぜ?

?

?

=>regSel<=instrReg(5downto3);regRd<='1';

aluSel<=alupass;shiftSel<=sh;next_state<=move2;

when00=>progcntrRd<='1';alusel<=inc;shiftsel<=sh<=loadI2;

when01=>progcntrRd<='1';alusel<=inc;shiftsel<=sh<=braI2;

3);

downtowhen10=>regSel<=instrReg(5

regRd<='1';next_state<=bgtI2;--BranchGTImm

when11=>regSel<=instrReg(2downto0);regRd<='1';alusel<=inc;

shiftsel<=sh;next_state<=inc2;

whenothers=>next_state<=incPc;

endcase;

whenload2=>regSel<=instrReg(5downto3);regRd<='1';addrregWr<='1';

next_state<=load3;

whenload3=>vma<='1';rw<='0';next_state<=load4;

whenload4=>vma<='1';rw<='0';regSel<=instrReg(2downto0);regWr<='1';

next_state<=incPc;

whenstore2=>regSel<=instrReg(2downto0);regRd<='1';addrregWr<='1';

next_state<=store3;

whenstore3=>regSel<=instrReg(5downto3);regRd<='1';next_state<=store4;

whenstore4=>regSel<=instrReg(5downto3);regRd<='1';rw<='1';next_state<=incPc;

whenmove2=>regSel<=instrReg(5downto3);regRd<='1';aluSel<=alupass;

shiftsel<=sh;outRegWr<='1';next_state<=move3;

whenmove3=>outRegRd<='1';next_state<=move4;

whenmove4=>outRegRd<='1';regSel<=instrReg(2downto0);regWr<='1';

.'

.

next_state<=incPc;

whenloadI2=>progcntrRd<='1';alusel<=inc;shiftsel<=sh<='1';

next_state<=loadI3;

whenloadI3=>outregRd<='1';next_state<=loadI4;

whenloadI4=>outregRd<='1';progcntrWr<='1';addrregWr<='1';next_state<=loadI5;

whenloadI5=>vma<='1';rw<='0';next_state<=loadI6;

whenloadI6=>vma<='1';rw<='0';regSel<=instrReg(2downto0);regWr<='1';

next_state<=incPc;

whenbraI2=>progcntrRd<='1';alusel<=inc;shiftsel<=sh<='1';

next_state<=braI3;

whenbraI3=>outregRd<='1';next_state<=braI4;

whenbraI4=>outregRd<='1