阶段性考核之一组合逻辑电路设计实验.docx

《阶段性考核之一组合逻辑电路设计实验.docx》由会员分享,可在线阅读,更多相关《阶段性考核之一组合逻辑电路设计实验.docx(9页珍藏版)》请在冰豆网上搜索。

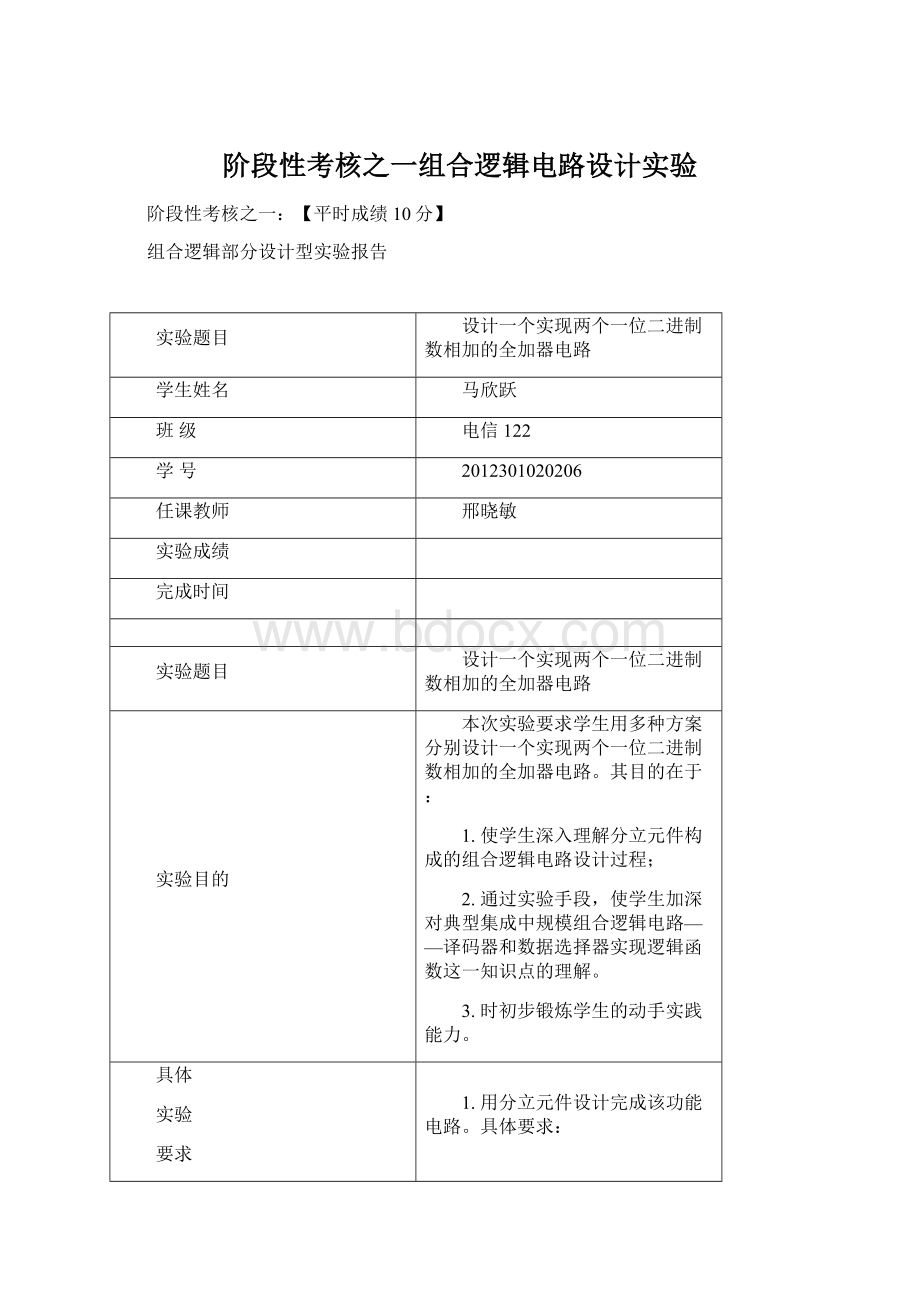

阶段性考核之一组合逻辑电路设计实验

阶段性考核之一:

【平时成绩10分】

组合逻辑部分设计型实验报告

实验题目

设计一个实现两个一位二进制数相加的全加器电路

学生姓名

马欣跃

班级

电信122

学号

2012301020206

任课教师

邢晓敏

实验成绩

完成时间

实验题目

设计一个实现两个一位二进制数相加的全加器电路

实验目的

本次实验要求学生用多种方案分别设计一个实现两个一位二进制数相加的全加器电路。

其目的在于:

1.使学生深入理解分立元件构成的组合逻辑电路设计过程;

2.通过实验手段,使学生加深对典型集成中规模组合逻辑电路——译码器和数据选择器实现逻辑函数这一知识点的理解。

3.时初步锻炼学生的动手实践能力。

具体

实验

要求

1.用分立元件设计完成该功能电路。

具体要求:

(1)试用2输入与非门芯片实现该电路;【要求指明所需芯片型号、功能和具体数量】

(2)试用最少个数的芯片实现该电路。

【要求指明所需芯片型号、功能和具体数量】

(3)以上两方案只需用Multisim仿真软件仿真实现即可,无需到实验室进行实物搭接。

但在该实验报告中要求必须有完整的设计过程和仿真电路图。

2.用3线-8线译码器7LS138设计完成该功能电路。

【要求指明所需芯片型号、功能和具体数量】

3.用双4选1数据选择器74LS153设计完成该功能电路。

【要求指明所需芯片型号、功能和具体数量】

4.以上1、2、3规定的实现方案要求都要用数码管来显示十进制的计算结果。

5.上述2、3两种方案的实现既要有Multisim仿真实验过程,又要求到实验室进行实物搭接。

在该实验报告中要有完整的设计过程、仿真电路图和实验调试过程。

6.总结本次实验的收获、体会以及建议,填入本实验报告的相应位置中。

【收获、体会必须写!

】

设计过程

一.用分立元件设计完成两个一位二进制数全加器

方案一:

用2输入与非门实现

1.设计过程:

全加器真值表

Ai

Bi

Ci-1

Si

Ci

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

写出全加器逻辑函数表达式,并转化成与非-与非式

画出电路图

2.所用器件:

2输入与非门7401九个实现与非功能

数码管译码器7448一个用于驱动数码管

共阴极数码管一个用于显示结果

3.仿真实现过程:

ABC三个开关控制输入0或1,当1个开关闭合时,数码管显示数字1;当2个开关闭合时,数码管显示2;当3个开关闭合时显示3。

开始没有注意到7448要搭配共阴极数码管,用了7447驱动,结果不显示数字,后改为7448,正常显示结果。

方案二:

用最少个数的芯片实现

1.设计过程:

写出全加器的逻辑表达式

化成最简式形式

根据表达式设计电路图。

2.所用器件:

二输入异或门7486两个

二输入与门7408两个

二输入或门7432一个

数码管译码器7448一个用于驱动数码管

共阴极数码管一个用于显示结果

3.仿真实现过程:

按照电路图连接ABC三个开关控制输入0或1,当1个开关闭合时,数码管显示数字1;当2个开关闭合时,数码管显示2;当3个开关闭合时显示3。

二.用3线-8线译码器7LS138设计完成该功能电路【方案三】

1.设计过程:

3线-8线译码器74LS138真值表

输入

输出

G1

G2A

G2B

C

B

A

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

X

1

X

X

X

X

1

1

1

1

1

1

1

1

X

X

1

X

X

X

1

1

1

1

1

1

1

1

0

X

X

X

X

X

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

0

1

1

1

1

1

1

1

0

0

0

1

0

1

1

0

1

1

1

1

1

1

0

0

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

0

0

1

1

1

1

0

1

1

1

1

0

0

1

0

1

1

1

1

1

1

0

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

1

1

0

0

1

1

1

1

1

1

1

1

1

1

0

根据全加器真值表写出函数表达式,并化为最小项之和形式

根据74LS138译码器实现要求转化成下面形式。

2.所用器件:

74LS138译码器一个

7420双4输入与非门两个

数码管译码器7448一个用于驱动数码管

共阴极数码管一个用于显示结果

3.仿真实现过程:

S1,S2,S2分别控制ABC的输入信号,将ABC分别接在71LS138的ABC输入端上,输出端Y1Y2Y4Y7进行与非运算后得到S,输出端Y3Y5Y6Y7与非之后得到CO,当1个开关闭合时,数码管显示数字1;当2个开关闭合时,数码管显示2;当3个开关闭合时显示3。

三.用双4选1数据选择器74LS153设计完成该功能电路【方案四】

1.设计过程:

双4选1数据选择器74LS153真值表

使能端

选择控制端

输出

_____EN

A

B

Y

1

X

X

0

0

0

0

C0

0

0

1

C1

0

1

0

C2

0

1

1

C3

逻辑表达式:

根据全加器真值表,可写出和S,高位进位CO的逻辑函数。

两个输入变量,A、B,D0~D3为第三个输入变量,即低位进位CI,1Y为全加器的和S,2Y全加器的高位进位CO,则可令数据选择器的输入为:

1DO=1D3=CI,1D1=1D2=CI,2D0=0,2D3=1,2D1=2D2=CI,1Y=S,2Y=CO;

2.所用器件:

双4选1数据选择器74LS153一个

7404反相器一个

3.仿真实现过程:

S1,S2,S2分别控制CAB的输入信号,AB分别连接在AB输入端上,1C1,1C2连在非门之后1C0,1C3,2C1,2C2连在非门之前,由S1控制实现信号的输入和输出,2C0接地,2C3接高电平,使能端接地。

将S(1Y)接在数码管的低位,CO(2Y)接在数码管的高位,实现信号的输入和输出。

当1个开关闭合时,数码管显示数字1;当2个开关闭合时,数码管显示2;当3个开关闭合时显示3。

实验心得

通过这次实验我懂得了当我们上课坐在那里听课和我们真正动手去做事完全不一样的。

上课时看老师在黑板上讲课画仿真时没觉得自己有这么多问题存在,当真正动手做时才发现自己有很多问题。

出现这些问题有些时因为粗心大意,有些时上课听课没认真注意老师说的一些话,有些是因为没有实践过太生疏导致的。

在做仿真时,我没有注意到7448是与共阴极数码管相配的,粗心的用了7447译码器与共阴极数码管,导致我做了很多遍就是没有结果显示。

后来通过问同学,我找出了原因改正了仿真。

所以,同学之间合作也是重要的。

大家在一起讨论过后可能就会明白很多。

自己没有注意到的问题其他同学有注意到就可以互相学习一下。

还有在搭电路时千万不可以粗心,出现错误一定要细心检查,看看是哪里错了,仔细整理思路,是不是连接出了问题,还是导线有损坏,或者是芯片不能正常工作。

所以当出现问题时,一定要有耐心不能急躁,仔细分析。

实践才能检验我们所学的理论,发现我们存在的问题。

所以我们要重视实践,重视同学间的合作。

附录1:

方案一仿真电路图

附录2:

方案二仿真电路图

附录3:

方案三仿真电路图

附录4:

方案四仿真电路图