义隆单片机EM78P153使用讲解.docx

《义隆单片机EM78P153使用讲解.docx》由会员分享,可在线阅读,更多相关《义隆单片机EM78P153使用讲解.docx(78页珍藏版)》请在冰豆网上搜索。

义隆单片机EM78P153使用讲解

基于EM78P153S的应用设计

(V1.0)

第一章EM78P153S的初识

EM78P152/3S是采用低功耗高速CMOS工艺设计开发的8位微控制器,它的内部有一个1024×13位一次性可编程只读存储器(OTP_ROM),可见1k的只读存储器(ROM)决定了应用程序不能够太多,否则应用程序机器码将无法烧录到芯片中。

硬件设计中,EM78P152/3S可以通过设置代码选项寄存器使微处理器工作在内部RC振荡模式(IRC)下,此模式下采用上电复位模式而不需要外接时钟电路;同时利用上电自动复位而不需要外接复位电路,P63复位引脚可以直接作为输入脚使用,充分提高了微处理器端口的利用率,这样硬件应用电路极为简化,节省了硬件成本。

此外,EM78P153S单片机具有休眠模式,在一些不需要微处理器实时工作的应用场合,可以节省用电量,特别是在使用电池供电时,应用此模式可以延长电池的使用时间;另外在休眠模式下避免了微处理器在运行时受到来自外在杂波信号的干扰而导致程序跑飞。

1.1EM78P152/3S特性

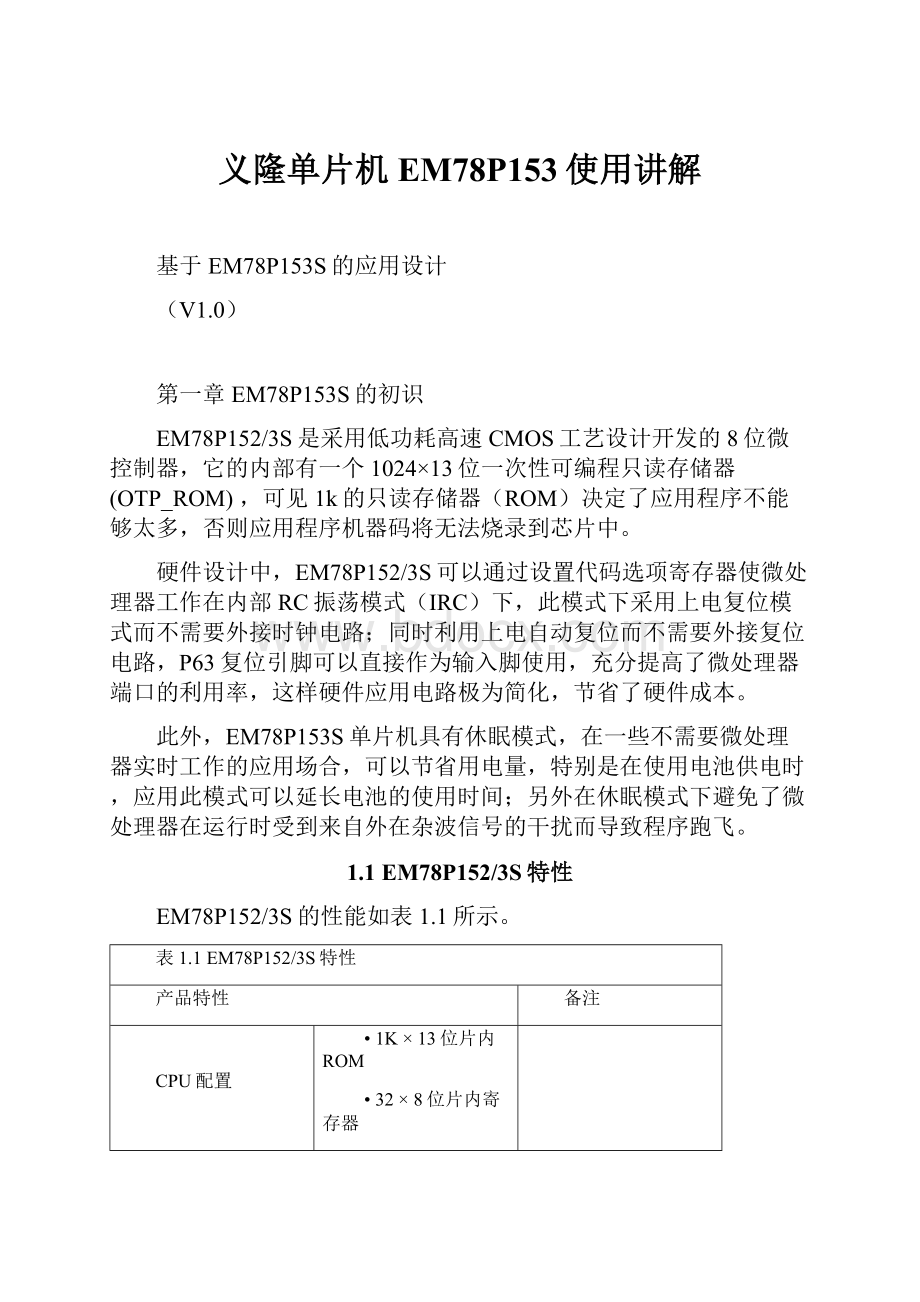

EM78P152/3S的性能如表1.1所示。

表1.1EM78P152/3S特性

产品特性

备注

CPU配置

•1K×13位片内ROM

•32×8位片内寄存器

•5级堆栈用于子程序嵌套

•小于1.5mA@5V/4MHz

•休眠模式下的典型值为1µA。

I/O端口配置

•2组双向I/O端口:

P5,P6

•11个I/O引脚

•唤醒端口:

P6

•6个可编程下拉I/O引脚

•7个可编程上拉I/O引脚

•7个可编程漏极开路I/O引脚

•外部中断:

P60

工作电压范围

•OTP版本;工作电压范围:

2.3V~5.5V

工作频率范围

•IRC模式;振荡模式:

4MHz,8MHz,1MHz,455KHz

外设配置

•8位实时时钟/计数器,可编程选择其信号源、触发边沿,溢出产生中断

三种中断源

•TCC溢出中断

•输入端口状态改变中断(可使微控制器从休眠模式唤醒)

•外部中断

专有特性

•省电模式(休眠模式)

•可选振荡模式

封装类型

•14引脚DIP:

EM78P153SP/S/J

•14引脚SOP:

EM78P153SN/S/J

•10引脚SSOP:

EM78P152SN/S/J

其它

•具备一个保护寄存器以防止OTP_ROM中的程序代码被窃取

1.2EM78P152/3S引脚

EM78P152/3S的引脚图如图1.1,引脚功能如表1.2所示。

图1.1EM78P152/3S引脚图

EM78P153SP/N/S/J

EM78P152SP/N/S/J

表1.2EM78P152/3S引脚功能表

引脚名称

序号

类型

功能

备注

P50~P53

1、12、13、14

I/O

*通用的I/O引脚

P60~P62

P64~P67

2、3、5

6、8、9、10

I/O

*通用的I/O引脚

*引脚状态发生改变时,从休眠模式唤醒

*可以设置为上拉

P60/INT

10

I/O

*下降沿触发的外部中断引脚

P62/TCC

8

I/O

*外部定时/计数器信号输入引脚

P63/RESET

7

I

*若设置/RESET引脚并使其保持逻辑低,器件将产生复位

*引脚状态改变时,从休眠模式唤醒

*P63仅用作输入引脚

P64、P65

5、6

I/O

*外部时钟信号输入

*晶体振荡器的输入引脚

VDD

4

—

*电源正极

VSS

11

—

*电源地

1.3功能寄存器

期望微处理器按预期的性能工作,就需要对功能寄存器进行有效的定义,这也是汇编编程初始化的基本任务。

针对EM78P153单片机,在汇编程序编写中,使用频率相对较高的寄存器有累加器A、I/O端口控制寄存器IOC5~IOC6、中断状态寄存器(RF)、中断使能寄存器(IOCF)。

1.3.1累加器与端口控制寄存器

[示例1]端口数值的传送(读取一个端口的值送给另一个端口)。

源程序如下:

;*****************************************************

;DIP输入,LED输出

;*****************************************************

dip==5;定义dip输入端口的地址为5

led==6;定义显示端口的地址为6

org0x00;定义程序存放区的起始地址

jmpmain;跳转到主程序

org0x50;声明主程序开始地址

main:

mova,@0x00;

iowled;设定显示端口引脚全部输出

mova,@0xff;

iowdip;设定dip端口全部为输入

loop

comadip;读取dip状态并取反送a

movled,a;传送到端口6上面显示

jmploop;循环回去

;*****************************************************

end;告知汇编器源程序结束

1、累加器A

累加器A用于内部数据传送或指令操作数暂存,它不可被寻址。

寄存器之间的数据传递需要通过累加器A来过渡,即寄存器先传送给A再由A传送给另一个寄存器。

2、I/O端口控制寄存器IOC5~IOC6

I/O端口控制寄存器IOC5~IOC6:

为“1”时,相关I/O引脚置为高阻态(输入);为“0”时,相关I/O引脚置为输出。

IOC5寄存器仅低4位可被有效定义,IOC5和IOC6均为可读/写寄存器。

1.3.2中断状态寄存器与中断使能寄存器

[示例2]將寄存器0x20当做计数器,每当外部中断产生,就自动加1。

源程序如下:

;*****************************************************

;P60/INT外部中断

;將寄存器0x20当做计数器,每当外部中断产生,就自动加1

;*****************************************************

ORG0x00;定义程序存放区的起始地址

CLR0x20;清除计数器

JMPEXT_PRO;跳转到主程序

ORG0x08;中断的入口地址

INT_EXT:

DISI;使能中断

CLR0x0F;清除中断状态寄存器的标志位

INC0x20;计数器加1

RETI;返回主程序

ORG0x50;主程序的开始地址

EXT_PRO:

CLR0x0F;清除标志位

MOVA,@0x04;使能外部中断信号产生

IOW0x0F;把A的内容送给0x0F

MOVA,@0x40;定义P60为外部中断引脚

IOW0x0E

ENI;开总中断

EXT_WAIT:

NOP

NOP

JMPEXT_WAIT;循环等待外部中断

;*****************************************************

END;汇编器源程序结束

1、中断状态寄存器(RF)

中断状态寄存器(RF)地址0x0F,它反映三种中断标志情形,硬件自动置1,均需要通过软件的方式清0,以清除中断标志。

RF各位的含义如表1.3所示。

表1.3中断状态寄存器RF

地址

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

0x0F

—

—

—

—

—

EXIF

ICIF

TCIF

其中:

Bit2(EXIF):

外部中断标志位,/INT管脚输入下降沿时置“1”,由软件清“0”;

Bit1(ICIF):

端口6输入状态改变标志位,输入状态改变时置“1”,由软件清“0”;

Bit0(TCIF):

TCC溢出中断标志位,TCC溢出时置“1”,由软件清“0”。

2、中断使能寄存器(IOCF)

中断使能寄存器(IOCF)地址0x0F,与中断状态寄存器共用一个地址,它反映三种中断的开启与关闭,在程序运行每个指令周期中,硬件自身判断中断使能位,当中断使能位为1时响应相应中断,同时在中断服务程序中务必清中断状态寄存器的相应标志位为0。

IOCF各位的含义如表1.4所示。

表1.4中断使能寄存器

地址

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

0x0F

—

—

—

—

—

EXIE

ICIE

TCIE

功能

0:

禁止EXIF中断

1:

使能EXIF中断

0:

禁止ICIF中断

1:

使能ICIF中断

0:

禁止TCIF中断

1:

使能TCIF中断

其中:

Bit2(EXIE)是外部中断EXIF使能位;Bit1(ICIE)是端口6输入状态改变引发中断ICIF使能位;Bit0(TCIE)是定时溢出中断TCIF使能位。

1.3.3操作寄存器

1、间接寻址寄存器R0

R0并非实际存在的寄存器,它的主要功能是作为间接寻址指针,任何以R0为指针的指令,实际上是对RAM选择寄存器R4所指向地址的数据内容进行操作。

2、定时/计数器R1

(1)TCC引脚的外部信号边沿或内部指令周期时钟触发(由CONT寄存器的TE位设定),会使TCC寄存器加1;

(2)像其它寄存器一样可读/写;

(3)通过复位PAB位(CONT-3)设定;

(4)如果PABbit(CONT-3)被复位,预分频器分配给TCC;

(5)写入一个值到TCC寄存器后,TCC计数器的内容会被刷新。

3、程序计数器R2&堆栈

复位时,程序计数器R2所有位均清0,它提供了程序指令代码的片内OTP_ROM地址。

一个程序页为1024字长。

在程序编译调试时,可以通过查看R2的值,判断程序是否跳转正常,或者通过对比某个程序的入口判断是否进入某个函数。

“JMP”指令直接加载程序计数器的低10位,因此,“JMP”允许PC跳转到一个程序页的任何位置。

“CALL”指令首先加载PC的低10位,然后将PC+1推入堆栈,因此,子程序的入口地址可位于一个程序页的任何位置。

正常情况下,所有指令均是单指令周期(一个指令周期包含2个振荡周期),但改变程序计数器(R2寄存器)内容的指令,均为2个指令周期。

EM78P153S有五级堆栈,这就决定了在程序编写的时候,子程序的嵌套调用不能够超过5次,否则编译会出错。

4、状态寄存器R3

(程序)状态寄存器R3的地址为0x03,如表1.5所示。

表1.5状态寄存器R3

地址

0x03

BIT7

RST

0代表其它复位类型引发唤醒复位方式;1代表引脚状态改变引发控制器从休眠模式唤醒方式

BIT6

GP1

通用读/写位

BIT5

GP0

BIT4

T

时间溢出标志位,执行“SLEP”和“WDTC”指令或上电时置“1”,WDT溢出时复位为“0”

BIT3

P

省电标志位,上电或执行"WDTC"指令时置“1”,执行“SLEP”指令时复位为“0”

BIT2

Z

零标志位,当算术或逻辑运算的结果为0时置“1”

BIT1

DC

辅助进位标志位

BIT0

C

进位标志位

在程序编译调试时,可以通过查看R3的值,了解程序的工作过程。

5、RAM选择寄存器R4:

I/O寄存器,仅低4位可用。

6、端口5寄存器R5:

I/O寄存器,引脚都为I/O口。

7、端口6寄存器R6:

I/O寄存器,除P63仅用作输入引脚外,其它引脚都为I/O口。

8、R10—R2F:

所有这些寄存器均为8位通用寄存器。

表1.6控制寄存器CONT

BIT7

—

BIT6

INT

中断使能标志位:

0代表被DISI或硬件中断屏蔽;1代表被ENI/RETI指令使能

BIT5

TS

TCC信号源选择位:

0代表内部指令周期时钟,P62为双向I/O引脚;1代表TCC引脚的跳变信号

BIT4

TE

TCC信号边沿选择位:

0代表TCC引脚信号由低变到高时TCC计数器加1;1代表TCC引脚信号由高变到低时TCC计数器加1

BIT3

PAB

预分频器分配位:

0代表TCC;1代表WDT

BIT2

PSR2

TCC/WDT预分频比选择位

PSR2

0

0

0

0

1

1

1

1

BIT1

PSR1

PSR1

0

0

1

1

0

0

1

1

PSR0

0

1

0

1

0

1

0

1

BIT0

PSR0

TCC预分频比

1:

2

1:

4

1:

8

1:

16

1:

32

1:

64

1:

128

1:

256

WDT预分频比

1:

1

1:

2

1:

4

1:

8

1:

16

1:

32

1:

64

1:

128

1.3.4特殊功能寄存器

1、控制寄存器CONT

控制寄存器CONT各位定义如表1.6所示。

2、下拉控制寄存器IOCB、漏极开路控制寄存器IOCC、上拉控制寄存器IOCD

下拉控制寄存器IOCB各位定义如表1.7所示。

表1.7下拉控制寄存器IOCB

BIT7

—

BIT6

/PD6

P62引脚下拉功能使能控制位;0代表使能内部下拉功能;1代表禁止内部下拉功能

BIT5

/PD5

P61引脚下拉功能使能控制位;0代表使能内部下拉功能;1代表禁止内部下拉功能

BIT4

/PD4

P60引脚下拉功能使能控制位;0代表使能内部下拉功能;1代表禁止内部下拉功能

BIT3

—

BIT2

/PD2

P52引脚下拉功能使能控制位;0代表使能内部下拉功能;1代表禁止内部下拉功能

BIT1

/PD1

P51引脚下拉功能使能控制位;0代表使能内部下拉功能;1代表禁止内部下拉功能

BIT0

/PD0

P50引脚下拉功能使能控制位;0代表使能内部下拉功能;1代表禁止内部下拉功能

漏极开路控制寄存器IOCC各位定义如表1.8所示。

表1.8漏极开路控制寄存器IOCC

BIT7

OD7

P67引脚漏极开路功能使能控制位;0代表禁止漏极开路输出;1代表使能漏极开路输出

BIT6

OD6

P66引脚漏极开路功能使能控制位;0代表禁止漏极开路输出;1代表使能漏极开路输出

BIT5

OD5

P65引脚漏极开路功能使能控制位;0代表禁止漏极开路输出;1代表使能漏极开路输出

BIT4

OD4

P64引脚漏极开路功能使能控制位;0代表禁止漏极开路输出;1代表使能漏极开路输出

BIT3

—

BIT2

OD2

P62引脚漏极开路功能使能控制位;0代表禁止漏极开路输出;1代表使能漏极开路输出

BIT1

OD1

P61引脚漏极开路功能使能控制位;0代表禁止漏极开路输出;1代表使能漏极开路输出

BIT0

OD0

P60引脚漏极开路功能使能控制位;0代表禁止漏极开路输出;1代表使能漏极开路输出

上拉控制寄存器IOCD各位定义如表1.9所示。

表1.9上拉控制寄存器IOCD

BIT7

/PH7

P67引脚上拉功能使能控制位;0代表使能内部上拉功能;1代表禁止内部上拉功能

BIT6

/PH6

P66引脚上拉功能使能控制位;0代表使能内部上拉功能;1代表禁止内部上拉功能

BIT5

/PH5

P65引脚上拉功能使能控制位;0代表使能内部上拉功能;1代表禁止内部上拉功能

BIT4

/PH4

P64引脚上拉功能使能控制位;0代表使能内部上拉功能;1代表禁止内部上拉功能

BIT3

—

BIT2

/PH2

P62引脚上拉功能使能控制位;0代表使能内部上拉功能;1代表禁止内部上拉功能

BIT1

/PH1

P61引脚上拉功能使能控制位;0代表使能内部上拉功能;1代表禁止内部上拉功能

BIT0

/PH0

P60引脚上拉功能使能控制位;0代表使能内部上拉功能;1代表禁止内部上拉功能

通过操作IOCB、IOCC、IOCD寄存器可以设置端口的输入输出方式。

当某端口作为输入口使用时,只需要考虑是否上拉或者下拉;当某端口作为输出口使用时,则考虑是否开漏极输出。

端口采用内部上拉,可以减少外部对引脚电平的干扰,如果要实现检测某端口是否为低电平的功能,则必须设置为内部上拉,若该端口没有上拉功能,则需要外部加上拉电阻。

端口采用内部下拉,理论上可以减少外部对引脚电平的干扰,但是实际的测试效果不明显,和没有设置下拉的效果一样。

所以如果端口设置为内部下拉,该端口只可以用于检测高电平,但是在没有输入的情况下,该引脚的电平并没有变为1V以下,不能看作真正的低电平。

端口采用内部开漏极输出,适用于微处理器工作电压与外围器件工作电压不相同的场合,输出的高电平将达不到VDD电压值。

5、看门狗定时器控制寄存器IOCE

看门狗定时器控制寄存器IOCE各位定义如表1.10所示。

表1.10看门狗定时器控制寄存器IOCE

地址

BIT7

WDTE

看门狗定时器使能控制位:

0代表禁止WDT;1代表使能WDT

BIT6

EIS

定义P60(/INT)引脚功能的控制位:

0定义P60为双向I/O引脚;1定义为外部中断输入引脚/INT,在此情况下,P60引脚的I/O控制位(IOC6的bit0)必须置为“1”

BIT5—0

—

1.4数据存储器的配置

通过了解数据存储器的分布,可以在仿真时直接了解各个寄存器的状态以及程序运行情况,数据存储器的配置如表1.11所示。

表1.11数据存储器配置

地址

RPAGE寄存器

IOCPAGE寄存器

00

R0

间接寻址寄存器

保留

01

R1

定时/计数器

CONT

控制寄存器

02

R2

程序计数器

保留

03

R3

状态寄存器

保留

04

R4

RAM选择寄存器

保留

05

R5

Port5

IOC5

I/O端口控制寄存器

06

R6

Port6

IOC6

I/O端口控制寄存器

07

保留

保留

08

保留

保留

09

保留

保留

0A

保留

保留

0B

保留

IOCB

下拉控制寄存器

0C

保留

IOCC

漏极开路控制寄存器

0D

保留

IOCD

上拉控制寄存器

0E

保留

IOCE

看门狗定时器控制寄存器

0F

RF

中断状态寄存器

IOCF

中断屏蔽寄存器

10—2F

通用寄存器

无

1.5休眠与唤醒

EM78P152/3S微处理器可以在程序中执行SLEP指令将进入休眠模式,微处理器可以由以下事件唤醒:

(1)/RESET引脚的外部复位信号输入;

(2)WDT溢出(若使能);

(3)Port6输入状态改变(若使能);

“/RESET引脚的外部复位信号输入”以及“WDT溢出”都将使EM78P152/3S复位,可用R3寄存器的T和P标志位来判断复位源(唤醒源)。

由于采用上电复位的方式,P63脚将作为输入脚使用,而不用作复位脚,所以不存在复位脚;另外若WDT的使用频率不高,可以设置为不使能(附:

实际中可以不采取这两种唤醒模式)。

实际中更多考虑的则是“Port6输入状态改变”的唤醒模式。

“Port6输入状态改变”将综合考虑后续程序的执行和全局中断(“ENI”或“DISI”指令的执行情况),来决定控制器在唤醒后是否进入中断向量。

如果在SLEP指令前执行了ENI指令,唤醒后将从地址为008H处开始执行。

如果在SLEP指令前执行了DISI指令,唤醒后将从SLEP指令的下一条指令开始执行。

在SLEP指令之前Port6输入状态的改变中断要使能,即中断使能寄存器(IOCF)中ICIE位要置“1”,同时必须通过软件编程禁止WDT,但代码选项寄存器(CodeOption)的WDT位仍要保持使能。

代码选项寄存器将在介绍烧录程序的章节详细介绍。

休眠与管脚唤醒的使用步骤:

(1)唤醒端口设置为输入口;

(2)使能唤醒端口内部上拉;

(3)设置WDT分频比大于1:

1,并禁止WDT;

(4)清TCC;

(5)读PORT6状态,即下“MOVPORT6,PORT6”指令;

(6)使能唤醒功能设置ICIE位为“1”;

(7)如需要中断则使能总中断下“ENI”指令;

(8)下“SLEP”指令;

(9)加三条“NOP”指令延时;

(10)下“WDTC”指令;

(11)禁止WDT;

(12)禁止管脚唤醒功能;

在编程的时候,要注意执行SLEP指令之前,要按照上述步骤编写,在SLEP指令后面要加上三条“NOP”指令,这个不能够缺少。

在休眠模式下,若WDT已使能,WDT也将被清零,但WDT会继续保持运行状态。

在唤醒后,要间隔10ms左右就要执行一次“WDTC”指令,防止WDT溢出引起复位。

此处设置预分频的比例要大于1:

1也是为防止WDT溢出引起复位。

1.6分频器

看门狗定时器WDT与TCC共用一个分频器,但某一时刻分频器只能够分配给二者之一。

与TCC配合使用时,它是以一个“预”分频器的角色出现在TCC的输入信号路径中的;而与WDT配合使用时,它是以一个“后”分频器的角色出现在WDT的输出信号路径中的。

分频器实际上就是一个8位的累加计数器,不过不能够像TCC那样通过内部数据总线用软件进行读写操作。

分频器的功能就是将进入TCC的时钟信号(或从WDT出来的序列脉冲信号)频率除以一个指定的倍数,这个倍数就是分频比,由CONT寄存器中的PSR2~PSR0位决定。

需要注意的是,当分频器分配给TCC时,任何以TCC为目标的写操作指令(如CLRTCC、MOVTCC,A)都会同时将分频器清零。

同理当分频器分配给WDT时,一条清WDT的指令(WDTC)将会同时将分频器清零。

这里说的只是分频器清零,而分配比和分配的对象不会改变。

看门狗定时器的时钟源是一个自由运行的片内RC振荡器。

即使在其它的振荡器关闭的时候(也就是休眠模式下),WDT仍然保持运行。

在正常模式下或休眠模式下,WDT溢出(若WDT使能)将会使器件产生复位。

在正常模式下,可以通过软件编程为禁止或使能,不使用分频器的时候,WDT的溢出周期约为18ms。

所以通常从休眠模式下唤醒后要间隔一段时间就要加一条清WDT的指令,防止WDT溢出产生复位。

1.7定时器/计数器TCC

与定时器/计数器TCC模块相关的寄存器有4个,分别为R1(TCC寄存器)、RF(中断状态寄存器)、CONT(控制寄存器)、IOCF(中断屏蔽寄存器)。

TCC具有两种工作模式,一种定时器模式,另一种是计数器模式。

两种模式之间的主要差异就是送入累加计数寄存器TCC的“触发信号”的来源不同而已。

TCC的工