服务器硬件架构.docx

《服务器硬件架构.docx》由会员分享,可在线阅读,更多相关《服务器硬件架构.docx(39页珍藏版)》请在冰豆网上搜索。

服务器硬件架构

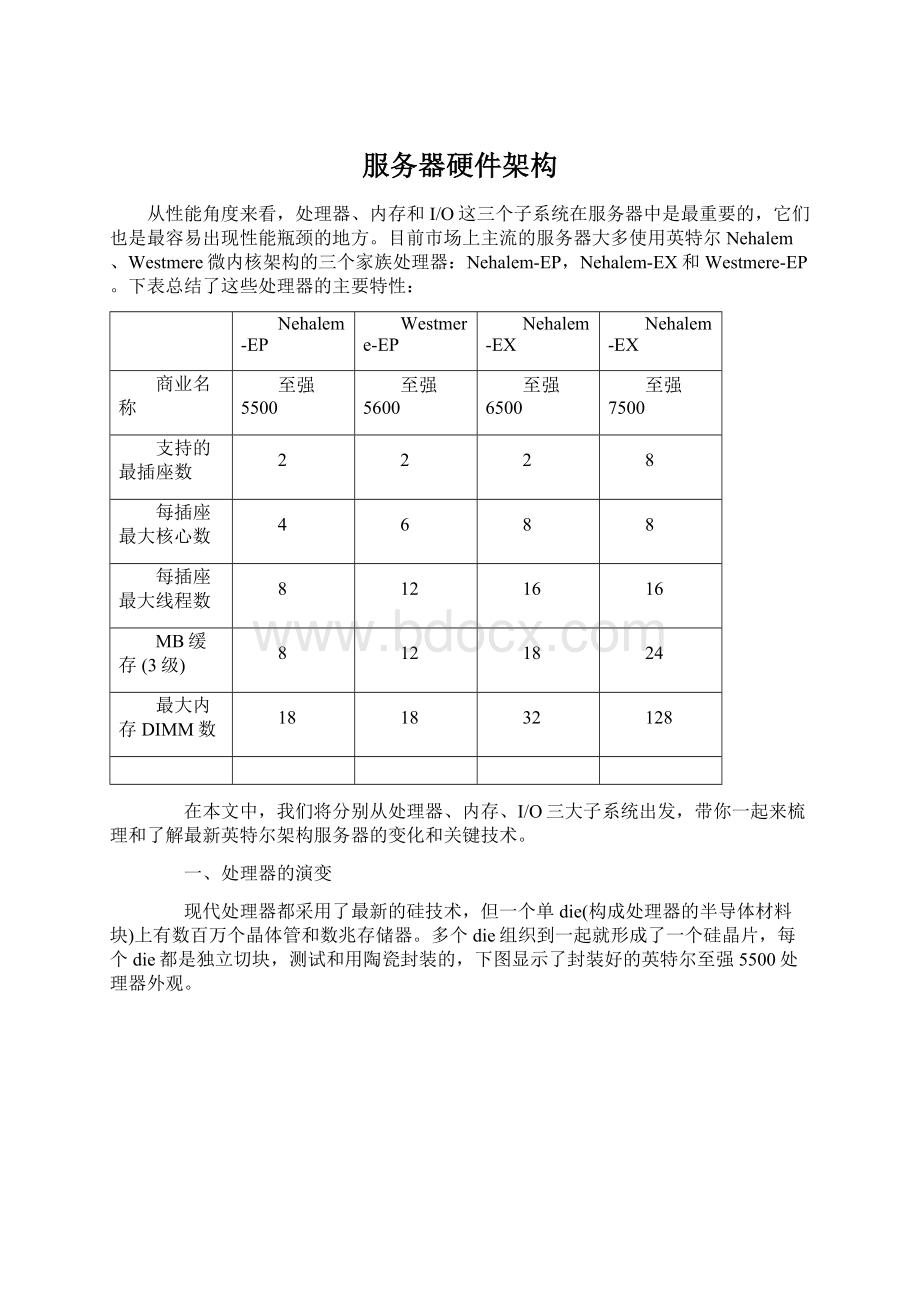

从性能角度来看,处理器、内存和I/O这三个子系统在服务器中是最重要的,它们也是最容易出现性能瓶颈的地方。

目前市场上主流的服务器大多使用英特尔Nehalem、Westmere微内核架构的三个家族处理器:

Nehalem-EP,Nehalem-EX和Westmere-EP。

下表总结了这些处理器的主要特性:

Nehalem-EP

Westmere-EP

Nehalem-EX

Nehalem-EX

商业名称

至强5500

至强5600

至强6500

至强7500

支持的最插座数

2

2

2

8

每插座最大核心数

4

6

8

8

每插座最大线程数

8

12

16

16

MB缓存(3级)

8

12

18

24

最大内存DIMM数

18

18

32

128

在本文中,我们将分别从处理器、内存、I/O三大子系统出发,带你一起来梳理和了解最新英特尔架构服务器的变化和关键技术。

一、处理器的演变

现代处理器都采用了最新的硅技术,但一个单die(构成处理器的半导体材料块)上有数百万个晶体管和数兆存储器。

多个die组织到一起就形成了一个硅晶片,每个die都是独立切块,测试和用陶瓷封装的,下图显示了封装好的英特尔至强5500处理器外观。

图1英特尔至强5500处理器

插座

处理器是通过插座安装到主板上的,下图显示了一个英特尔处理器插座,用户可根据自己的需要,选择不同时钟频率和功耗的处理器安装到主板上。

图2英特尔处理器插座

主板上插座的数量决定了最多可支持的处理器数量,最初,服务器都只有一个处理器插座,但为了提高服务器的性能,市场上已经出现了包含2,4和8个插座的主板。

在处理器体系结构的演变过程中,很长一段时间,性能的改善都与提高时钟频率紧密相关,时钟频率越高,完成一次计算需要的时间越短,因此性能就越好。

随着时钟频率接近4GHz,处理器材料物理性质方面的原因限制了时钟频率的进一步提高,因此必须找出提高性能的替代方法。

核心

晶体管尺寸不断缩小(Nehalem使用45nm技术,Westmere使用32nm技术),允许在单块die上集成更多晶体管,利用这个优势,可在一块die上多次复制最基本的CPU(核心),因此就诞生了多核处理器。

现在市场上多核处理器已经随处可见,每颗处理器包含多个CPU核心(通常是2,4,6,8个),每个核心都有一级缓存(L1),通常所有的核心会共享二级(L2)、三级缓存(L3)、总线接口和外部连接,下图显示了一个双核心的CPU架构。

图3双核心CPU架构示意图

现代服务器通常提供了多个处理器插座,例如,基于英特尔至强5500系列(Nehalem-EP)的服务器通常包含两个插座,每个插座四个核心,总共可容纳八个核心,而基于英特尔至强7500系列(Nehalem-EX)的服务器通常包含八个插座,每个插座八个核心,总共可容纳64个核心。

下图显示了更详细的双核处理器架构示意图,CPU的主要组件(提取指令,解码和执行)都被复制,但系统总线是公用的。

图4双核处理器的详细架构示意图

线程

为了更好地理解多核架构的含义,我们先看一下程序是如何执行的,服务器会运行一个内核(如Linux,Windows的内核)和多个进程,每个进程可进一步细分为线程,线程是分配给核心的最小工作单元,一个线程需要在一个核心上执行,不能进一步分割到多个核心上执行。

下图显示了进程和线程的关系。

图5进程和线程的关系

进程可以是单线程也可以是多线程的,单线程进程同一时间只能在一个核心上执行,其性能取决于核心本身,而多线程进程同一时间可在多个核心上执行,因此它的性能就超越了单一核心上的性能表现。

因为许多应用程序都是单线程的,在多进程环境中,多插座、多核心的架构通常会带来方便,在虚拟化环境中,这个道理一样正确,Hypervisor允许在一台物理服务器上整合多个逻辑服务器,创建一个多进程和多线程的环境。

英特尔超线程技术

虽然单线程不能再拆分到两个核心上运行,但有些现代处理器允许同一时间在同一核心上运行两个线程,每个核心有多个并行工作能力的执行单元,很难看到单个线程会让所有资源繁忙起来。

下图展示了英特尔超线程技术是如何工作的,同一时间在同一核心上有两个线程执行,它们使用不同的资源,因此提高了吞吐量。

图6英特尔超线程技术工作原理

前端总线

在多插座和多核心的情况下,理解如何访问内存和两个核心之间是如何通信的非常重要,下图显示了过去许多英特尔处理器使用的架构,被称作前端总线(FSB)架构。

在FSB架构中,所有通信都是通过一个单一的,共享的双向总线发送的。

在现代处理器中,64位宽的总线以4倍速总线时钟速度运行,在某些产品中,FSB信息传输速率已经达到1.6GT/s。

图7基于前端总线的服务器平台架构

FSB将所有处理器连接到芯片组的叫做北桥(也叫做内存控制器中枢),北桥连接所有处理器共享访问的内存。

这种架构的优点是,每个处理器都可以访问其它所有处理可以访问的所有内存,每个处理器都实现了缓存一致性算法,保证它的内部缓存与外部存储器,以及其它所有处理器的缓存同步。

但这种方法设计的平台要争夺共享的总线资源,随着总线上信号传输速度的上升,要连接新设备就变得越来越困难了,此外,随着处理器和芯片组性能的提升,FSB上的通信流量也会上升,会导致FSB变得拥挤不堪,成为瓶颈。

双独立总线

为了进一步提高带宽,单一共享总线演变成了双独立总线架构(DIB),其架构如下图所示,带宽基本上提高了一倍。

图8基于双独立总线的服务器平台架构

但在双独立总线架构中,缓存一致性通信必须广播到两条总线上,因此减少了总有效带宽,为了减轻这个问题,在芯片组中引入了“探听过滤器”来减少带宽负载。

如果缓存未被击中,最初的处理器会向FSB发出一个探听命令,探听过滤器拦截探听,确定是否需要传递探听给其它FSB。

如果相同FSB上的其它处理器能满足读请求,探听过滤器访问就被取消,如果相同FSB上其它处理器不满意读请求,探听过滤器就会确定下一步的行动。

如果读请求忽略了探听过滤器,数据就直接从内存返回,如果探听过滤器表示请求的目标缓存在其它FSB上不存在,它将向其它部分反映探听情况。

如果其它部分仍然有缓存,就会将请求路由到该FSB,如果其它部分不再有目标缓存,数据还是直接从内存返回,因为协议不支持写请求,写请求必须全部传播到有缓存副本的所有FSB上。

专用高速互联

在双独立总线之后又出现了专用高速互联架构(DedicatedHigh-SpeedInterconnect,DHSI),其架构如下图所示。

图9基于DHSI的服务器平台架构

基于DHSI的平台使用四个独立的FSB,每个处理器使用一个FSB,引入探听过滤器实现了更好的带宽扩容,FSB本身没多大变化,只是现在变成点对点的配置了。

使用这种架构设计的平台仍然要处理快速FSB上的电信号挑战,DHSI也增加了芯片组上的针脚数量,需要扩展PCB路线,才能为所有FSB建立好连接。

英特尔QuickPath互联

随英特尔酷睿i7处理器引入了一种新的系统架构,即著名的英特尔QuickPath互联(QuickPathInterconnect,QPI),这个架构使用了多个高速单向连接将处理器和芯片组互联,使用这种架构使我们认识到了:

①.多插座和多核心通用的内存控制器是一个瓶颈;

②.引入多个分布式内存控制器将最符合多核处理器的内存需要;

③.在大多数情况下,在处理器中集成内存控制器有助于提升性能;

④.提供有效的方法处理多插座系统一致性问题对大规模系统是至关重要的。

下图显示了一个多核处理器,集成了内存控制器和多个连接到其它系统资源的英特尔QuickPath的功能示意图。

图10集成英特尔QPI和DDR3内存通道的处理器架构

在这个架构中,每个插座中的所有核心共享一个可能有多个内存接口的IMC(IntegratedMemoryControllers,集成内存控制器)。

IMC可能有不同的外部连接:

①.DDR3内存通道–在这种情况下,DDR3DIMM直接连接到插座,如下图所示,Nehalem-EP(至强5500)和Westmere-EP(至强5600)就使用了这种架构。

图11具有高速内存通道的处理器

②.高速串行内存通道–如下图所示,在这种情况下,外部芯片(SMB:

ScalableMemoryBuffer,可扩展内存缓存)创建DDR3内存通道,DDR3DIMM通过这个通道连接,Nehalem-EX使用了这种架构。

图12四插座Nehalem-EX

IMC和插座中的不同核心使用英特尔QPI相互通信,实现了英特尔QPI的处理器也可以完全访问其它处理器的内存,同时保持缓存的一致性,这个架构也叫做“缓存一致性NUMA(Non-UniformMemoryArchitecture非统一内存架构)”,内存互联系统保证内存和所有潜在的缓存副本总是一致的。

英特尔QPI是一个端到端互联和消息传递方案,在目前的实现中,每个连接由最高速度可达25.6GB/s或6.4GT/s的20条线路组成。

英特尔QPI使用端到端连接,因此在插座中需要一个内部交叉路由器,提供全局内存访问,通过它,不需要完整的连接拓扑就可以构建起系统了。

图12显示了四插座Nehalem-EX配置,每个处理器有四个QPI与其它三个处理器和Boxboro-EX芯片组互联。

二、内存子系统

电子业在内存子系统上付出了艰辛的努力,只为紧跟现代处理器需要的低访问时间和满足当今应用程序要求的高容量需求。

解释当前内存子系统之前,我们先了解一下与内存有关的一些常用术语。

①.RAM(随机访问存储器)

②.SRAM(静态RAM)

③.DRAM(动态RAM)

④.SDRAM(同步DRAM)

⑤.SIMM(单列直插式内存模块)

⑥.DIMM(双列直插内存模块)

⑦.UDIMM(无缓冲DIMM)

⑧.RDIMM(带寄存器的DIMM)

⑨.DDR(双数据速率SDRAM)

⑩.DDR2(第二代DDR)

⑩.DDR3(第三代DDR)

电子器件工程联合委员会(JointElectronDeviceEngineeringCouncil,JEDEC)是半导体工程标准化机构,JEDEC21,22定义了从256位SRAM到最新的DDR3模组的半导体存储器标准。

现代服务器的内存子系统是由RAM组成的,允许数据在一个固定的时间按任意顺序访问,不用考虑它所在的物理位置,RAM可以是静态的或动态的。

SRAM

SRAM(静态RAM)通常非常快,但比DRAM的容量要小,它们有一块芯片结构维持信息,但它们不够大,因此不能作为服务器的主要内存。

DRAM

DRAM(动态RAM)是服务器的唯一选择,术语“动态”表示信息是存储在集成电路的电容器内的,由于电容器会自动放电,为避免数据丢失,需要定期充电,内存控制器通常负责充电操作。

SDRAM

SDRAM(同步DRAM)是最常用的DRAM,SDRAM具有同步接口,它们的操作与时钟信号保持同步,时钟用于驱动流水线内存访问的内部有限状态机,流水线意味着上一个访问未结束前,芯片可以接收一个新的内存访问,与传统DRAM相比,这种方法大大提高了SDRAM的性能。

DDR2和DDR3是两个最常用的SDRAM,