Multisim电子秒表.docx

《Multisim电子秒表.docx》由会员分享,可在线阅读,更多相关《Multisim电子秒表.docx(8页珍藏版)》请在冰豆网上搜索。

Multisim电子秒表

--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--

Multisim-电子秒表(总7页)

电子秒表设计

1.实验目的:

学习数字电路中的基本RS触发器,单稳触发器,时钟发生器,译码显示电路等单元电路的综合应用。

学习电子秒表的调试方法。

2.实验原理

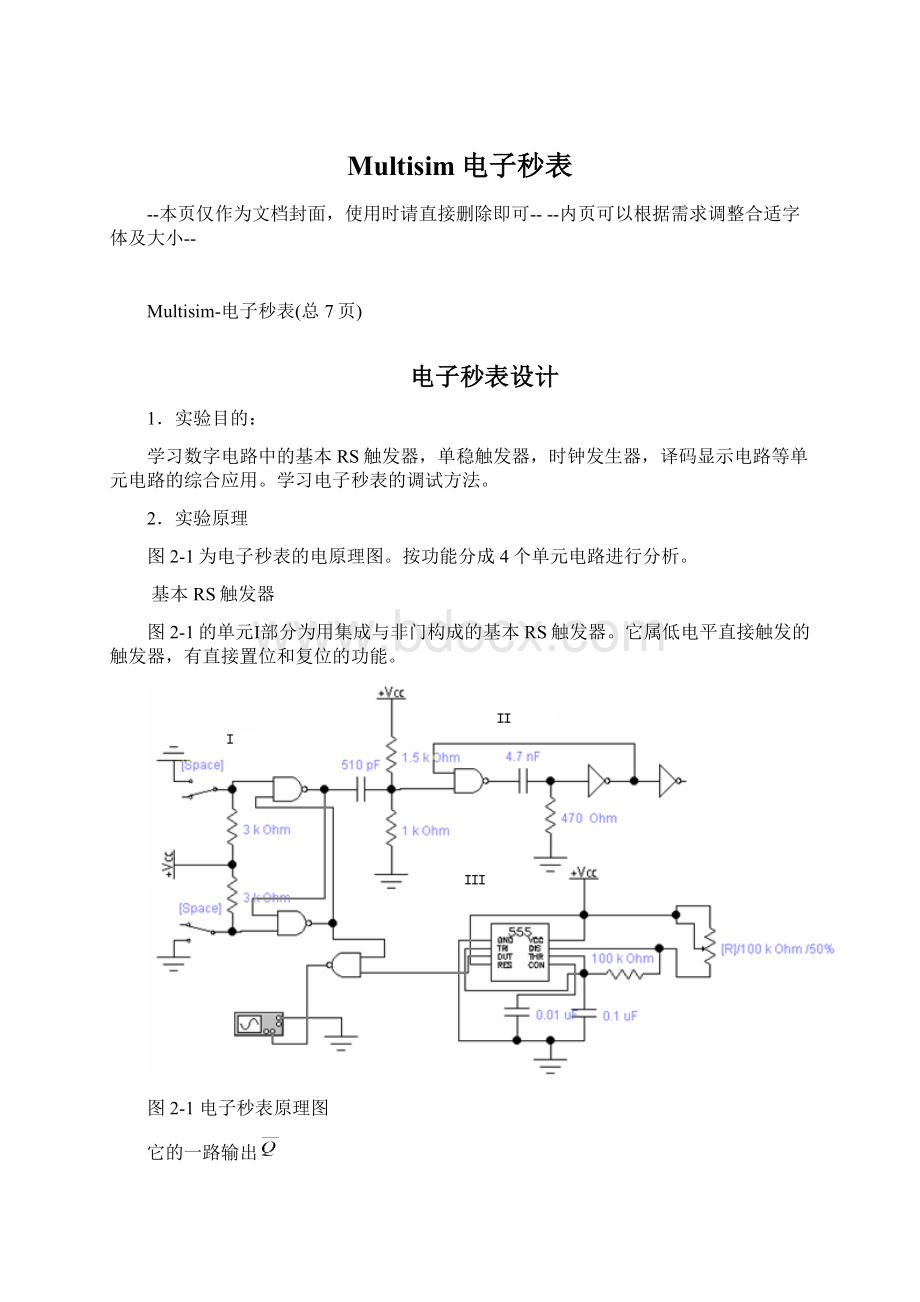

图2-1为电子秒表的电原理图。

按功能分成4个单元电路进行分析。

基本RS触发器

图2-1的单元Ⅰ部分为用集成与非门构成的基本RS触发器。

它属低电平直接触发的触发器,有直接置位和复位的功能。

图2-1电子秒表原理图

它的一路输出

作为单稳态触发器的输入,另一路输出Q作为与非门5的输入控制信号。

按动按钮开关K2到接地,则门一的输出

=1;门2的输出Q=0,K2复位后Q、

状态保持不变。

再按动按钮开关K1,则Q由0变为1,门5开启,为计数器启动作好准备,

由1变到0,送出负脉冲,启动单稳态触发器工作。

基本RS触发器在电子秒表中的职能是启动和停止秒表的工作。

单稳态触发器

图2-1的单元Ⅱ部分为用集成与非门构成的微分型单稳态触发器。

单稳态触发器的输入触发负脉冲信号Vi由基本RS触发器

端提供,输出负脉冲V0通过非门加到计数器的清除端R。

静态时,门4应处于截止状态,故电阻R必须小于门的开关电阻Roff。

定时元件RC取值不同,输出脉冲宽度也不同。

当触发脉冲宽度小于输出脉冲宽度时,可以省去输入微分电路的Rp和Cp。

单稳态触发器在电子秒表中的职能是为计数器提供清零信号。

时钟触发器

图2-1的单元Ⅲ为由555定时器构成的多谐振荡器,是一种性能较好的时钟源。

调节电位Rp,使在输出端3获得频率为50Hz的矩形波信号。

当基本RS触发器的Q=1时,门5开启,此时,50Hz脉冲信号通过门5作为计数脉冲加于计数器74LS90(Ⅰ)的计数输入端CP2。

计数及译码显示

二-五-十进制加法计数器74LS90构成电子秒表的计数单元。

其中计数器①接成五进制形式,对频率为50Hz的时钟脉冲进行五分频,在输出端QD取得周期为秒的矩形脉冲,作为计数器②的时钟输入。

计数器②及计数器③接成8421码十进制形式,其输出端与实验装置的译码显示单元的相应输出端连接,可显示~和1~计时。

表2-1为74LS90引脚功能表。

输入

输出

功能

清0

置9

时钟

QDQCQBQA

R0

(1)、R0

(2)

S9

(1)、S9

(2)

CP1、CP2

11

0*

*0

**

0000

清0

0*

*0

11

**

1001

置9

1*

*0

1*

*0

↓1

QA输出

二进制计数

1↓

QDQCQB输出

五进制计数

↓QA

QDQCQBQA输出8421DCB码

十进制计数

QD↓

QAQDQCQB输出5421DCB码

十进制计数

11

不变

保持

74LS90是异步二-五-十进制加法计数器,它既可以作二进制加法计数器,也可以作五进制和十进制加法计数器。

通过不同的连接方式,74LS90可以实现4种不同的逻辑功能;而且还可以借助R0

(1)、R0

(2)对计时器清零,借助S9

(1)、S9

(2)将计数器置9。

其具体功能详述如下:

(1)当计数脉冲从CP1输入,QA作为输出端,为二进制计数器。

(2)当计数脉冲从CP2输入,QDQCQB作为输出端,为异步五进制加法计数器。

(3)若将CP2和QA相连,计数脉冲由CP1输入,QD、QC、QB和QA作为输出端,则构成异步8421码十进制加法计数器。

(4)若将CP1和QD相连,计数脉冲由CP2输入,QA、QD、QC和QB作为输出端,则构成异步5421码十进制加法计数器。

(5)清零、置9功能。

异步清零:

当R0

(1)、R0

(2)均为“1”,且S9

(1)、S9

(2)中有“0”时,可实现异步清零,即QDQCQBQA=0000。

置9功能:

当S9

(1)、S9

(2)均为“1”,且R0

(1)、R0

(2)中有“0”时,可实现置9功能,即QDQCQBQA=1001。

基于74LS190的记时电路请读者自行设计。

计时电路也可采用74160实现,秒计时电路如图2-2所示,分、时计时电路请读者参考秒计时电路自行设计。

图2-2采用74160设计的秒计时电路

3、实验仿真

对定时时钟信号仿真

图3-1555定时器产生时钟信号原理图

图3-2555定时器产生波形

计数器仿真

图3-3计数器仿真原理图

图3-4计数器仿真结果

图3-4整体效果图

4.心得与体会

通过此次电路设计,我的理论知识掌握的更扎实,动手能力明显提高,同时,通过网上搜索等多方面的查询资料,我学到了书本上没有的知识。

还有加深了对课本知识的认识理解以及应用,对一些器件的具体应用思想也有深刻的理解,以及对电路设计方法的实际电路连接实现特定功能也有了一定的认识。

在整个设计过程中,我个人感觉调试部分是最难的,调试是一个经验的积累过程,没有经验是不可能在短时间内将其完成的!