DC常用命令及脚本.docx

《DC常用命令及脚本.docx》由会员分享,可在线阅读,更多相关《DC常用命令及脚本.docx(35页珍藏版)》请在冰豆网上搜索。

DC常用命令及脚本

利用DC进行综合设计

(2012-03-2517:

45:

10)

转载▼

标签:

dc

综合

杂谈

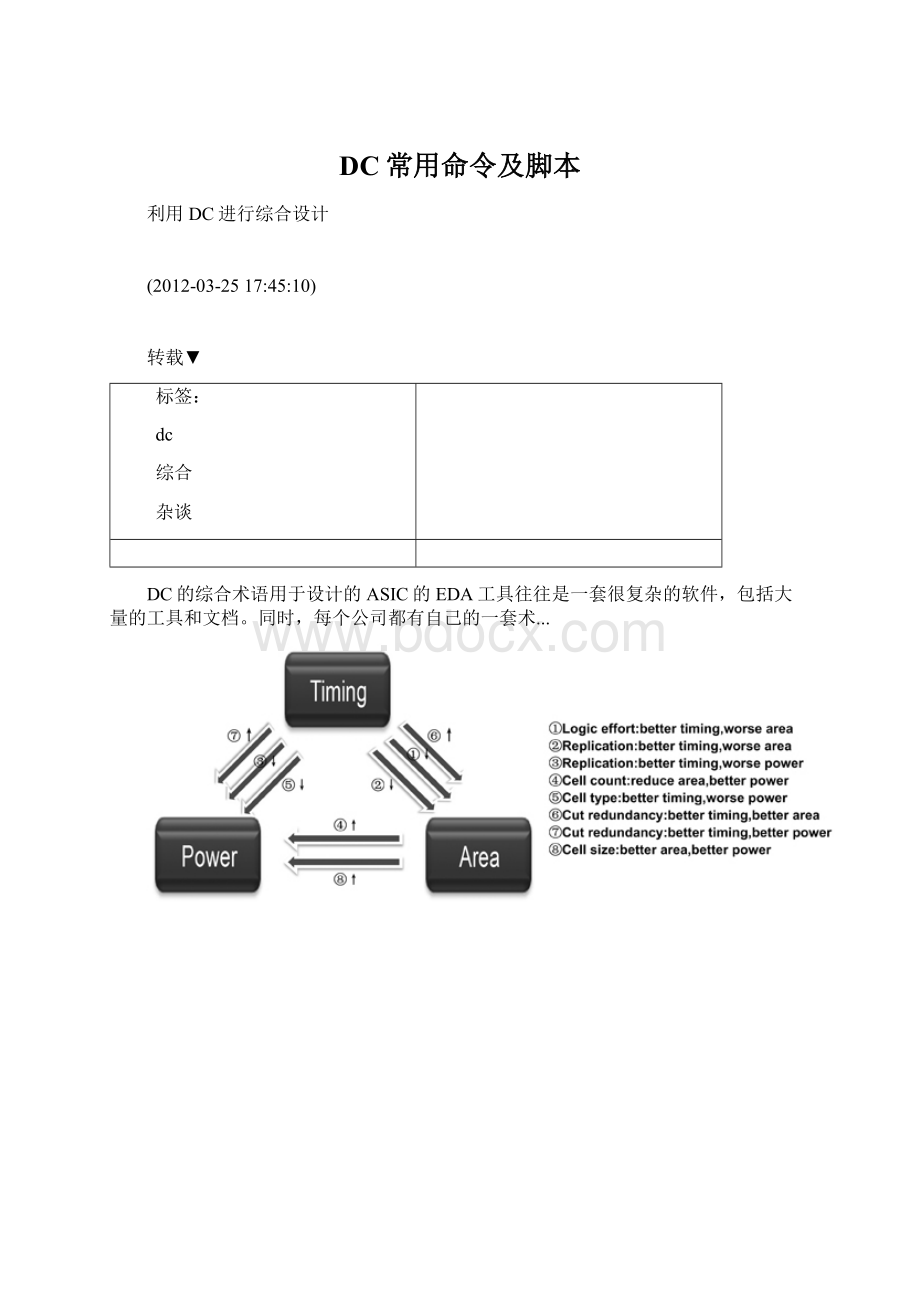

DC的综合术语用于设计的ASIC的EDA工具往往是一套很复杂的软件,包括大量的工具和文档。

同时,每个公司都有自己的一套术...

一、预备知识

1.1、DC的综合术语

用于设计的ASIC的EDA工具往往是一套很复杂的软件,包括大量的工具和文档。

同时,每个公司都有自己的一套术语。

只有理解了这些术语的含义才能很好的掌握这些工艺。

1设计和设计对象

设计是实现一定逻辑功能的电路的描述。

设计对象就是在设计中被DC命令、属性和约束操作或控制的对象。

常用的设计中包括元件、网络、端口、引脚和时钟。

另外,一个设计可能包括某个相同子设计或库元件的多个例化。

这时候被例化的设计或库元件称作参考。

在一个设计中查找某个对象的命令:

find,这是在DC命令中很常用的命令。

如:

列出当前设计的所有端口(ports):

Dc_shell>findportORfind(port,”*”)

列出所有包含”DW”字母的元件:

dc_shell>find(cell,”*DW*”)

列出cba_core库中的AN2门的所有接脚:

dc_shell>find(pin,cba_core/AN2

Read–formatvhdl./src/rtl/timer_tugw.vhd

Read–formatvhdl./src/rtl/test_top.vhd

Check_error–v

If(dc_shell_status==1){exit1}

Current_designtest_top

Link

Check_error–v

If(dc_shell_status==1){exit1}

Includepass0/constraint/test_top.con

Check_error–v

If(dc_shell_status==1){exit1}

Set_max_area0.0000

Set_flattenfalse

Echo”***doingfullcompileforthepartition‘test_top’***”

Shdate;

Compile–map_effortmedium

Check_error–v

If(dc_shell_status==1){exit1}

Shdate;

Check_design

Compile_top_acs_partion=ture

Compile_top_all_paths=true

Echo”***doingboundarycompileforthepartition‘test_top’***”

Shdate;

Compile–top

Uniquify

Check_error–v

If(dc_shell_status==1){exit1}

Shdate;

Current_designtest_top

Write–formatdb–hierarchy–outputpass0/db/test_top.db

Write–formatverilog–hierarchy–outputpass0/db/test_top.v

Write–formatvhdl–hierarchy–outputpass0/db/test_top.vhd

Report_timing>pass0/report/test_top.tim

Report_area>pass0/report/test_top.area

Report_constraints>pass0/report/test_top.cstr

Report_qor>pass0/report/test_top.qor

Report_constraints–all_violators–verbose>pass0/report/test_top.vio

quit

脚本文件可以使用任何一个文本编辑工具产生或修改,也可以在dc_shell中执行write_scirpt命令产生。

如,下面的命令就是将设计的属性和约束等信息保存到名为test.scr的脚本文件。

Dc_shell>write_>test.scr

脚本文件的语法应该符合dc_shell命令的语法。

DC提供了一个语法检查工具和一个上下文检查工具,他们可以检查脚本文件的语法和脚本文件的错误,并提供相应的错误信息。

语法检查工具检查脚本文件的语法,但是不执行其中的命令。

语法检查实现的功能包括:

检查预先定义的命令参数是否正确,检查必须的参数是否存在、文件重定向问题、检查引用文件中的命令的语法、按照dc_shell正常的使用方式执行赋值。

要使用语法检查,我们必须对该功能进行使能,此后每次引用或执行脚本前就会首先进行语法检查。

在dc_shell中使能语法检查功能的方法如下:

Dc_shell>syntax_checktrue

Syntaxcheckon.

上下文检查工具检查上下文的错误。

在执行一个脚本文件前,我们应该对其进行上下文检查。

上下文检查在检查每个命令的语法的同时,还会读入设计、检查设计和库文件是否有效、文件设法齐全等。

其执行具体的功能包括:

检查设计对象和属性的合法性,检查用户定义的属性,检查变量是否存在,检查条件语句的条件,检查循环语句,读入需要读入的文件,根据命令重定向文件,检查库和库对象。

要使用上下文检查,我们必须对该功能进行使能,此后每次引用或执行脚本文件前就会进行上下文检查。

使能命令如下。

Dc_shell>context_checktrue

Contextcheckon.

最后,脚本文件的执行是比较简单的,可以通过两种方法:

在dc_shell中,应该使用include命令执行脚本文,include

在启动dc_shell时,可以使用-f选项执行脚本文件,dc_shell–f

在执行脚本前,如果我们激活了脚本语法检查和上下文检查,那么就会先进行相应的检查。

二、准备HDL文件

输入DC的文件通常是HDL文件,HDL的代码质量将直接影响综合的效果,因此在编码中必须考虑设计数据管理、设计划分和HDL代码的风格

2.1、数据文件管理

首先,由于综合过程中需要大量的数据和多种文件,因此数据的管理就显得非常重要。

这种管理通常设计两个部分,设计数据控制和数据组织。

控制设计数据主要是控制数据的创建、维护、覆盖和删除等。

这和软件工程中的版本控制是基本一致的。

在DC中对于不同类型的的文件,一般有约定的扩展名。

在控制数据的同时还必须注意对数据合理有效的组织,一般,在使用DC综合的时候,我们都会使用层次化的目录结构来存放数据文件。

相对于不同的综合策略,我们也有两种不同的目录结构。

可以看出,在应用自顶向下的综合策略时,由于综合是从顶层模块开始一次到各个模块,所以只需要一个综合目录。

而自底向上的综合则现对各个模块进行综合,因此可能有多个综合目录。

2.2、设计划分

对设计的合理划分可以改善综合的结果,减少操作的时间,简化约束文件和脚本文件。

划分直接影响设计中模块的大小,如果模块太小,相当于人为的制造了一个界限,将限制DC有效的进行优化。

另一方面,如果划分的模块太大,则会增加综合消耗的时间。

在划分的时候还要考虑设计的重用性,主要应该注意以下几点:

详细定义并记录设计的接口,尽可能使接口标准化,编写参数化的代码。

通常,我们设计的划分一般使用以下策略:

(1)将相关的组合逻辑划分在一起

(2)消除胶连逻辑

(3)模块的输出都应该使用寄存器

(4)按照设计目标进行划分

按照编译技术划分,将设计中使用不同编译技术的部分划分到不同的模块。

特别使当设计中既有高度结构化的逻辑(ALU),又有随机逻辑时,应当将他们分开。

因为对于结构化的逻辑应该使用结构化编译,而对随机逻辑,应该使用扁平化的编译。

可以将共享的资源划分到一起

将用户定义的资源和他们驱动的逻辑划分到一起,用户定义的资源包括用户定义的函数、过程、宏单元和designware元件。

DC对于这些资源无法自动实现共享和复制。

因此,将他们和它们所驱动的逻辑放在一起,我们就可以手工的插入多个元件来增大驱动能力。

把顶层逻辑分成至少3级,将一些特殊的功能独立出来,如管脚、时钟、边界扫描和异步逻辑等。

如下图所示,一般情况下,设计的最顶层是I/O管脚。

下一层包括边界扫描、时钟处理、异步逻辑和核心逻辑。

增加这一层是为了I/O管脚例化的灵活性.将时钟处理独立出来是为了对这部分进行详细的分析仿真。

将异步逻辑独立出来是为了可测性和静态时序分析的问题限制在一个比较小的范围之内。

设计划分的方法分为HDL划分和DC中的划分。

HDL的划分就是根据上面一些原则通过HDL代码对设计进行划分。

而DC中的划分是在DC中通过使用专门的命令,改变HDL中的划分和层次的结构。

DC中提供了两个与此相关的命令:

group,ungroup。

三、确定设计库

综合之前必须设定链接库、目标库、符号库和综合库。

连接和目标库属于工艺库,它们定义了半导体生产厂的工艺元件和其它信息。

符号库定义用于designvision或designanalyzer中的元件的符号表示

确定这些库是使用DC进行综合的前提条件,因此我们必须掌握DC中库的命令的使用,以便DC可以正确的使用库中的数据。

3.1、工艺库

工艺库包括描述每个单元的功能和特性的信息。

工艺库由半导体厂商提供和维护。

元件库包括元件名称、元件接脚名称、面积、时延信息、接脚负载。

同时工艺库还定义了实现设计功能必须满足的条件。

这些条件也可以称作设计规则约束。

除此之外,工艺库还确定了工艺的工作条件和线载模型。

工艺库在DC中有下面一些用途:

(1)实现设计的功能,在dc综合过程中要将设计映射到某个工艺库,他们称作目标库。

目标库包括了所有用于生产网表的元件以及设计工作条件的定义。

(2)解析元件参考,在dc中用于解析元件参考的工艺库称为链接库。

链接库中除了工艺库外还可能包括设计文件。

(3)计算时延和路径延时,链接库还定义了用于计算时延值和路径延时的时延模型

(4)计算消耗的功率

3.2、设置库变量

在使用dc综合之前我们必须对库进行设置。

具体的方法是使用dc_shell中的变量来确定各种库。

变量和库文件的定义见下表

在确定库的位置的时候,我们可以使用完整的路径也可以只用文件名。

如果只确定了文件名,DC会在search_path变量确定的搜索路径中查找这个文件。

在设置工艺库和链接库的时候要注意:

链接库包括了工艺库和设计文件。

因此,link_library变量的值是工艺库加上一个星号“*”,表示链接时,DC既搜索工艺库,也搜索调入内存中的设计文件。

除了设置库变量,DC还支持各种对库的操作,如:

读入和保存库,列出使用的库,显示库的内容,确定库的对象甚至直接对库对象进行操作。

如下为一个工艺库的例子:

Cell(AND23)//元件名称

(area:

8.000;//元件面积

Pin(Y)(direction:

output;

Timing()(

Related_pin:

”A”;

Timing_sence:

positive_unate;

Rise_propagation(drive_3table_1)(values(“0.2626,0.2607…..”))//接脚延时

Fall_progpagation(drive_3_table_3)(values(“0.1316,0.1331….”))

)

……..

)

Timing()(related_pin:

”B”;

……………..

)

:

”A&B”;//接脚的功能描述

Max_capatiance:

0.00220

Min_capatiance:

0.00220//输出引脚的设计规则

)

Pin(A)(direction:

input;

Capacitance:

0.012000;)

Pin(B)(direction:

input;//输入引脚的电器特性

Capacitance:

0.010000;)

)

四、DC对设计的一些操作

4.1、读入文件

下表列出了DC支持的所有文件类型

对于设计文件,可以使用两种方法读入。

使用read_file命令或使用analyze和elaborate命令。

这两种方法有一些区别。

简单的说,前一种适用于各种类型的文件,而后一种主要用于综合VHDL和verilog文件。

但是使用后者有一些特殊的功能。

具体说来,analyze的功能包括读入HDL源文件,检查错误,产生独立于HDL的中间类型的HDL库对象,存储中间文件。

如果一个设计执行的analyze命令,只需要在这个设计改变之后再执行该操作。

Elaborate命令根据analyze产生的中间文件产生一个与工艺无关的设计。

这个操作还将HDL中的算术操作用于DESIGNWARE库中的元件替代,同时确定总线的宽度。

当设计读入内存之后,它将转换为synopsys内部数据库的格式。

DC之后的综合优化过程都是对内存中的设计执行的。

(1)链接

对于一个完整的设计,必须把所有的库元件和他们对应的设计参考链接起来。

对于每一个设计,还必须有一个参考来衔接子设计和链接库。

这一过程称为链接设计或参考解析。

换句话说,链接就是要在链接库中找到设计中使用的所有元件和子设计,保证设计的完整。

如果不能正确的链接,则无法进行以后的综合等操作。

DC通过一下步骤完成参考解析:

首先,它确定哪个库元件和子设计在当前的设计中被使用。

然后,它在链接库中定位这些参考。

最后,把定位好的参考和设计链接起来。

如图。

链接的操作可以自动进行,也可以手工完成。

当使用一些DC命令,如compile时会自动进行链接。

如果需要,也可以使用link命令进行手工链接。

(2)对设计和设计对象的操作

这些操作时DC中的一些基本操作,和其它EDA软件中的操作类似,如生成新设计、拷贝设计、重新命名等。

其中比较重要的有以下几种:

设置当前设计。

在DC中,我们应当注意当前设计的概念,因为大多数的命令都是针对当前设计进行的。

一般说来,如果成功的读入了一个设计之后,这个设计就会作为当前设计。

另外,如果指定了一个当前设计,可以使用current_design命令。

列出设计和设计对象。

使用list_designs命令来列出内存中的设计,其中带“*”为当前设计。

下表也列出了显示设计对象信息的一些命令。

改变设计的层次,在DC中我们可以改变HDL所描述的设计层次关系。

首先,使用report_hierarchy命令可以显示设计当前的层次关系。

然后,使用group可以将一些元件或子设计组合起来,增加一个逻辑层次。

或使用ungroup名去掉一个逻辑层次。

编辑设计,使用下表列出的命令可以对设计对象进行编辑,如生成,删除等。

Creat_cell生成一个元件

Remove_cell删除一个元件

Create_net生成一个网络

Connect_net连接一个网络

Disconnect_net断开一个网络

Remove_net删除一个网络

Create_port生成一个端口

Remove_port删除一个端口

Create_bus生成一个总线

Remove_bus删除一个总线

4.2、属性的处理

属性描述了设计数据库中对象逻辑的电气、物理和其它特性。

一个属性通常都是附加给一个设计对象并存储于设计数据库中。

DC中,我们可以设置和使用以下一些对象的属性

整个设计

设计对象,如时钟,网络和端口

设计中的子设计或元件的例化

工艺库,库元件

属性有自己的名称、类型和值。

属性一般有以下几种类型:

串、数或是逻辑。

属性可以是DC预设的,这些属性可以被DC识别;也可以是用户定义的。

一些属性是只读的,其值由DC设置,用户无法修改,另一些是用户可以自己修改的。

例如,我们经常使用“dout_touch”属性,它可以付给网络,单元,端口或设计。

而当我们需要设置这个属性的时候,需要专门的命令:

set_dont_touch

而对于一般的属性,可以使用命令set_attribute来设置。

Design Compiler 综合脚本常用命令和模板

(2012-03-2517:

47:

12)

转载▼

标签:

dc

综合

script

杂谈

分类:

微电子

参照自己的设计,以及自己的工艺信息,适当修改下面的Constraints和RunScript等的脚本,添加一些相关的约束语句,就可以运行了详细...

参照自己的设计,以及自己的工艺信息,适当修改下面的Constraints 和 RunScript等的脚本,添加一些相关的约束语句,就可以运行了

详细的命令请参照DC的官方UserGuide等相关资料。

InvokingDesignCompiler

Unix%design_vision #InteractiveGUI,WLMmode

Unix%design_vision–topographical #InteractiveGUI,Topographicalmode

Unix%dc_shell-t #Interactiveshell,WLMmode

Unix%dc_shell-t–topographical #Interactiveshell,Topographicalmode

Unix%dc_shell-t–fRUN.tcl|tee–imy.log #Batchmode

.synopsys_dc.setup

setsearch_path“$search_pathlibsconsunmappedrtl”

setsynthetic_librarydw_foundation.sldb

settarget_library65nm.db

setlink_library“*$target_library$synthetic_libraryIP.db”

setsymbol_library65nm.sdb

define_design_libWORK–path./work

set_svf

set_vsdc

historykeep200

setsh_enable_page_modefalse

setcache_write.

setcache_read$cache_write

suppress_message{LINT-28LINT-32LINT-33UID-401}

setalib_library_analysis_path[get_unix_variableHOME]

aliashhistory

aliasrc“report_constraint-all_violators”

TCLCommandsandConstructs

setPER2.0 #Defineavariableanditsvalue

echo$PER #Variablesubstitutionà2.0

setMARG0.95

expr$PER*$MARG #expr:

*,/,+,-,>,<,=,<=,>=

setpci_ports[get_portsA] #Imbeddedcommand

setpci_ports[get_ports“Y?

?

MZ*”] #Wildcards

echo“EffctvP=\ #Softquotesà1.9

[expr$PERIOD*$MARGIN]”

echo{EffctvP=\ #Hardquotes

[expr$PERIOD*$MARGIN]} #àEffctvP=[expr$PER*$MARG]

#Commentline

setCOMMENTin_line; #In-linecomment

setMY_DESIGNS{B1.v...B26.v} #foreachloop

foreachDESIGN$MY_DESIGNS{

read_verilog$DESIGN

}

for{seti1}{$i<27}{incri}{ #forloop

read_verilogBLOCK_$i.v

}

HelpfulUNIX-likeDC-shellcommands

pwd

cd

ls

history

!

!

!

7

!

report

sh

printenv

get_unix_variableARCH

Constraints

reset_design

set_max_area0

create_clock-period2–nameMain_Clk[get_portsClk1]

create_clock–period2.5–waveform{23.5}[get_portsClk2]

create_clock–period3.5–nameV_Clk;#VIRTUALclock

set_clock_uncertainty–setup0.14[get_clocks*]

set_clock_uncertainty–setup0.21–from[get_clocksMain_Clk]–to[get_clocksClk2]

set_clock_latency–max0.6[get_clocksMain_Clk]

set_clock_latency–source–max0.3[get_clocksMain_Clk]

set_clock_transition0.08[get_clocksMain_Clk]

set_input_delay-max0.6-clockMain_Clk[all_inputs]

set_input_delay–max0.3–clockClk2–clock_fall–add_delay[get_ports“BE”]

set_input_delay-max0.5-clock–network_latency_includedV_Clk[get_ports“ACF”]

set_output_delay-max0.8-clock–source_latency_includedMain_Clk[all_outputs]

set_output_delay-max1.1-clockV_Clk[get_ports“OUT2OUT7]

set_max_capacitance1