EDA整理.docx

《EDA整理.docx》由会员分享,可在线阅读,更多相关《EDA整理.docx(17页珍藏版)》请在冰豆网上搜索。

EDA整理

专用集成电路(ApplicationSpecificIntegratedCircuit,ASIC)

单片电子系统(SystemonaChip,SoC)

电子设计自动化(ElectronicDesignAutomation,EDA)

硬件描述语言(HardwareDescriptionLanguage,HDL)

现场可编程门阵列(FieldProgrammableGateArray,FPGA)

复杂可编程逻辑器件(ComplexProgrammableLogicDevice,CPLD)

专用集成电路(ASIC)

IP(IntellectualProperty)--知识产权核或知识产权模块

FSM

1.2EDA技术实现的目标

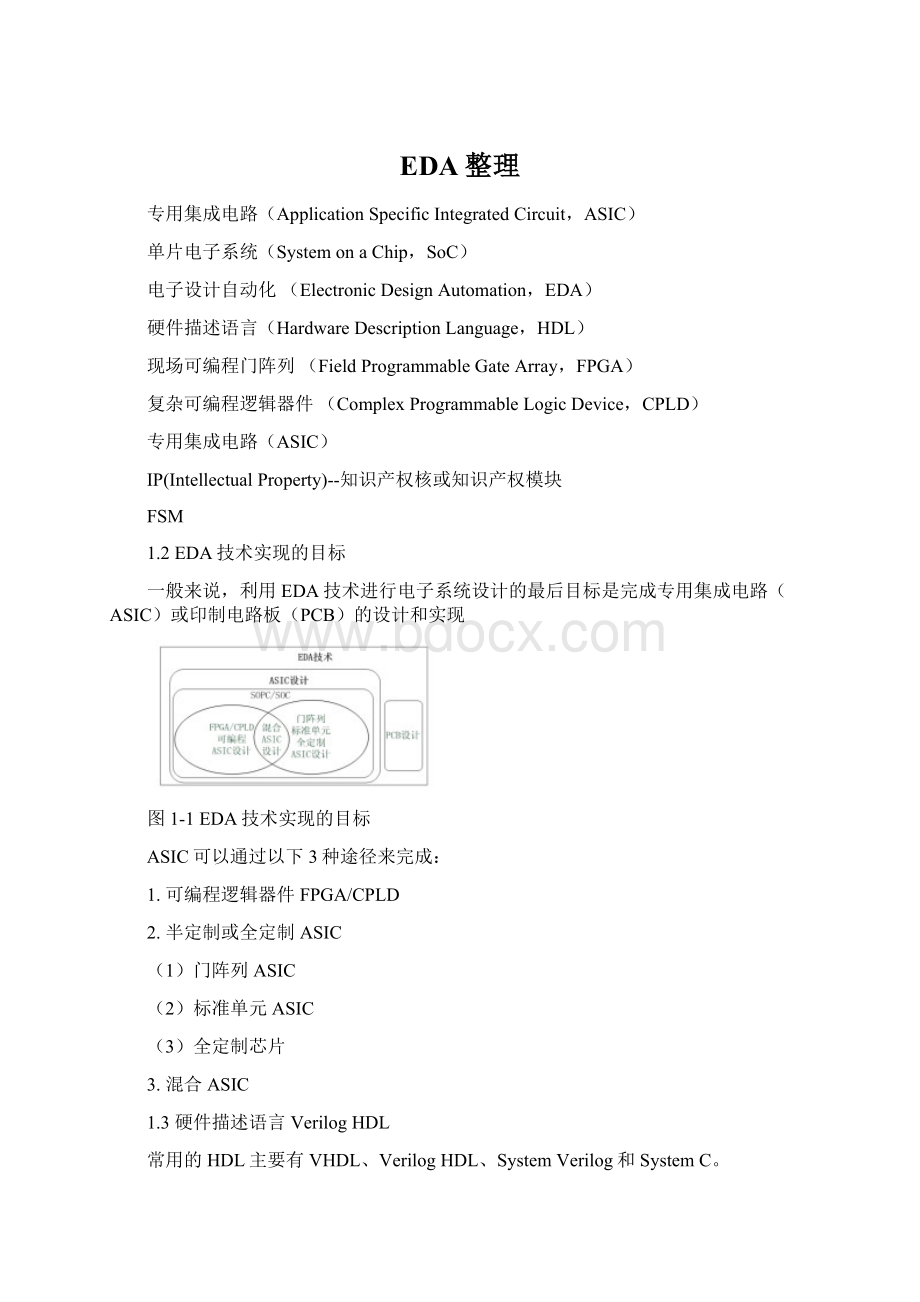

一般来说,利用EDA技术进行电子系统设计的最后目标是完成专用集成电路(ASIC)或印制电路板(PCB)的设计和实现

图1-1EDA技术实现的目标

ASIC可以通过以下3种途径来完成:

1.可编程逻辑器件FPGA/CPLD

2.半定制或全定制ASIC

(1)门阵列ASIC

(2)标准单元ASIC

(3)全定制芯片

3.混合ASIC

1.3硬件描述语言VerilogHDL

常用的HDL主要有VHDL、VerilogHDL、SystemVerilog和SystemC。

2.1FPGA/CPLD设计流程

2.3常用EDA工具

EDA工具大致可以分为如下5个模块:

2.4QuartusII简介

图2-5QuartusII设计流程

2.5IP核简介

IP(IntellectualProperty)就是知识产权核或知识产权模块的意思,在EDA技术和开发中具有十分重要的地位。

FPGA(FieldProgrammableGateArray) 现场可编程门阵列

(可编程的查找表(LookUpTable,LUT)结构,LUT是可编程的最小逻辑构成单元。

)

CPLD(ComplexProgrammableLogicDevice)复杂可编程逻辑器件

(是基于乘积项的可编程结构,即可编程的与阵列和固定的或项组成。

)

3.2简单PLD原理

3.2.2PROM

图3-11PROM表达的PLD图阵列图3-12用PROM完成半加器逻辑阵列Mp-1,m-1这里p=4行、m=2

3.

3CPLD结构与工作原理

(2)宏单元

(3)扩展乘积项

图3-28共享扩展乘积项结构

基于查找表的结构模块

什么是查找表

一个N输入查找表(LUT,LookUpTable)可以实现N个输入变量的任何逻辑功能,如N输入“与”、N输入“异或”等。

输入多于N个的函数、方程必须分开用几个查找表(LUT)实现

3.4FPGA结构与工作原理

3.4.1查找表LUT

图3-32

FPGA查找表单元:

图3-33

FPGA查找表单元内部结构

VerilogHDL设计初步

4.1组合电路的VerilogHDL描述

4.1.24选1多路选择器及其VerilogHDL描述2

3.assign连续赋值语句

assign目标变量名=驱动表达式;

assignDOUT=a&b;

assignDOUT=a&b|c;

assignDOUT=e&f|d;

4.wire定义网线型变量

wire变量名1,变量名2,...;

wire[msb:

lsb]变量名1,变量名2,...;

wire[7:

0]a;

wireY=tmp1^tmp2;

wiretmp1,tmp2;assignY=tmp1^tmp2;

5.注释符号

4.1.34选1多路选择器及其VerilogHDL描述3

1.if_else条件语句

if(S)Y=A;elseY=B;

if(S)Y=A;elsebeginY=B;Z=C;Q=1b0;end

2.过程赋值语句

(1)阻塞式赋值。

“=”

(2)非阻塞式赋值。

3.数据表示方式

2.全加器顶层文件设计

Verilog中元件例化语句的结构比较简单,一般格式如下:

<模块元件名>:

<例化元件名>(.例化元件端口(例化元件外接端口名),...);

9.1VerilogHDL文字规则

1.整数

2.实数

3.字符串

4.标识符

5.关键词

9.2VerilogHDL数据类型

9.2.1net网线类型

9.2.2register寄存器类型

9.2.3存储器类型

9.3操作符

●单目操作符(unaryoperators):

操作符可带一个操作数,如逻辑取反~。

●双目操作符(binaryoperators):

操作符可带两个操作数,如与操作&。

●三目操作符(ternaryoperators):

操作符可带三个操作数,如条件操作符。

1.逻辑操作符

2.缩位操作符

11.1Verilog仿真方法与仿真流程

11.4.1基本元件及其用法

1.and、nand、or、nor、xor和xnor

2.buf与not

3.bufif1、bufif0、notif1和notif0

1.pullup和pulldown

2.pmos、nmos、rnmos和rpmos

3.cmos和rcmos

4.tran和rtran

5.tranif0、rtranif0、tranif1和rtranif1

第9章VerilogHDL基本要素与语句

函数

任务

函数能调用另一个函数,但不能调用另一个任务

任务能调用另一个任务,也能调用另一个函数

函数总是在仿真时刻0就开始执行

任务可以在非零仿真时刻执行

函数一定不能包含任何延迟、事件或者时序控制

任务可以包含延迟、事件或者时序控制声明语句

函数至少有一个输入变量,

函数可以有多个输入变量声明语句

任务可以没有或者有多个

输入(input)、输出(output)和双向(inout)变量

函数只能返回一个值,

函数不能有输出(output)或者双向(inout)变量

任务不返回任何值,

任务可以通过输出(output)或者双向(inout)变量传递多个值

表9.1任务和函数的区别

•任务使用关键字task和endtask进行声明。

如果子程序满足下面任意一个条件,则必须使用任务而不能使用函数:

•.子程序中包含有延迟、时序或者事件控制结构。

•.没有输出或者输出变量的数目大于1。

•.没有输入变量。

•Verilog使用关键字function和endfunction来进行函数声明。

对于一个子程序来说,如果下面的所有条件全部成立则可以使用函数来完成:

•●在子程序内不含有延迟、时序或者控制结构。

•●子程序只有一个返回值。

•●至少有一个输入变量。

•●没有输出或者双向变量。

•●不含有非阻塞赋值语句。

***************************************************************编程题************************************************************

4-5用Verilog设计一个3-8译码器,要求分别用case语句和if_else语句。

比较这两种方式。

(必考)

moduledecoder3_8(G1,Y,G2,A,G3);

inputG1,G2,G3;

wireG1,G2,G3;

input[2:

0]A;

wire[2:

0]A;

output[7:

0]Y;

reg[7:

0]Y;

regs;

always@(A,G1,G2,G3)

begin

s<=G2|G3;

if(G1==0)

Y<=8'b1111_1111;

elseif(s)

Y<=8'b1111_1111;

else

case(A)

3'b000:

Y=8'b11111110;

3'b001:

Y=8'b11111101;

3'b010:

Y=8'b11111011;

3'b011:

Y=8'b11110111;

3'b100:

Y=8'b11101111;

3'b101:

Y=8'b11011111;

3'b110:

Y=8'b10111111;

3'b111:

Y=8'b01111111;

default:

Y=8'bxxxxxxxx;

endcase

end

endmodule

moduledecoder3_8(G1,Y,G2,A,G3);

inputG1,G2,G3;

wireG1,G2,G3;

input[2:

0]A;

wire[2:

0]A;

output[7:

0]Y;

reg[7:

0]Y;

regs;

always@(A,G1,G2,G3)

begin

s<=G2|G3;

if(G1==0)

Y<=8'b1111_1111;

elseif(s)

Y<=8'b1111_1111;

elsebeginif(A==3'b000)Y=8'b11111110;

elseif(A==3'b001)Y=8'b11111101;

elseif(A==3'b010)Y=8'b11111011;

elseif(A==3'b011)Y=8'b11110111;

elseif(A==3'b100)Y=8'b11101111;

elseif(A==3'b101)Y=8'b11011111;

elseif(A==3'b110)Y=8'b10111111;

elseif(A==3'b111)Y=8'b01111111;

elseY=8'bxxxxxxxx;end

end

endmodule

4-6 图4-26所示的是双2选1多路选择器构成的电路MUXK。

对于其中MUX21A,当s=0和s=1时,分别有y=a和y=b。

试在一个模块结构中用两个过程来表达此电路。

答:

参考实验1

moduleMUXK(a1,a2,a3,s0,s1,outy);

inputa1,a2,a3,s0,s1;

outputouty;

wireouty;

wiretmp;

mux21au1(.a(a2),.b(a3),.s(s0),.y(tmp));

mux21au2(.a(a1),.b(tmp),.s(s1),.y(outy));

endmodule

4-8给出一个4选1多路选择器的Verilog描述。

此器件与图4-1类似,但选通控制端有4个输入:

S0、S1、S2、S3。

当且仅当S0=0时:

Y=A;S1=0时:

Y=B;S2=0时:

Y=C;S3=0时:

Y=D。

moduleMUX41a(A,B,C,D,S0,S1,S2,S3,Y);

outputY;//定义Y为输出信号

inputA,B,C,D;

inputS0,S1,S2,S3;

regY;//定义输出端口信号Y为寄存器型变量

always@(A,B,C,S0,S1,S2,S3)begin//块语句起始

if(S0==0)Y=A;//当S0==0成立,即(S0==0)=1时,Y=A;

elseif(S1==0)Y=B;//当(S1==1)为真,则Y=B;

elseif(S2==0)Y=C;//当(S2==2)为真,则Y=C;

elseif(S3==0)Y=D;//当(S3==3)为真,即Y=D;

end//块语句结束

endmodule

8-3根据图8-32(a),按照图8-32(b)写出对应结构的VerilogHDL状态机。

modulefsmb(CLK,rese,ina,outa);

inputCLK,reset;

inputina;

outputouta;

regouta;

reg[1:

0]c_state;

parameter[1:

0]st0=0;

parameter[1:

0]st1=1;

parameter[1:

0]st2=2;

parameter[1:

0]st3=3;

always@(posedgeCLKornegedgereset))

begin:

if(!

reset)c_state<=st0;

elsebegin

case(c_state)

st0:

begin

if(ina=3'b101)outa<=4'b0010;

elseifina=3'b111outa<=4'b1100;

c_state<=st1;

end

st1:

begin

outa<=4'b1001;

if(ina==3'b000)

begin

c_state<=st1;

end

elseif(ina==3'b011)

begin

c_state<=st2;

end

end

st2:

begin

outa<=4'b1111;

if(ina==3'b100)

begin

c_state<=st2;

end

elseif(ina==3'b011)

begin

c_state<=st1;

end

elseif(ina/==3'b100)

begin

c_state<=st3;

end

end

st3:

begin

if(ina=3'b101)outa<=4'b1101;

elseif(ina=3'b011)outa<=4'b1110;

c_state<=st0;

end

default:

begin

c_state<=st0;

end

endcase

end

end

endmodule

根据图8-32(a),按照图8-32(c)写出对应结构的VerilogHDL状态机。

modulefsmc(CLK,rese,ina,outa);

inputCLK,reset;

inputina;

outputouta;

regouta;

reg[1:

0]current_state;

reg[1:

0]next_state;

parameter[1:

0]st0=0;

parameter[1:

0]st1=1;

parameter[1:

0]st2=2;

parameter[1:

0]st3=3;

always@(current_stateC)

begin:

COM

case(current_state)

st0:

begin

if(ina=3'b101)outa<=4'b0010;

elseifina=3'b111outa<=4'b1100;

next_state<=st1;

end

st1:

begin

outa<=4'b1001;

if(ina==3'b000)

begin

next_state<=st1;

end

elseif(ina==3'b011)

begin

next_state<=st2;

end

end

st2:

begin

outa<=4'b1111;

if(ina==3'b100)

begin

next_state<=st2;

end

elseif(ina==3'b011)

begin

next_state<=st1;

end

elseif(ina/==3'b100)

begin

next_state<=st3;

end

end

st3:

begin

if(ina=3'b101)outa<=4'b1101;

elseifina=3'b011outa<=4'b1110;

next_state<=st0;

end

default:

begin

next_state<=st0;

end

endcase

end

always@(posedgeCLKornegedgereset)

begin:

REG

if(!

reset)

current_state<=st0;

else

current_state<=next_state;

end

endmodule