modelsim实验01计数器仿真实验步骤.docx

《modelsim实验01计数器仿真实验步骤.docx》由会员分享,可在线阅读,更多相关《modelsim实验01计数器仿真实验步骤.docx(10页珍藏版)》请在冰豆网上搜索。

modelsim实验01计数器仿真实验步骤

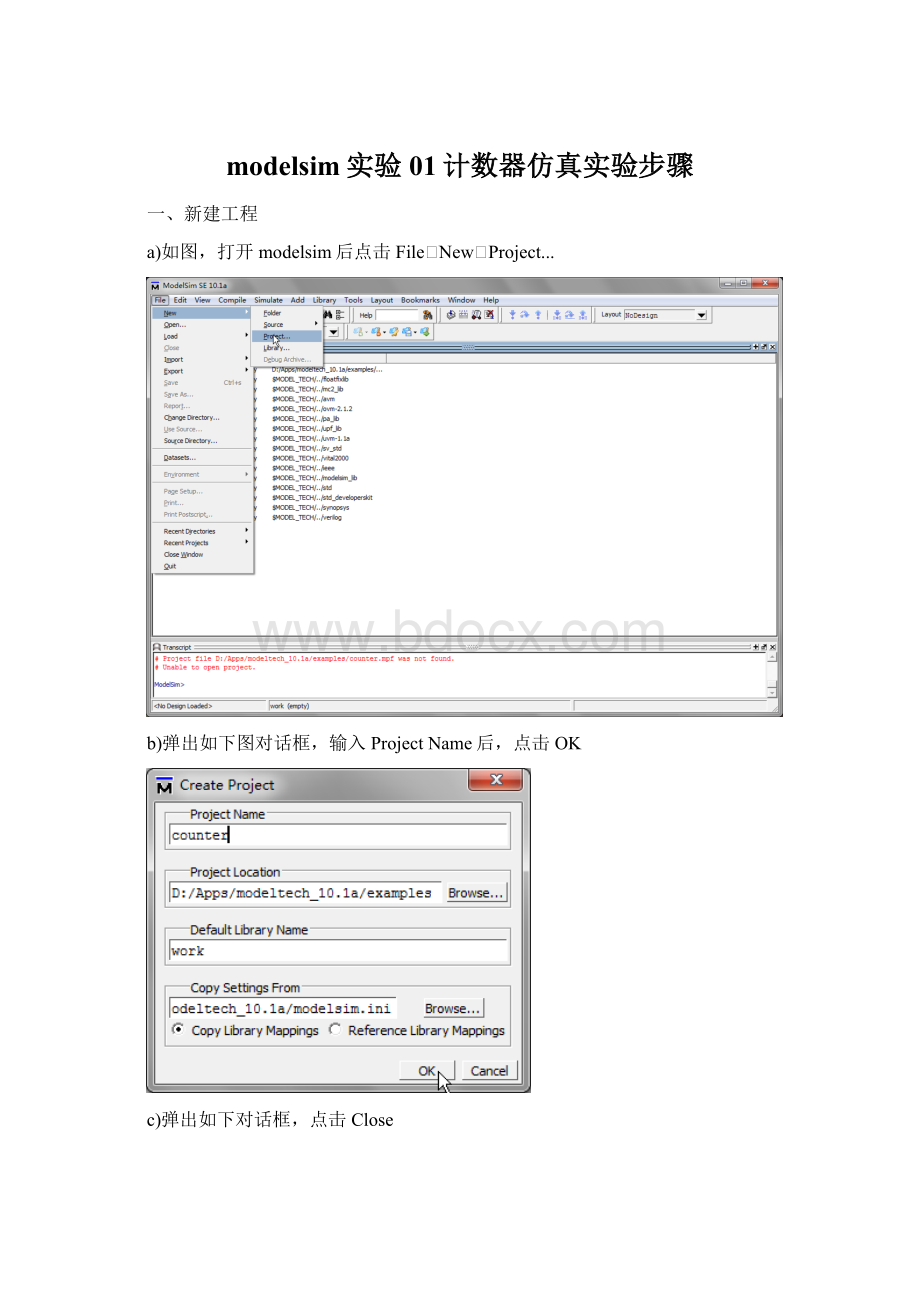

一、新建工程

a)如图,打开modelsim后点击FileàNewàProject...

b)弹出如下图对话框,输入ProjectName后,点击OK

c)弹出如下对话框,点击Close

二、在建好的工程中添加Verilog程序文件并进行编译

a)新建好的空工程如下图,在空白处右击,选择AddtoProjectàNewFile...

b)弹出如下对话框,将type选项改为Verilog,然后输入名称,点击OK

c)双击新建好的文件,在右侧的编辑框里输入程序

d)输入完成后,点击左上角工具栏的保存按钮

e)同样的步骤建立一个测试文件,然后在空白处右击选择CompileàCompileAll,进行编译

f)编译成功后,会出现如下变化,否则请检查程序重新编译

三、进行仿真

a)编译成功后,点击下方Library选项,在展开的work文件夹中右击刚才建立的测试文件,选择Simulate

b)此时弹出如下sim选项界面,在任意处右击选择AddtoàWaveàAllitemsinregion

c)添加波形完成后,会弹出右侧如下波形框,将上方工具栏中的时间长度100ps改为1ms,然后点击傍边的

run工具按钮

d)点击运行之后,出现如下波形图,通过调节工具栏上的放大、缩小、适应屏幕的按钮,以及拖动下方的进度条,就会出现合适的波形视图,如下

PS:

鼠标右击波形框中的测试文件名,选择RadixàUnsigned,可以将二进制改为十进制,如下图,可以看到,计数器随着时钟频率的上升沿,开始计数

四、附录Verilog计数器实验源程序

modulecounter3b(clk,cnt);//counter3b.v

inputclk;

outputreg[2:

0]cnt=3'b0;

always@(posedgeclk)begin

cnt<=cnt+1;

end

endmodule

`timescale1ns/10ps//counter3b_tb

modulecounter3b_tb();

regclk=0;

wire[2:

0]cnt;

always#100clk=~clk;

counter3bi1(.clk(clk),.cnt(cnt));

endmodule