毕业论文基于verilog电子时钟报告说明书.docx

《毕业论文基于verilog电子时钟报告说明书.docx》由会员分享,可在线阅读,更多相关《毕业论文基于verilog电子时钟报告说明书.docx(51页珍藏版)》请在冰豆网上搜索。

毕业论文基于verilog电子时钟报告说明书

一总体设计方案

1.设计原理及思路

1.1原理分析

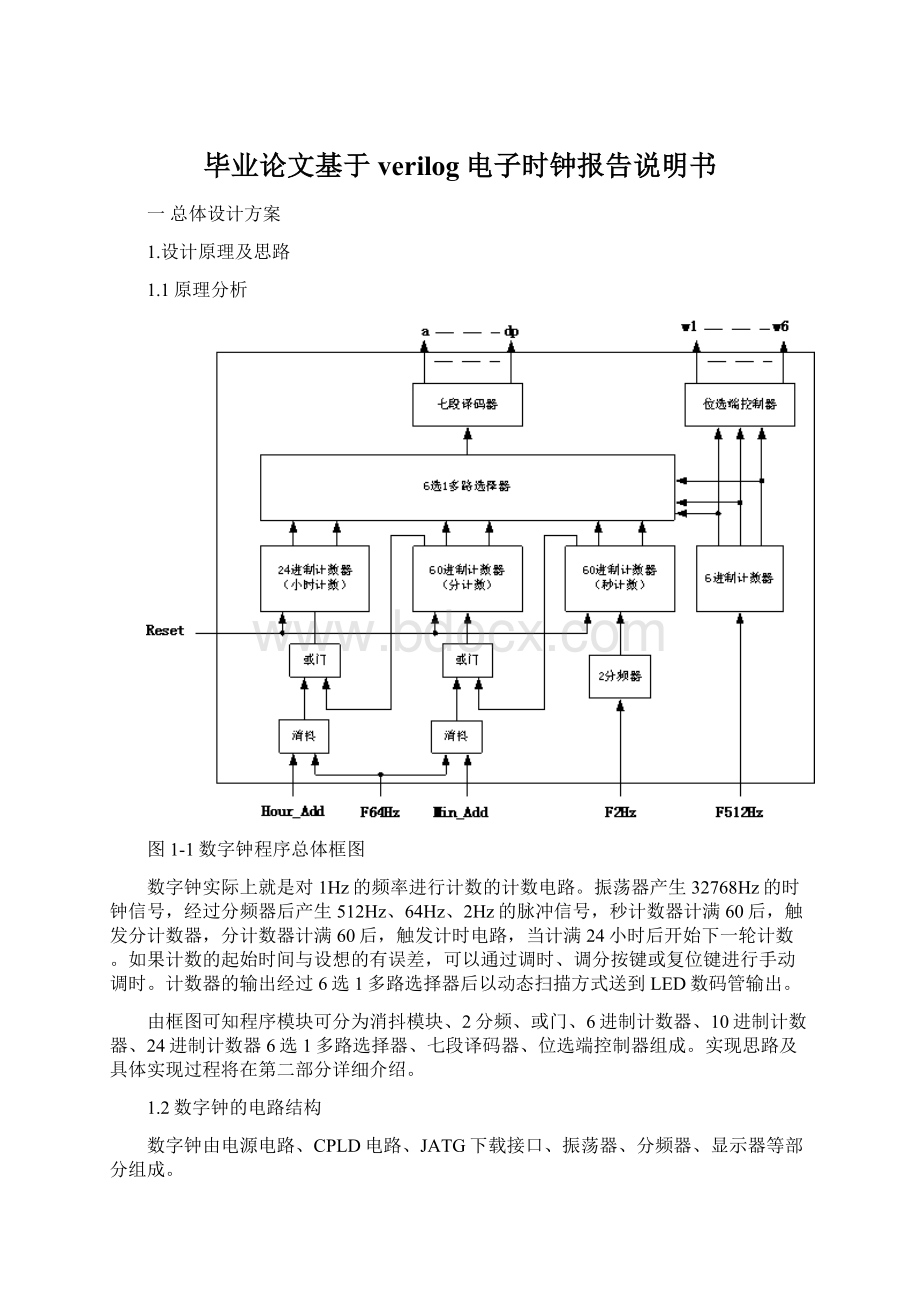

图1-1数字钟程序总体框图

数字钟实际上就是对1Hz的频率进行计数的计数电路。

振荡器产生32768Hz的时钟信号,经过分频器后产生512Hz、64Hz、2Hz的脉冲信号,秒计数器计满60后,触发分计数器,分计数器计满60后,触发计时电路,当计满24小时后开始下一轮计数。

如果计数的起始时间与设想的有误差,可以通过调时、调分按键或复位键进行手动调时。

计数器的输出经过6选1多路选择器后以动态扫描方式送到LED数码管输出。

由框图可知程序模块可分为消抖模块、2分频、或门、6进制计数器、10进制计数器、24进制计数器6选1多路选择器、七段译码器、位选端控制器组成。

实现思路及具体实现过程将在第二部分详细介绍。

1.2数字钟的电路结构

数字钟由电源电路、CPLD电路、JATG下载接口、振荡器、分频器、显示器等部分组成。

1.2.1电源电路

图1-2电源电路

电源电路通过USB接口输入5V电压,经三端稳压器输出3.3V工作电压用于电路中各元件的用电需求。

1.2.2JATG下载接口

图1-3JATG下载接口

通过USB-blaster将JATG接口与电脑相连,即可将编写好程序代码下载到开发板上进行功能验证。

1.2.3CPLD电路

该CPLD电路通过MAX3000AEPM3064ALC44-10N实现各模块的功能验证和综合。

在该芯片中有64个宏单元,44个可用引脚,载入程序后断电不消失,再次通电后仍执行上次载入的程序。

编写的VerilogHDL模块利用其中提供的触发器,逻辑门电路实现所编写程序的逻辑功能。

从原理图可看出芯片通过制定接口与电源电路、振荡电路、JATG下载接口及译码管相连综合实现其功能。

三个按键电路图分别表示RESET(复位键)、AD_Hour(调时按键)、AD_Min(调分按键)。

三个按键通过指定接口接入芯片通过程序中的消抖模块为计数器提供调时、调分、复位脉冲。

图1-4CPLD电路

1.2.4振荡和分频电路

图1-5振荡和分频电路

振荡和分频电路由晶振产生32768Hz的脉冲通过MC74WC4060芯片分频,产生F512Hz、F64Hz、F2Hz的脉冲信号,用于电路的计时脉冲和位选信号的产生。

1.2.5显示器

该数字钟以动态扫描方式输出。

计数器把输出信号送到六选一多路选择器中。

F512Hz的信号脉冲通过六进制计数器一个三位二进制数,把它作为六选一多路选择器和位选端控制器的输入。

六选一多路选择器根据要求把输出信号给到译码器。

位选端控制器产生一个六位二进制数决定哪个译码管亮。

由于扫描频率超出人眼识别能力,所以表面上看每个译码管是同时亮的。

图1-6显示器

二各模块说明

2.1消抖模块

2.1.1消抖模块原理

按键开关是各种电子设备不可或缺的人机接口。

在实际应用中,很大一部分的按键是机械按键。

在机械按键的触点闭合和断开时,都会产生抖动,为了保证系统能正确识别按键的开关,就必须对按键的抖动进行处理。

为了消除机械开关的抖动,可在开关与输出端点之间接人一个RS触发器,就能使输出端产生很清晰的阶跃信号。

2.1.2消抖模块程序代码

modulexiaodou(BJ_CLK,BUTTON_IN,BUTTON_OUT);

inputBJ_CLK;

inputBUTTON_IN;

outputBUTTON_OUT;

regBUTTON_IN_Q,BUTTON_IN_2Q,BUTTON_IN_3Q;

always@(posedgeBJ_CLK)

begin

BUTTON_IN_Q<=BUTTON_IN;

BUTTON_IN_2Q<=BUTTON_IN_Q;

BUTTON_IN_3Q<=BUTTON_IN_2Q;

end

wireBUTTON_OUT=BUTTON_IN_2Q|BUTTON_IN_3Q;

endmodule

仿真波形:

2.2或门

2.2.1或门原理

对于计时和计分电路既需要低位的进位信号,又需要手动按键调时,所以需要将两个信号通过或门后给到计时器和计分器。

对于或门,可用连续赋值语句C=A+B;实现。

2.2.2或门程序代码

modulehuo(in_1,in_2,huo_out);

inputin_1,in_2;

outputhuo_out;

assignhuo_out=in_1+in_2;

endmodule

仿真波形

2.3六进制计数器(不带进位端)

2.3.1六进制计数器(不带进位端)原理

该六进制计数器没有进位端,用于六选一多路选择器的输入,控制其输出计时器的计时信号。

同时它也作为位选端控制器的输入,决定哪个数码管亮。

六进制计数器采用时序逻辑电路,从0开始计时到5后归零,重新进行开始计时。

2.3.2六进制计数器(不带进位端)程序代码

moduleliujinzhi(clk512,cout);

outputcout;

inputclk512;

reg[2:

0]cout;

always@(posedgeclk512)

begin

if(clk512)

begin

if(cout==3'b101)

cout<=0;

else

cout<=cout+3'b1;

end

else

cout<=cout;

end

endmodule

仿真波形

2.42分频

2.4.12分频原理

该模块用于产生秒计数脉冲。

2分频即在每一个输入脉冲的上升沿(或下降沿)取反即可得到。

2.4.22分频程序代码

moduletwofenpin(clk2,clk_out);

outputclk_out;

inputclk2;

regclk_out;

always@(posedgeclk2)

begin

clk_out<=~clk_out;

end

endmodule

仿真波形:

2.5十进制计数器

2.5.1十进制计数器原理

十进制计数器作为秒计数器和分计数器的低位,具有进位输出端和异步复位端,复位信号为高电平有效。

它要求从0到9计数,到九清零重新计数。

采用时序逻辑电路。

设计时应考虑计数器能够进行级联。

2.5.2十进制计数器程序代码

moduleji10(clk_1,reset,jinwei_1,d1);

inputclk_1,reset;

output[3:

0]d1;

outputjinwei_1;

reg[3:

0]d1;

regjinwei_1;

always@(posedgeclk_1,posedgereset)

begin

if(reset)

begin

d1<=4'b0;

jinwei_1<=1'b0;

end

elseif(d1<4'd9)

begin

d1<=d1+4'b1;

jinwei_1<=1'b0;

end

elseif(d1==4'd9)

begin

d1<=4'b0;

jinwei_1<=1'b1;

end

end

endmodule

仿真波形:

2.6六进制计数器(含进位端)

2.6.1六进制计数器(含进位端)原理

该六进制计数器作为秒计数器和分计数器的高位,具有进位输出端和异步复位端,复位信号为高电平有效。

它要求从0到5计数,到5清零重新计数。

采用时序逻辑电路。

设计时应考虑计数器能够进行级联。

2.6.2六进制计数器(含进位端)程序代码

moduleliu(reset,clk_2,d2,jinwei_2);

outputd2,jinwei_2;

inputreset,clk_2;

reg[2:

0]d2;

regjinwei_2;

always@(posedgeclk_2orposedgereset)

begin

if(reset)

begin

d2<=3'b0;

jinwei_2<=1'b0;

end

elseif(d2==3'd5)

begin

d2<=3'b0;

jinwei_2<=1'b1;

end

else

begin

d2<=d2+3'b1;

jinwei_2<=1'b0;

end

end

endmodule

仿真波形:

2.7时计数器

2.7.1时计数器原理

该时计数器实际是一个24进制计数器,具有异步复位端,复位信号为高电平有效。

它要求从0到23计数,到23清零重新计数。

采用时序逻辑电路。

2.7.2时计数器程序代码

moduleshi(reset,d5,d6,dw_shi);

outputd5,d6;

inputreset,dw_shi;

reg[3:

0]d5;

reg[1:

0]d6;

reg[4:

0]count;

always@(posedgeresetorposedgedw_shi)

begin

if(reset)

begin

d5<=4'b0;

d6<=2'b0;

count<=5'b0;

end

elseif(count==5'd23)

begin

d5<=4'b0;

d6<=2'b0;

count<=5'b0;

end

else

begin

count=count+5'b1;

d5<=count%5'd10;

d6<=count/5'd10;

end

end

endmodule

仿真波形:

2.8六选一多路选择器

2.8.1六选一多路选择器原理

六选一多路选择器通过六进制计数器的输出信号控制实现了对计数器产生的脉冲信号的选择性输出。

加入此模块是为了实现数码管的动态扫描输出。

六选一多路选择器的输入是一个三位二进制数,输出是计时器、计分器、计秒器的高位或低位。

2.8.2六选一多路选择器程序代码

moduleliutoyi(cin,d1,d2,d3,d4,d5,d6,cout);

input[2:

0]cin;

input[3:

0]d1,d3,d5;

input[2:

0]d2,d4;

input[1:

0]d6;

output[3:

0]cout;

reg[3:

0]cout;

always@(cin)

case(cin)

3'b000:

cout<=d1;

3'b001:

cout<=d2;

3'b010:

cout<=d3;

3'b011:

cout<=d4;

3'b100:

cout<=d5;

3'b101:

cout<=d6;

endcase

endmodule

仿真波形:

2.9位选端控制器

2.9.1位选端控制器原理

该数字钟采用动态扫描方式输出,数码管每一时刻只有一个在亮,因为切换频率超过人眼识别能力,所以可以认为它们是同时亮的。

位选端控制器通过六进制计数器的输出决定哪一个数码管亮。

位选端控制器实际是一个3-6译码器。

当输入是三位2进制数时,输出为6位2进制数。

2.9.2位选端控制器程序代码

moduleweixuan(cin,v);

outputv;

input[3:

0]cin;

reg[5:

0]v;

always@(cin)

case(cin)

3'b000:

v<=6'b111110;

3'b001:

v<=6'b111101;

3'b010:

v<=6'b111011;

3'b011:

v<=6'b110111;

3'b100:

v<=6'b101111;

3'b101:

v<=6'b011111;

default:

v<=6'b111111;

endcase

endmodule

2.10七段译码器

2.10.1七段译码器原理

七段译码器是对输入的信号对应的位置进行编码,使其能显示出输入的数的值。

本文所介绍的译码器将小数点dp通过位拼接符将其与计数器的计数值组合,然后一同给到译码管,便于输出。

计时器低位的小数点要求常亮,即dp=1;计分器的低位小数点要求以1Hz的频率闪烁,可以让它以2分频的输出为值。

2.10.2七段译码器程序代码

moduleyimaguan(cin_7,cout_7,xuan_tong,

clk_dp);

input[3:

0]cin_7;

outputcout_7;

regdpy;

inputclk_dp;

input[2:

0]xuan_tong;

reg[7:

0]cout_7;

always@(xuan_tong)

case(xuan_tong)

3'b100:

dpy<=1'b1;

3'b010:

dpy<=clk_dp;

default:

dpy<=1'b0;

endcase

always@(cin_7)

case(cin_7)

4'b0000:

cout_7<={dpy,7'b0111111};

4'b0001:

cout_7<={dpy,7'b0000110};

4'b0010:

cout_7<={dpy,7'b1011011};

4'b0011:

cout_7<={dpy,7'b1001111};

4'b0100:

cout_7<={dpy,7'b1100110};

4'b0101:

cout_7<={dpy,7'b1101101};

4'b0110:

cout_7<={dpy,7'b1111101};

4'b0111:

cout_7<={dpy,7'b0000111};

4'b1000:

cout_7<={dpy,7'b1111111};

4'b1001:

cout_7<={dpy,7'b1101111};

endcase

endmodule

2.11综合模块

2.11.1综合模块原理

综合模块采用模块例化的方法实现。

2.11.2综合模块程序代码

modulezonghe(reset,hour_add,f64,min_add,f2,f512,z_out,z_wx);

inputreset,hour_add,f64,min_add,f2,f512;

output[7:

0]z_out;

output[5:

0]z_wx;

wiref_2,x1,x2,m1,f1,j1,j2,j3,j4,huo1,huo2;

wire[3:

0]dd1,dd3,dd5,qi1;

wire[2:

0]dd2,dd4,six1;

wire[1:

0]dd6;

xiaodouxd1(.BJ_CLK(f64),.BUTTON_IN(min_add),.BUTTON_OUT(x1));

xiaodouxd2(.BJ_CLK(f64),.BUTTON_IN(hour_add),.BUTTON_OUT(x2));

twofenpintfp1(.clk2(f2),.clk_out(f_2));

ji10ji101(.clk_1(f_2),.reset(reset),.jinwei_1(j1),.d1(dd1));

liul1(.reset(reset),.clk_2(j1),.d2(dd2),.jinwei_2(j2));

huoh1(.in_1(x1),.in_2(j2),.huo_out(huo1));

ji10ji102(.clk_1(huo1),.reset(reset),.jinwei_1(j3),.d1(dd3));

liul2(.reset(reset),.clk_2(j3),.d2(dd4),.jinwei_2(j4));

huoh2(.in_1(x2),.in_2(j4),.huo_out(huo2));

shish1(.reset(reset),.d5(dd5),.d6(dd6),.dw_shi(huo2));

liutoyili1(.cin(six1),.d1(dd1),.d2(dd2),.d3(dd3),.d4(dd4),.d5(dd5),.d6(dd6),.cout(qi1));

liujinzhiji1(.clk512(f512),.cout(six1));

weixuanw1(.cin(six1),.v(z_wx));

yimaguan(.cin_7(qi1),.cout_7(z_out),.xuan_tong(six1),.clk_dp(f_2));

endmodule

三总结

3.1硬件问题

焊接前要先弄清楚要焊接的元件,尤其是各种不同的电阻、电容。

焊接最需要注意的是焊接的温度和时间,我觉得焊接的时间最重要而且不太容易把握。

焊接的时间不能太短,那样焊点的温度就会太低,焊点融化不充分,很容易造成虚焊;而焊接时间长,则会使焊锡流淌,使元件过热,易于损坏,还容易烫坏电路板,同样会造成虚焊的现象。

焊接芯片时应该先焊接好底端插座,注意插座方向灯。

焊接完成后,焊点应呈现锥形,这才是好的焊点。

3.2程序过大

程序方面,由于EPM3064ALC44-10芯片只有64个宏单元,编写程序时有可能导致所需的宏单元数超过提供的数量,经过分析在处理小数点的时候,直接把其作为与其它段显示一起定义成八位变量,这样就会增加芯片内存消耗,但实际要求中只用到两个小数点,所以把这个小数点单独进行操作处理,大大减少了宏单元的利用,这样才能编译成功。

3.3赋值问题

初次实验,第一次按键不起作用。

原因是出在阻塞与非阻塞赋值上。

非阻塞赋值在过程块执行完后才赋值,由于变量初始值为0,所以第一次按键变量的值并未随之改变。

此时我们可以适当调整赋值顺序,将其改变为阻塞赋值。

即可解决这一问题。

参考文献

[978-7-81124-309-3]夏宇闻.Verilog数字系统设计教程.北京航空航天大学出版社,2008年6月,1—212页

EDA技术实验指导书河北大学2014年2月

附件:

本科生毕业设计(论文)管理规范

教务处

教育部办公厅关于加强普通高等学校

毕业设计(论文)工作的通知

教高厅〔2004〕14号

各省、自治区、直辖市教育厅(教委),新疆生产建设兵团教育局,有关部门(单位)教育司(局),部属各高等学校:

为了认真贯彻落实国务院批转的《2003-2007年教育振兴行动计划》,办好让人民满意的教育,切实把提高教育质量放在重中之重的位置,实现高等教育的持续健康发展,根据普通高等学校教学的实际情况和社会发展对人才培养工作的新要求,现就加强普通高等学校毕业设计(论文)工作有关要求通知如下:

一、要充分认识毕业设计(论文)环节的重要意义

毕业设计(论文)是实现培养目标的重要教学环节。

毕业设计(论文)在培养大学生探求真理、强化社会意识、进行科学研究基本训练、提高综合实践能力与素质等方面,具有不可替代的作用,是教育与生产劳动和社会实践相结合的重要体现,是培养大学生的创新能力、实践能力和创业精神的重要实践环节。

同时,毕业设计(论文)的质量也是衡量教学水平,学生毕业与学位资格认证的重要依据。

各省级教育行政部门(主管部门)和各类普通高等学校都要充分认识这项工作的必要性和重要性,制定切实有效措施,认真处理好与就业工作等的关系,从时间安排、组织实施等方面切实加强和改进毕业设计(论文)环节的管理,决不能降低要求,更不能放任自流。

二、要加强毕业设计(论文)阶段的教学管理工作

各类普通高等学校要进一步强化和完善毕业设计(论文)的规范化要求与管理,围绕选题、指导、中期检查、评阅、答辩等环节,制定明确的规范和标准。

毕业设计(论文)选题要切实做到与科学研究、技术开发、经济建设和社会发展紧密结合,要把一人一题作为选题工作的重要原则。

要根据不同专业学科特点和条件,研究建立有效的毕业设计(论文)质量管理模式和监控制度。

要重视研究和解决毕业设计(论文)工作中出现的新情况和新问题,积极采取措施,加大改革和工作力度,建立和完善校内外实习基地,高度重视毕业实习,不断提高毕业设计(论文)的整体水平。

三、要加强对毕业设计(论文)指导教师的管理工作

当前,要重视解决指导教师的数量和水平不适应毕业设计(论文)工作需要的问题。

要统筹教师队伍在毕业设计(论文)工作中的指导作用,确保指导教师数量的足额到位。

要通过建立制度和奖惩机制,从严治教,明确指导教师的职责,增强责任意识,使其集中精力完成毕业设计(论文)环节的各项教育教学任务。

提倡建立校内外指导教师相结合以校内教师为主体的指导教师队伍,加强在各类实践活动中对大学生综合能力的训练。

四、要加强毕业设计(论文)环节的学风建设

要通过各种途径和方式加强对学生的学风教育,使学生理解毕业实习、毕业设计(论文)的目的和意义,充分认识到做好毕业设计(论文)对自身思想品德、业务水平、工作能力和综合素质的提高具有深远的影响。

要建立严格的管理制度,倡导科学、求实、勇于创新、团结协作的优良学风,切实纠正毕业设计(论文)脱离实际的倾向,严肃处理弄虚作假、抄袭等不良行为。

五、高职高专学生的毕业设计要充分体现其职业性和岗位性

高职高专学生的毕业设计要与所学专业及岗位需求紧密结合,可以采取岗前实践和毕业综合训练等形式,由学校教师与企业的专业技术人员共同指导,结合企业的生产实际选题,确定训练内容和任务要求。

时间应不少于半年。

对高职高专学生要加强毕业设计环节的规范管理,加强过程监控,严格考核,采取评阅、答辩、实际操作等形式,检查和验收毕业设计成果。

六、要保证经费投入,努力改善毕业设计(论文)工作的基本条件

高等学校要通过多种形式和渠道加大对毕业设计(论文)工作的经费投入,采取切实措施改变当前对毕业设计(论文)工作投入不足的状况。

改善实习、实验及工作条件,为做好毕业设计(论文)工作创造良好的环境。

请各省级教育行政部门和有关主管部门加强对高等学校毕业设计(论文)工作的宏观管理和指导,认真研究和解决存在的实际问题,提出相应的政策措施。

要及时总结、宣传和推广先进经验,推动毕业设计(论文)工作质量的不断提高。

教育部将在适当时候开展专项检查,在今后的教学评估工作中也将加大对学校毕业设计(论文)环节的考察力度,并将其列为确定评估结论的关键指标。

请认真贯彻执行本通知精神,并将执行中的有关情况及时报告我部高等教育司。

教育部办公厅

二○○四年四月八日

毕业设计(论文)工作管理规程

毕业设计(论文)是本科生培养过程中重要的组成部分,是毕业前学生进行全面综合训练,培养学生综合素质、创新意识和创新能力的一个重要的实践性教学环节,是对学生知识、能力和素质的综合考核。

为了规范我校毕业设计(论文)工作,全面提高毕业设计(论文)质量,特制定本规程。

一、基本要求

毕业设计(论文)应从以下几方面培养学生的能力:

1、综合运用知识能力。

2、文献资料查阅应用能力。

3、研究方案的设计(实验)能力。

4、研究方法和手段(计算机等)的运用能力。

5、技术经济分析能力。

6、外文应用能力。

7、创新能力。

二、工作程序

l、确定题目

每年11月底前,各大学向学生公布下届毕业生课题方向和题目,并说明题目来源、内容、难易程度、工作量大小及所具备的条件等。

各大学可采取学生自选与分配相结合方法,使每位学生选定一个题目,要求一人一题。

2、指定指导教师

大学根据学生选题方向指定指导教师,指导教师确定后,安排指导教师与学生见面。

指导教师向学生下达毕业设计(论文)任务书,并提出具体要求。

毕业设计(论文)开始前,各大学必须进行毕业设计(论文)动员。

组织师生学习本管理规程,明确职责及要求,安排必要的指导培训和专题讲