Vivado实验01流水灯仿真实验及下板步骤.docx

《Vivado实验01流水灯仿真实验及下板步骤.docx》由会员分享,可在线阅读,更多相关《Vivado实验01流水灯仿真实验及下板步骤.docx(32页珍藏版)》请在冰豆网上搜索。

Vivado实验01流水灯仿真实验及下板步骤

Vivado实验01-流水灯仿真实验及下板步骤

一、新建工程

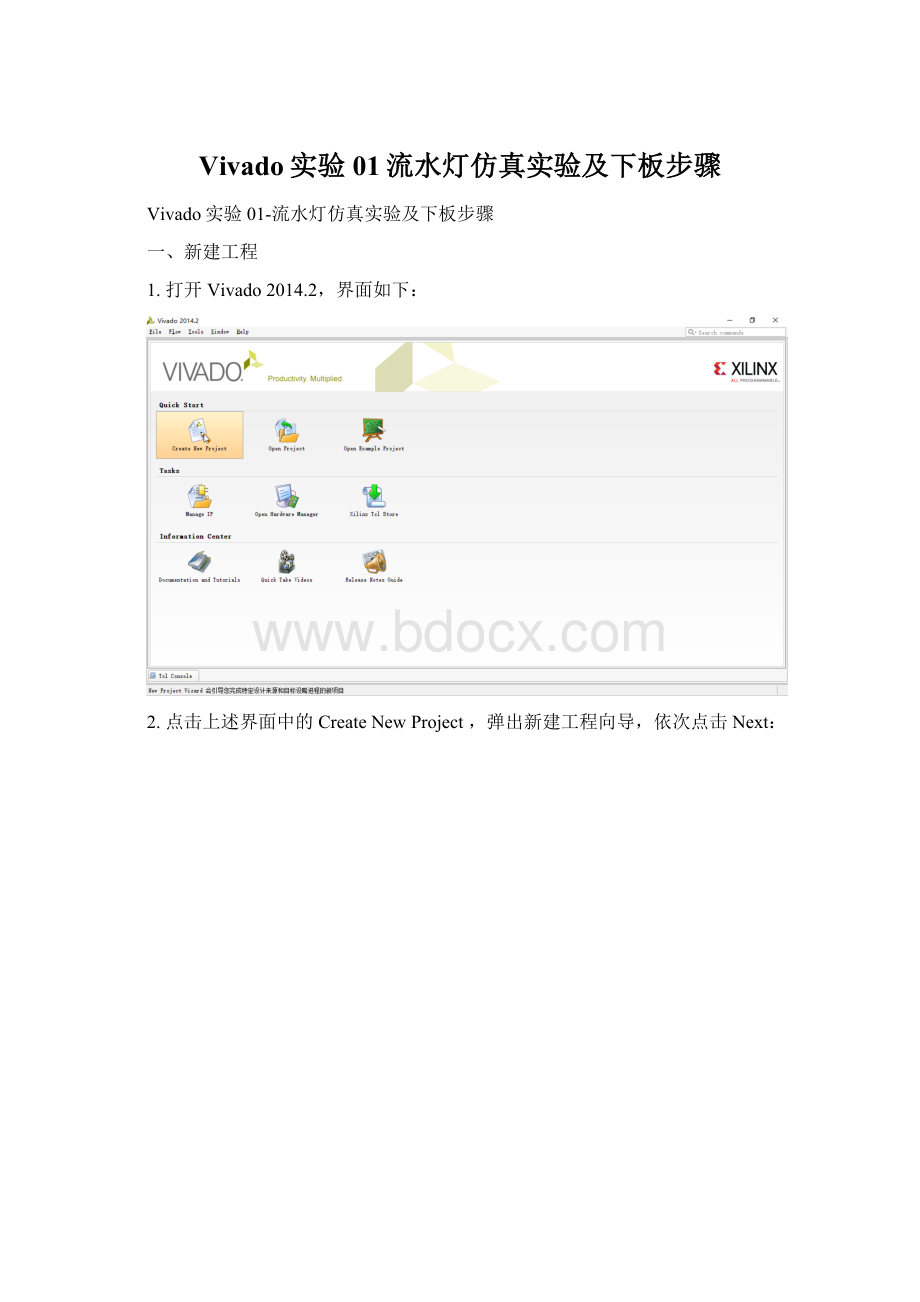

1.打开Vivado2014.2,界面如下:

2.点击上述界面中的CreateNewProject,弹出新建工程向导,依次点击Next:

1.如下图,点击输入设计程序:

2.如下图,选择新建文件,依次创建4个verilog文件,文件名依次为:

clock_div;ctc;s_74ls138;led_light

注意:

最后一个为顶层文件,文件名与项目的文件名相同,且所有名称中不能出现中文、空格和符号

3.双击打开,然后输入依次设计程序:

注意:

每次输入一个设计程序最好保存一次,保存操作如下图

然后重复步骤,将4个设计程序依次输入保存

4.添加仿真文件:

5.进入仿真,点击RunSimulation→RunBehavioralSimulation

6.调节缩小按钮,将间隔调节为1s,方便观察实验结果,然后点击上方运行按钮进行仿真,接着点击弹出的信息条的Background将其隐藏,即可看到完整的仿真循环结果

7.仿真结果如下图:

三、下板操作

1.仿真完成后,先关闭仿真,操作如下图:

2.接着进行下一步综合,如下图操作:

3.综合处成功后,要进行实现操作,如下图:

4.实现成功后进行下一步,管脚约束,操作如下图:

注意:

此处需用到板卡手册,请使用老师群共享的文件“Nexys4-DDR_rm”,此为配适的较新版本,否则可能出现错误

5.约束文件生成后,更改为I/O操作界面:

6.此处不能使用默认电压值,否则会报错,更改电压值为3.3V,然后将时钟引脚接至E3,复位引脚接至C12,y0至y7输出接至V16、T15、U14、T16、V15、V14、V15、V11,引脚的连接方式有三种,所有操作如下图:

7.约束完成后,关闭保存:

8.在源程序文档中的约束文件中可以看到刚才操作生成的约束文件,也可以直接在约束文件中直接输入代码来完成管教的约束和更改:

9.约束完成后,生成编程文件:

10.此时需要连接板卡到电脑,在此之前需要对板卡进行设置:

11.连接电脑,打开电源开关,等待驱动安装完成后,打开HardwareManager→Openanewhardwaretarget→在跳出的提示框中一直点击Next,不需更改,直到Finish→Programdevice→选择板卡xc7a100t_0→在跳出的选择框中点击ok,这时就可以观察到仿真结果中的流水灯效果,以上为识别板卡到把编程文件下载到板卡的无脑操作,具体步骤请看下图:

12.观察到板卡上的实验结果正确后,实验到此结束,关闭板卡的电源开关,拔出板卡,以上。

四、附录Verilog流水灯实验源程序

第一步设计电路

一个分频器

一个3位计数器

一个38译码器

第二步设计各元器件的verilog代码;分频器

moduleclock_div(clk,clk_sys);

inputclk;

outputclk_sys;

regclk_sys=0;

reg[25:

0]div_counter=0;

always@(posedgeclk)begin

if(div_counter>50000000)begin

clk_sys<=~clk_sys;

div_counter<=0;

end

elsebegin

div_counter<=div_counter+1;

end

end

endmodule

第二步设计各元器件的verilog代码;3位计数器

modulectc(clk,reset,count);

inputclk,reset;

outputreg[2:

0]count;

always@(posedgeclkornegedgereset)begin

if(reset==0)begin

count=0;

end

elsebegin

if(count==0)

count=7;

elsebegin

count=count-1;

end

end

end

endmodule

第二步设计各元器件的verilog代码;38译码器

modules_74ls138(Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7,A0,A1,A2,Enable);

inputA0,A1,A2,Enable;

outputregY0,Y1,Y2,Y3,Y4,Y5,Y6,Y7;

always@(A0orA1orA2orEnable)begin

if(!

Enable)

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0000_0000;

elsebegin

case({A2,A1,A0})

3'b000:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0000_0001;

3'b001:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0000_0010;

3'b010:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0000_0100;

3'b011:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0000_1000;

3'b100:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0001_0000;

3'b101:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0010_0000;

3'b110:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0100_0000;

3'b111:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b1000_0000;

default:

{Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0}<=8'b0000_0000;

endcase

end

end

endmodule

第三步设计一个总电路(顶层文件)

moduleled_light(clock,reset,y0,y1,y2,y3,y4,y5,y6,y7);

inputclock,reset;

outputy0,y1,y2,y3,y4,y5,y6,y7;

wireclk_sys;

wire[2:

0]count;

clock_divu0(.clk(clock),.clk_sys(clk_sys));

s_74ls138u1(.A0(count[0]),.A1(count[1]),.A2(count[2]),.Enable(reset),.Y0(y0),.Y1(y1),.Y2(y2),.Y3(y3),.Y4(y4),.Y5(y5),.Y6(y6),.Y7(y7));

ctcu2(.clk(clk_sys),.reset(reset),.count(count));

endmodule

第四步设计一个仿真文件

moduleled_sim();

regclock=0;

regreset=0;

wirey0;

wirey1;

wirey2;

wirey3;

wirey4;

wirey5;

wirey6;

wirey7;

led_lightyyt(.clock(clock),.reset(reset),.y0(y0),.y1(y1),.y2(y2),.y3(y3),.y4(y4),.y5(y5),.y6(y6),.y7(y7));

initialbegin

#500000005reset=1;

end

always#5clock=~clock;

endmodule

第六步设计综合,管脚约束

第七步生成编程文件

第八步下载