AT89S51单片机.docx

《AT89S51单片机.docx》由会员分享,可在线阅读,更多相关《AT89S51单片机.docx(29页珍藏版)》请在冰豆网上搜索。

AT89S51单片机

AT89S51

AT89S51单片机的硬件组成

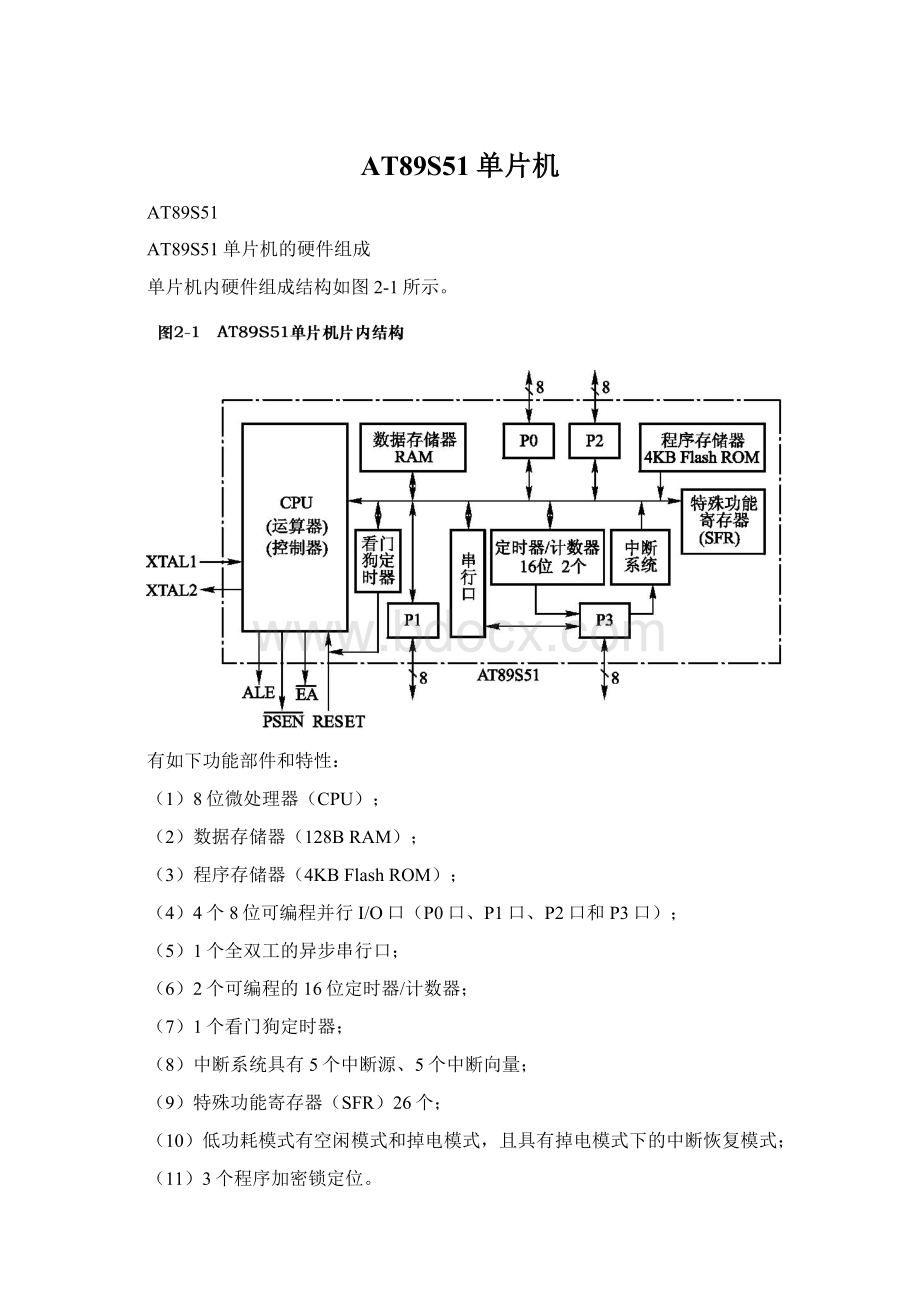

单片机内硬件组成结构如图2-1所示。

有如下功能部件和特性:

(1)8位微处理器(CPU);

(2)数据存储器(128BRAM);

(3)程序存储器(4KBFlashROM);

(4)4个8位可编程并行I/O口(P0口、P1口、P2口和P3口);

(5)1个全双工的异步串行口;

(6)2个可编程的16位定时器/计数器;

(7)1个看门狗定时器;

(8)中断系统具有5个中断源、5个中断向量;

(9)特殊功能寄存器(SFR)26个;

(10)低功耗模式有空闲模式和掉电模式,且具有掉电模式下的中断恢复模式;

(11)3个程序加密锁定位。

与AT89C51相比,AT89S51有更突出的优点:

(1)增加在线可编程功能ISP(InSystemProgram),字节和页编程,现场程序调试和修改更加方便灵活;

(2)数据指针增加到两个,方便了对片外RAM的访问过程;

(3)增加了看门狗定时器,提高了系统的抗干扰能力;

(4)增加断电标志;

(5)增加掉电状态下的中断恢复模式。

单片机内各功能部件通过片内单一总线连接而成(见图2-1),基本结构依旧是CPU加上外围芯片的传统微机结构。

CPU对各种功能部件的控制是采用特殊功能寄存器(SFR,SpecialFunctionRegister)的集中控制方式。

单片机内部件功能

1)CPU(微处理器)

8位的CPU,与通用CPU基本相同,同样包括了运算器和控制器两大部分,还有面向控制的位处理功能。

2)数据存储器(RAM)

片内为128B(52子系列为256B),片外最多可扩64KB。

片内128B的RAM以高速RAM的形式集成,可加快单片机运行的速度和降低功耗。

3)程序存储器(FlashROM)

片内集成有4KB的Flash存储器(AT89S52则为8KB;AT89C55片内20KB),如片内容量不够,片外可外扩至64KB。

4)中断系统

具有5个中断源,2级中断优先权。

5)定时器/计数器

2个16位定时器/计数器(52子系列有3个),4种工作方式。

6)1个看门狗定时器WDT

当CPU由于干扰使程序陷入死循环或跑飞时,WDT可使程序恢复正常运行。

7)串行口

1个全双工的异步串行口,4种工作方式。

可进行串行通信,扩展并行I/O口,还可与多个单片机构成多机系统。

8)P0口、P1口、P2口和P3口

4个8位并行I/O口。

9)特殊功能寄存器(SFR)

26个,对片内各功能部件管理、控制和监视。

是各个功能部件的控制寄存器和状态寄存器,映射在片内RAM区80H~FFH内。

AT89S51完全兼容AT89C51,在充分保留原来软、硬件条件下,完全可以用AT89S51直接代换。

AT89S51的引脚功能

AT89S51与51系列中各种型号芯片的引脚互相兼容。

目前多采用40只引脚双列直插,如图2-2所示。

引脚按其功能可分为如下3类:

1)电源及时钟引脚—VCC、VSS;XTAL1、XTAL2。

2)控制引脚—、ALE/、/VPP、RST(RESET)

3)I/O口引脚——P0、P1、P2、P3,为4个8位I/O口

电源及时钟引脚

1.电源引脚

1)VCC(40脚):

+5V电源。

2)VSS(20脚):

数字地。

2.时钟引脚

1)XTAL1(19脚):

片内振荡器反相放大器和时钟发生器电路输入端。

用片内振荡器时,该脚接外部石英晶体和微调电容。

外接时钟源时,该脚接外部时钟振荡器的信号。

2)XTAL2(18脚):

片内振荡器反相放大器的输出端。

当使用片内振荡器,该脚连接外部石英晶体和微调电容。

当使用外部时钟源时,本脚悬空。

3.控制引脚

1)RST(RESET,9脚)

复位信号输入,在引脚加上持续时间大于2个机器周期的高电平,可使单片机复位。

正常工作,此脚电平应≤0.5V。

当看门狗定时器溢出输出时,该脚将输出长达96个时钟振荡周期的高电平。

2)/VPP(EnableAddress/VoltagePulseofPrograming,31脚)

引脚第一功能:

外部程序存储器访问允许控制端。

=1:

在PC值不超出0FFFH(即不超出片内4KBFlash存储器的地址范围)时,单片机读片内程序存储器(4KB)中的程序,但PC值超出0FFFH(即超出片内4KBFlash地址范围)时,将自动转向读取片外60KB(1000H-FFFFH)程序存储器空间中的程序。

=0:

只读取外部的程序存储器中的内容,读取的地址范围为0000H~FFFFH,片内的4KBFlash程序存储器不起作用。

VPP:

引脚第二功能,对片内Flash编程,接编程电压。

3)ALE/(AddressLatchEnable/PROGramming,30脚)

ALE为CPU访问外部程序存储器或外部数据存储器提供地址锁存信号,将低8位地址锁存在片外的地址锁存器中。

此外,单片机正常运行时,ALE端一直有正脉冲信号输出,此频率为时钟振荡器频率fosc的1/6。

可用作外部定时或触发信号。

注意,每当AT89S51访问外部RAM时(执行MOVX类指令),要丢失一个ALE脉冲。

如需要,可将特殊功能寄存器AUXR(地址为8EH,将在后面介绍)的第0位(ALE禁止位)置1,来禁止ALE操作,但执行访问外部程序存储器或外部数据存储器指令“MOVC”或“MOVX”时,ALE仍然有效。

即ALE禁止位不影响对外部存储器的访问。

:

引脚第二功能,对片内Flash编程,为编程脉冲输入脚。

4)(ProgramStrobeENable,29脚)

片外程序存储器读选通信号,低电平有效。

并行I/O口引脚

1)P0口:

8位,漏极开路的双向I/O口

当外扩存储器及I/O接口芯片时,P0口作为低8位地址总线及数据总线的分时复用端口。

P0口也可用作通用的I/O口,需加上拉电阻,这时为准双向口。

作为通用I/O输入,应先向端口写入1。

可驱动8个LS型TTL负载。

2)P1口:

8位,准双向I/O口,具有内部上拉电阻。

准双向I/O口,作为通用I/O输入时,应先向端口锁存器写1。

P1口可驱动4个LS型TTL负载。

P1.5/MOSI、P1.6/MISO和P1.7/SCK

可用于对片内Flash存储器串行编程和校验,它们分别是串行数据输入、输出和移位脉冲引脚。

3)P2口:

8位,准双向I/O口,具有内部上拉电阻。

当AT89S51扩展外部存储器及I/O口时,P2口作为高8位地址总线用,输出高8位地址。

P2口也可作为普通的I/O口使用。

当作为通用I/O输入时,

应先向端口输出锁存器写1。

P2口可驱动4个LS型TTL负载。

4)P3口:

8位,准双向I/O口,具有内部上拉电阻。

可作为通用的I/O口使用。

作为通用I/O输入,应先向端口输出锁存器写入1。

可驱动4个LS型TTL负载。

P3口还可提供第二功能。

第二功能定义见表2-1,应熟记。

表2-1P3口的第二功能定义

引脚

第二功能

说明

P3.0

RXD

串行数据输入口

P3.1

TXD

串行数据输出口

P3.2

INT0

外部中断0输入

P3.3

INT1

外部中断1输入

P3.4

T0

定时器0外部计数输入

P3.5

T1

定时器1外部计数输入

P3.6

WR

外部数据存储器写选通输出

P3.7

RD

外部数据存储器读写通输出

综上所述,P0口可作为总线口,为双向口。

作为通用的I/O口使用时,为准双向口,这时需加上拉电阻。

P1口、P2口、P3口均为准双向口。

注意:

准双向口与双向口的差别。

准双向口仅有两个状态。

而P0口作为总线使用,口线内无上拉电阻,处于高阻“悬浮”态。

故P0口为双向三态I/O口。

为什么P0口要有高阻“悬浮”态?

准双向I/O口则无高阻的“悬浮”状态。

另外,准双向口作通用I/O的输入口使用时,一定要向该口先写入“1”。

以上的准双向口与双向口的差别,读者在阅读2.5节后,将会有深刻的理解。

至此,40个引脚已介绍完,应熟记每一引脚功能对应用系统硬件电路设计十分重要。

AT89S51的CPU(p41)

由图2-1可见,CPU由运算器和控制器构成。

一、运算器

对操作数进行算术、逻辑和位操作运算。

主要包括算术逻辑运算单元ALU、累加器A、位处理器、程序状态字寄存器PSW及两个暂存器等。

1.算术逻辑运算单元ALU

可对8位变量逻辑运算(与、或、异或、循环、求补和清零),还可算术运算(加、减、乘、除)

ALU还有位操作功能,对位变量进行位处理,如置“1”、清“0”、求补、测试转移及逻辑“与”、“或”等。

2.累加器A

使用最频繁的寄存器,可写为Acc。

“A”与“Acc”书写上的差别,将在第3章介绍。

作用如下:

1)ALU单元的输入数据源之一,又是ALU运算结果存放单元。

2)数据传送大多都通过累加器A,相当于数据的中转站。

为解决“瓶颈堵塞”问题,AT89S51增加了一部分可以不经过累加器的传送指令。

A的进位标志Cy是特殊的,因为它同时又是位处理机的位累加器

3.程序状态字寄存器PSW

PSW(ProgramStatusWord)位于片内特殊功能寄存器区,字节地址为D0H。

包含了程序运行状态的信息,其中4位保存当前指令执行后的状态,供程序查询和判断。

格式如图2-3所示。

图2-3PSW的格式

PSW中各个位的功能:

1)Cy(PSW.7)进位标志位

可写为C。

在算术和逻辑运算时,若有进位/借位,Cy=1;否则,Cy=0。

在位处理器中,它是位累加器。

2)Ac(PSW.6)辅助进位标志位

在BCD码运算时,用作十进位调整。

即当D3位向D4位产生进位或借位时,Ac=1;否则,Ac=0。

3)F0(PSW.5)用户设定标志位

由用户使用的一个状态标志位,可用指令来使它置1或清0,控制程序的流向。

用户应充分利用。

4)RS1、RS0(PSW.4、PSW.3)4组工作寄存器区选择

选择片内RAM区中的4组工作寄存器区中的某一组为当前工作寄存区见表2-2。

5)OV(PSW.2)溢出标志位

当执行算术指令时,用来指示运算结果是否产生溢出。

如果结果产生溢出,OV=1;否则,OV=0。

6)PSW.1位

保留位

7)P(PSW.0)奇偶标志位

指令执行完,累加器A中“1”的个数是奇数还是偶数。

P=1,表示A中“1”的个数为奇数。

P=0,表示A中“1”的个数为偶数。

此标志位对串行通信有重要的意义,常用奇偶检验的方法来检验数据串行传输的可靠性。

表2-2RS1RS0与四组寄存器区的对应关系

RS1RS0

所选的四组寄存器

00

0区(内部RAM地址00H-07H)

01

1区(内部RAM地址08H-0FH)

10

2区(内部RAM地址10H-17H)

11

3区(内部RAM地址18H-1FH)

二、控制器

任务识别指令,并根据指令的性质控制单片机各功能部件,从而保证单片机各部分能自动协调地工作。

控制器包括:

程序计数器、指令寄存器、指令译码器、定时及控制逻辑电路等。

功能是控制指令的读入、译码和执行,从而对各功能部件进行定时和逻辑控制。

程序计数器PC是一个独立的16位计数器,不可访问。

单片机复位时,PC中内容为0000H,从程序存储器0000H单元取指令,开始执行程序。

PC工作过程是:

CPU读指令时,PC的内容作为所取指令的地址,程序存储器按此地址输出指令字节,同时PC自动加1。

PC中内容变化轨迹决定程序流程。

当顺序执行程序时自动加1;执行转移程序或子程序、中断子程序调用时,自动将其内容更改成所要转移的目的地址。

PC的计数宽度决定了程序存储器的地址范围。

PC为16位,故可对64KB(=216B)寻址。

基本工作方式:

1)程序计数器自动加1

2)执行有条件或无条件转移指令时,程序计数器将被置入新的数值,从而使程序的流向发生变化。

3)执行子程序调用或中断调用时完成下列操作:

①PC的当前值保护

②将子程序入口地址或中断向量的地址送入PC。

PC变化的轨迹决定程序的流程。

AT89S51存储器的结构

存储器的结构特点之一是将程序存储器和数据存储器分开(哈佛结构),并有各自的访问指令。

存储器空间可分为4类。

1.程序存储器空间

片内和片外两部分。

片内4KBFlash,编程和擦除完全是电气实现。

可用通用编程器对其编程,也可在线编程。

当片内4KBFlash存储器不够用时,可片外扩展,最多可扩展至64KB程序存储器。

2.数据存储器空间

片内与片外两部分。

片内有128BRAM(52子系列为256B)。

片内RAM不够用时,在片外可扩展至64KBRAM。

3.特殊功能寄存器SFR(SpecialFunctionRegister)

片内各功能部件的控制寄存器及状态寄存器。

SFR综合反映了整个单片机基本系统内部实际的工作状态及工作方式。

4.位地址空间

共有211个可寻址位,构成了位地址空间。

它们位于内部RAM(共128位)和特殊功能寄存器区(共83位)中。

程序存储器空间

存放程序和表格之类的固定常数。

片内为4KB的Flash,地址为0000H~0FFFH。

16位地址线,可外扩的程序存储器空间最大为64KB,地址为0000H~FFFFH。

使用时应注意以下问题:

1)分为片内和片外两部分,访问片内的还是片外的程序存储器,由引脚电平确定。

=1时,CPU从片内0000H开始取指令,当PC值没有超出0FFFH时,只访问片内Flash存储器,当PC值超出0FFFH自动转向读片外程序存储器空间1000H~FFFFH内的程序。

=0时,只能执行片外程序存储器(0000H~FFFFH)中的程序。

不理会片内4KBFlash存储器。

2)程序存储器某些固定单元用于各中断源中断服务程序入口。

64KB程序存储器空间中有5个特殊单元分别对应于5个中断源的中断入口地址,见表2-3。

通常这5个中断入口地址处都放一条跳转指令跳向对应的中断服务子程序,而不是直接存放中断服务子程序。

表2-3五个中断源的中断入口地址

中断源

入口地址

外部中断0

0003H

定时器T0

000BH

外部中断1

0013H

定时器T1

001BH

串行口

0023H

数据存储器空间

片内与片外两部分。

1.片内数据存储器

片内数据存储器(RAM)共128个单元,字节地址为00H~7FH。

图2-4为片内数据存储器的结构。

00H~1FH的32个单元是4组通用工作寄存器区,每区包含8B,为R7~R0。

可通过指令改变RS1、RS0两位来选择。

20H~2FH的16个单元的128位可位寻址,也可字节寻址。

30H~7FH的单元只能字节寻址,用作存数据以及作为堆栈区。

2.片外数据存储器

当片内128B的RAM不够用时,需外扩,最多可外扩64KB的RAM。

注意,片内RAM与片外RAM两个空间是相互独立的,片内RAM与片外RAM的低128B的地址是相同的,但由于使用的是不同的访问指令,所以不会发生冲突。

特殊功能寄存器(SFR)

采用特殊功能寄存器集中控制各功能部件。

特殊功能寄存器映射在片内RAM的80H~FFH区域中,共26个。

表2-4SFR的名称及其分布。

有些还可位寻址,位地址见表2-4。

与AT89C51相比,新增5个SFR:

DP1L、DP1H、AUXR、AUXR1和WDTRST,已在表2-4中标出。

凡是可位寻址的SFR,字节地址末位只能是0H或8H。

另外,若读/写未定义单元,将得到一个不确定的随机数。

下面介绍某些SFR,余下的SFR将在后面介绍。

1.堆栈指针SP

指示堆栈顶部在内部RAM块中的位置。

堆栈结构—向上生长型。

单片机复位后,SP为07H,使得堆栈实际上从08H单元开始,由于08H~1FH单元分别是属于1~3组的工作寄存器区,最好在复位后把SP值改置为60H或更大的值,避免堆栈与工作寄存器冲突。

堆栈是为子程序调用和中断操作而设,主要用来保护断点和现场。

1)保护断点。

无论是子程序调用操作还是中断服务子程序调用,最终都要返回主程序。

应预先把主程序的断点在堆栈中保护起来,为程序正确返回做准备。

2)现场保护。

执行子程序或中断服务子程序时,要用到一些寄存器单元,会破坏原有内容。

要把有关寄存器单元的内容保存起来,送入堆栈,这就是所谓的“现场保护”。

两种操作:

数据压入(PUSH)堆栈,数据弹出(POP)堆栈。

数据压入堆栈,SP自动加1;数据弹出堆栈,SP自动减1。

2.寄存器B

为执行乘法和除法而设。

在不执行乘、除法操作的情况下,可把它当作一个普通寄存器来使用。

乘法,两乘数分别在A、B中,执行乘法指令后,乘积在BA中

除法,被除数取自A,除数取自B,商存放在A中,余数存B中。

3.AUXR寄存器

AUXR是辅助寄存器,其格式如图2-5所示:

其中:

DISALE:

ALE的禁止/允许位。

0:

ALE有效,发出脉冲;

1:

ALE仅在执行MOVC和MOVX类指令时有效,不访问外部存储器时,ALE不输出脉冲信号。

DISRTO:

禁止/允许WDT溢出时的复位输出。

0:

WDT溢出时,在RST引脚输出一个高电平脉冲;

1:

RST引脚仅为输入脚。

WDIDLE:

WDT在空闲模式下的禁止/允许位。

0:

WDT在空闲模式下继续计数;

1:

WDT在空闲模式下暂停计数。

4.数据指针DPTR0和DPTR1

双数据指针寄存器,便于访问数据存储器。

DPTR0:

AT89C51单片机原有的数据指针;

DPTR1:

新增加的数据指针。

AUXR1的DPS位用于选择两个数据指针。

当DPS=0时,选用DPTR0;当DPS=1时,选用DPTR1。

数据指针可作为一个16位寄存器来用,也可作为两个独立的8位寄存器DP0H(或DP1H)和DP0L(或DP1L)来用。

5.AUXR1寄存器

AUXR1是辅助寄存器,格式如图2-6所示:

DPS:

数据指针寄存器选择位。

0:

选择数据指针寄存器DPTR0;

1:

选择数据指针寄存器DPTR1。

6.看门狗定时器WDT

WDT包含一个14位计数器和看门狗定时器复位寄存器——(WDTRST)。

当CPU由于干扰,程序陷入死循环或跑飞状态时,WDT提供了一种使程序恢复正常运行的有效手段。

有关WDT在抗干扰设计中的应用以及低功耗模式下运行的状态,将在相应的章节中具体介绍。

上面介绍的特殊功能寄存器,除了前两个SP和B以外,其余的均为AT89S51在AT89C51基础上新增加的SFR。

位地址空间

211个寻址位的位地址,位地址范围为00H~FFH,其中00H~7FH这128位处于片内RAM字节地址20H~2FH单元中,如表2-5所示。

其余的83个可寻址位分布在特殊功能寄存器SFR中,见表2-6。

可被位寻址的特殊寄存器有11个,共有位地址88个,5个位未用,其余83个位的位地址离散地分布于片内数据存储器区字节地址为80H~FFH的范围内,其最低的位地址等于其字节地址,且其字节地址的末位都为0H或8H。

特殊功能

寄存器

位地址

字节地址

D7

D6

D5

D4

D3

D2

D1

D0

B

F7H

F6H

F5H

F4H

F3H

F2H

F1H

F0H

F0H

Acc

E7H

E6H

E5H

E4H

E3H

E2H

E1H

E0H

E0H

PSW

D7H

D6H

D5H

D4H

D3H

D2H

D1H

D0H

D0H

IP

—

—

—

BCH

BBH

BAH

B9H

B8H

B8H

P3

B7H

B6H

B5H

B4H

B3H

B2H

B1H

B0H

B0H

IE

AFH

—

—

ACH

ABH

AAH

A9H

A8H

A8H

P2

A7H

A6H

A5H

A4H

A3H

A2H

A1H

A0H

A0H

SCON

9FH

9EH

9DH

9CH

9BH

9AH

99H

98H

98H

P1

97H

96H

95H

94H

93H

92H

91H

90H

90H

TCON

8FH

8EH

8DH

8CH

8BH

8AH

89H

88H

88H

P0

87H

86H

85H

84H

83H

82H

81H

80H

80H

作为对AT89S51存储器结构的总结,图2-7为各类存储器的结构图。

从图中可清楚看出各类存储器在存储器空间的位置。

AT89S51的并行I/O端口

4个双向的8位并行I/O端口,分别记为P0、P1、P2和P3,其中输出锁存器属于特殊功能寄存器。

端口的每一位均由输出锁存器、输出驱动器和输入缓冲器组成,4个端口按字节输入/输出外,也可位寻址。

P0口

P0口是一个双功能的8位并行端口,字节地址为80H,位地址为80H~87H。

端口的各位具有完全相同但又相互独立的电路结构,P0口某一位的位电路结构如图2-8所示。

1.位电路结构

P0口某一位的电路包括:

1)一个数据输出的锁存器,用于数据位的锁存。

2)两个三态的数据输入缓冲器,分别是用于读锁存器数据的输入缓冲器BUF1和读引脚数据的输入缓冲器BUF2。

3)一个多路转接开关MUX,它的一个输入来自锁存器的端,另一个输入为地址/数据信号的反相输出。

MUX由“控制”信号控制,实现锁存器的输出和地址/数据信号之间的转接。

4)数据输出的控制和驱动电路,由两个场效应管(FET)组成。

2.工作过程分析

1)P0口用作地址/数据总线

外扩存储器或I/O时,P0口作为单片机系统复用的地址/数据总线使用。

当作为地址或数据输出时,“控制”信号为1,硬件自动使转接开关MUX打向上面,接通反相器的输出,同时使与门处于开启状态。

当输出的地址/数据信息为1时,与门输出为1,上方的场效应管导通,下方的场效应管截止,P0.x引脚输出为1;当输出的地址/数据信息为0时,上方的场效应管截止,下方的场效应管导通,P0.x引脚输出为0。

输出电路是上、下两个场效应管形成的推拉式结构,大大提高了负载能力,上方的场效应管这时起到内部上拉电阻的作用。

当P0口作为数据输入时,仅从外部存储器(或I/O)读入信息,对应的“控制”信号为0,MUX接通锁存器的端。

由于P0口作为地址/数据复用方式访问外部存储器时,CPU自动向P0口写入FFH,使下方场效应管截止,上方场效应管由于控制信号为0也截止,从而保证数据信息的高阻抗输入,从外部存储器输入的数据信息直接由P0.x引脚通过输入缓冲器BUF2进入内部总线。

具有高阻抗输入的I/O口应具有高电平、低电平和高阻抗3种状态的端口。

因此,P0口作为地址/数据总线使用时是一个真正的双向端口,简称双向口。

2)P0口用作通用I/O口

当P0口不作为系统的地址/数据总线使用时,此时P0口也可作为通用的I/O口使用。

作通用的I/O口时,对应的“控制”信号为0,MUX打向下面,接通锁存器