3篇7章习题解答.docx

《3篇7章习题解答.docx》由会员分享,可在线阅读,更多相关《3篇7章习题解答.docx(16页珍藏版)》请在冰豆网上搜索。

3篇7章习题解答

第三篇第7章习题

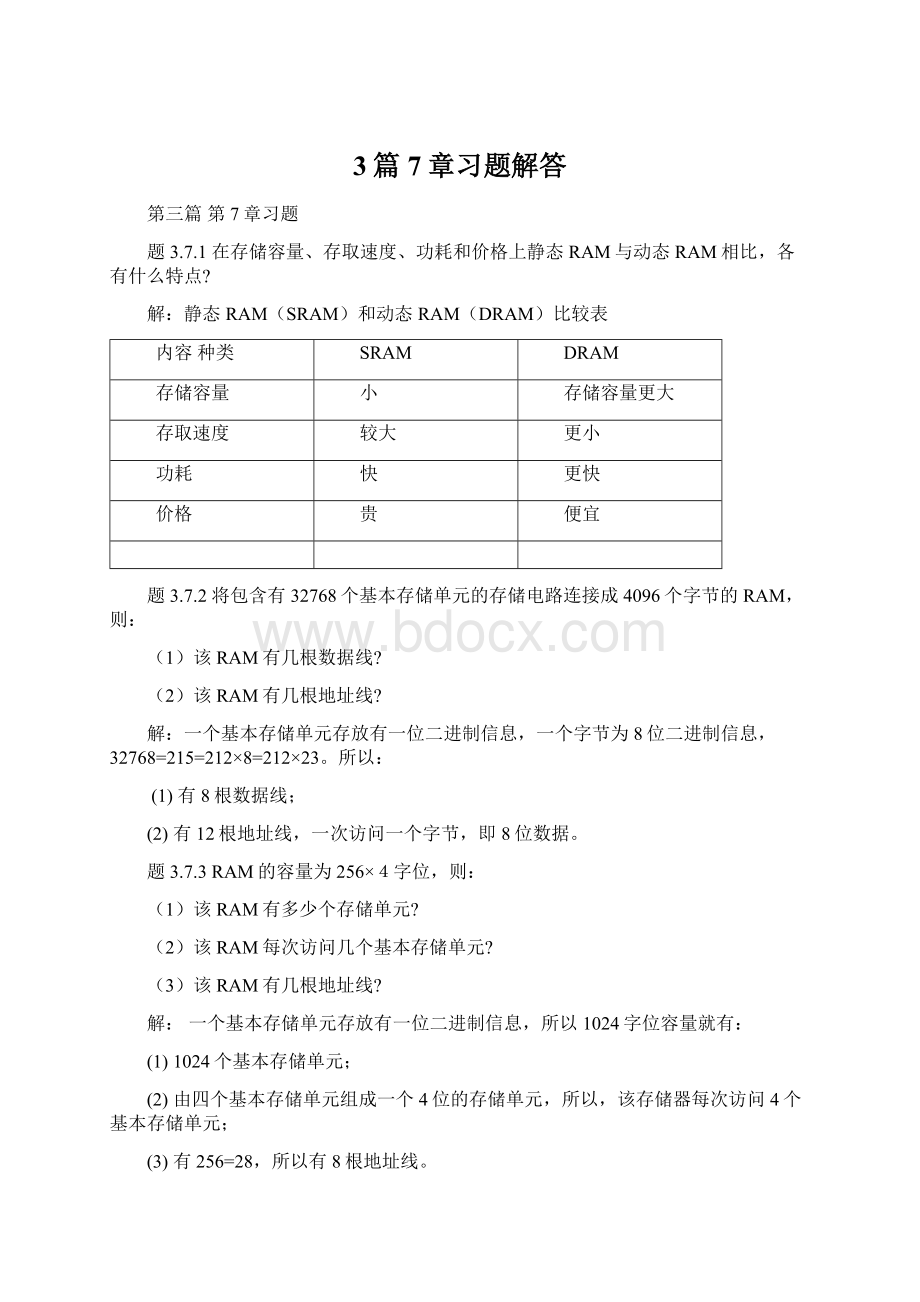

题3.7.1在存储容量、存取速度、功耗和价格上静态RAM与动态RAM相比,各有什么特点?

解:

静态RAM(SRAM)和动态RAM(DRAM)比较表

内容种类

SRAM

DRAM

存储容量

小

存储容量更大

存取速度

较大

更小

功耗

快

更快

价格

贵

便宜

题3.7.2将包含有32768个基本存储单元的存储电路连接成4096个字节的RAM,则:

(1)该RAM有几根数据线?

(2)该RAM有几根地址线?

解:

一个基本存储单元存放有一位二进制信息,一个字节为8位二进制信息,32768=215=212×8=212×23。

所以:

(1)有8根数据线;

(2)有12根地址线,一次访问一个字节,即8位数据。

题3.7.3RAM的容量为256×4字位,则:

(1)该RAM有多少个存储单元?

(2)该RAM每次访问几个基本存储单元?

(3)该RAM有几根地址线?

解:

一个基本存储单元存放有一位二进制信息,所以1024字位容量就有:

(1)1024个基本存储单元;

(2)由四个基本存储单元组成一个4位的存储单元,所以,该存储器每次访问4个基本存储单元;

(3)有256=28,所以有8根地址线。

题3.7.4试用256×4字位的RAM,用位扩展的方法组成一个256×8字位的RAM,请画出电路图。

解:

256×4字位的RAM只有4位数据线,要扩大成8位时应采用位扩展的方法实现。

将8位地址线、片选线、读/写控制线并联,RAM

(1)的4位作扩展后8位的高4位,RAM

(2)的4位作为扩展后的低4位,组成扩展后的8位数据输出。

其扩展的连接电路如图所示:

题3.7.5C850是64×1字位容量的静态RAM,若要用它扩展成一个128×4字位容量的RAM,需要几块C850?

并画出相应的电路图。

解:

该题原地址为64=26为6位,现要有128=27,需用7位地址线,因此要用地址扩展;数据线只有1位,现需要4位数据,同时要进行数据位扩展;所以要有8块C850是64*1字位容量的静态RAM。

其连接后的电路如图所示:

题3.7.6按照编程工艺不同,只读存储器大致可分为哪几类?

各有什么特点?

解:

熔丝/反熔丝型,EPROM型,E2PROM型,FlashMemory型等。

题3.7.7设某个只读存储器由16位地址构成,地址范围为000~FFF(16进制)。

现将它分为RAM、I/O、ROM1和ROM2等四段,且各段地址分配为RAM段:

000~DFFF;I/O段:

E000~E7FF;ROM1段:

F000~F7FF;ROM2段:

F800~FFFF。

试:

(1)设16位地址标号为A15A14……A1A0,则各存储段内部仅有哪几位地址值保持不变?

(2)根据高位地址信号设计一个选择存储段的地址译码器。

解:

(1)RAM存储段地址:

A15A14···A1A0为0000000000000000-

110111*********1,所有的地址都变;I/O存储段地址为

1110000000000000-111001*********1,只有A15A14A13A12A11=11100的地址不变;ROM1存储段具体地址为1111000000000000-111101*********1只有A15A14A13A12A11=11110五位地址不变;同理ROM2不变的地址为

A15A14A13A12A11=11111五位;

(2)因此,四个存储区的地址译码输出方程分别为:

画出相应的框图如下:

题3.7.8利用数据选择器和数据分配器的原理,将二只64×8容量的ROM分别变换成一只512×1字位和一只256×2字位ROM。

解:

变换成512×1字位时用8选1的数选择器,变换成256×2字位的系统时用

双4选1的数据选择器,它们的电路图分别如下:

题3.7.9有两块16KB(2048×8)的ROM,试用它们构成:

(1)32KB(4096×8)的ROM;

(2)32KB(2048×16)的ROM。

解:

(1)用二片16KB(2048*8)的ROM,加一个反相器即可实现32KB(4096*8)的ROM,连接图如图所示:

(2)该题只要进行数据位扩展即可,连接电路如图所示:

题3.7.10已知某8×4位PROM的地址输入为A3、A2、A1、A0,数据输出为D3、D2、D1、D0,且对应地址中存放数据如题表2.5.10所示,试求出各数据输出关于地址输入的逻辑函数表达式。

题表3.7.10

0000

0011

1000

1011

0001

0100

1001

1100

0010

0101

1010

1101

0011

0110

1011

1110

0100

0111

1100

1111

0101

1000

1101

0000

0110

1001

1110

0001

0111

1010

1111

0010

解:

D3=A3&A2&A1#A3&A2&A0#A3&A2#A3&A1&A0;

D2=A2&A1&A0#A2&A1#A2&A0;

D1=A1&A0#A1&A0;

D0=A0;

题3.7.11试用PROM设计一个二位二进制数的乘法器。

设被乘数为A1、A0,乘数为B1、B0,乘积为P3、P2、P1、P0。

试问:

(1)PROM的容量应该为多少字位?

(2)画出PROM实现该乘法器的编程逻辑图。

解:

(1)24×4;

P3=A1&A0&B1&B0;

(2)P2=A1&B1&B0#A1&A0&B1;

P1=A0&B1&B0#A1&B1&B0#A1&A0&B0#A1&A0&B1;

P0=A0&B0;

题3.7.12已知某逻辑电路如题3.7.12图所示,其中74LS161为一个四位二进制计数器,PROM中对应地址存放的数据如题表3.7.12所示,设计数器初态为“0000”,D=(D3D2D1D0)2,试:

`

(1)画出T=0~40秒内,输出数据D关于时间的变化波形。

(2)分析该电路实现了何种功能?

(3)若要用该电路实现一个近似的正弦波发生器,则PROM中的数据应如何存放

(4)若要改善波形的性能(如减少失真),电路应如何改造?

图题3.7.12

表题3.7.12

0000

0000

1000

1000

0001

0001

1001

0111

0010

0010

1010

0110

0011

0011

1011

0101

0100

0100

1100

0100

0101

0101

1101

0011

0110

0110

1110

0010

0111

0111

1111

0001

解:

(1)波形图

(2)

(2)三角波发生器。

(3)只需对正弦波采样即可

(4)增加计数器的位数,同时增加PROM的数据位数

题3.7.13CPLD器件与FPGA器件相比,各有哪些特点?

它们分别适合设计何种类型的逻辑电路?

解:

CPLD的基本逻辑块相对较大,布线延时可预测,资源利用率低。

适合设计复杂组合逻辑电路

FPGA的基本逻辑块较小,寄存器丰富,资源利用率高,布线延时不确定,特别适合大型时序逻辑电路的设计。

题3.7.14参考教材图3.7.25,试问单独用一个GLB最多可实现多少个逻辑变量的逻辑函数?

能否用它们实现这些变量组成的的所有逻辑函数?

解:

由于一个GLB最多只有18个输入逻辑变量,故它最多可直接实现18个逻辑变量的逻辑电路。

由于其与或阵列,及其它硬件资源的限止,它并不能实现所有18个输入的逻辑函数。

题2.5.15试问四变量输入的逻辑函数发生器,需要多少个存储单元控制?

最多可产生多少个逻辑函数?

又可当作容量为多少字位的高速SARM?

相应的地址输入、数据输出是什么?

解:

24个存储单元;216种逻辑运算;16(字)×1(位)的SRAM。

题3.7.16现要设计一个模四的可逆二进制计数器,当输入X=0时,实现加法计数,X=1时,实现减法计数。

试画出描述该计数器的ASM流程图。

解:

(1)电路共有16个状态,可依次定义为S1~S16

根据外部输入X,可方便地画出其ASM图。

例,若当前状态为S3,若X=1,则下一状态转移至S2,若X=0,则下一个状态转移至S4。

题3.7.17现要设计一个“110”序列脉冲检测器,设输入序列为X,输出为Z。

试画出描述该序列脉冲检测器的ASM流程图。

解:

定义如下状态

初始状态S0:

输入序列信号没有出现过“1”时的状态;

状态S1:

输入序列信号出现过一个“1”后的状态;

状态S2:

输入序列信号出现过连续两个“1”后的状态;

状态S3:

输入序列信号出现过连续两个“1”后,接着又出现“0”的状态,即出现了110序列信号。

ASM流程图如下:

题3.7.18(上机题)用VHDL语言描述一个能显示时、分、秒的数字钟电路,并要求时、分、秒可调。

解:

不带时、分、秒可调功能的数字钟参考VHDL源文件

顶层VHDL代码:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

ENTITYclockIS

PORT

(

g_clk,g_clr:

INSTD_LOGIC;

hh1_7bcd:

OUTSTD_LOGIC_VECTOR(6downto0);

hh0_7bcd:

OUTSTD_LOGIC_VECTOR(6downto0);

mm1_7bcd:

OUTSTD_LOGIC_VECTOR(6downto0);

mm0_7bcd:

OUTSTD_LOGIC_VECTOR(6downto0);

ss1_7bcd:

OUTSTD_LOGIC_VECTOR(6downto0);

ss0_7bcd:

OUTSTD_LOGIC_VECTOR(6downto0)

);

ENDclock;

ARCHITECTURErtlOFclockIS

COMPONENTcnt60

PORT(clk,clr,enable:

INSTD_LOGIC;

c60:

outSTD_LOGIC;

qh:

bufferSTD_LOGIC_VECTOR(2downto0);

ql:

bufferSTD_LOGIC_VECTOR(3downto0)

);

ENDCOMPONENT;

COMPONENTcnt24

PORT(clk,clr,enable:

INSTD_LOGIC;

qh:

bufferSTD_LOGIC_VECTOR(1downto0);

ql:

bufferSTD_LOGIC_VECTOR(3downto0)

);

ENDCOMPONENT;

COMPONENTBCDCODEn

PORT(d3,d2,d1,d0:

INSTD_LOGIC;

bcdcode:

OUTSTD_LOGIC_VECTOR(6downto0)

);

ENDCOMPONENT;

signalss_carry,mm_carry:

STD_LOGIC;

signalss1:

STD_LOGIC_VECTOR(2downto0);

signalss0:

STD_LOGIC_VECTOR(3downto0);

signalmm1:

STD_LOGIC_VECTOR(2downto0);

signalmm0:

STD_LOGIC_VECTOR(3downto0);

signalhh1:

STD_LOGIC_VECTOR(1downto0);

signalhh0:

STD_LOGIC_VECTOR(3downto0);

BEGIN

second:

cnt60PORTMAP(clk=>g_clk,clr=>g_clr,enable=>'1',c60=>ss_carry,qh=>ss1,ql=>ss0);

minus:

cnt60PORTMAP(clk=>ss_carry,clr=>g_clr,enable=>'1',c60=>mm_carry,qh=>mm1,ql=>mm0);

hour:

cnt24PORTMAP(clk=>mm_carry,clr=>g_clr,enable=>'1',qh=>hh1,ql=>hh0);

hh1bcd:

BCDCODEnPORTMAP(d3=>'0',d2=>'0',d1=>hh1

(1),d0=>hh1(0),bcdcode=>hh1_7bcd);

hh0bcd:

BCDCODEnPORTMAP(d3=>hh0(3),d2=>hh0

(2),d1=>hh0

(1),d0=>hh0(0),bcdcode=>hh0_7bcd);

mm1bcd:

BCDCODEnPORTMAP(d3=>'0',d2=>mm1

(2),d1=>mm1

(1),d0=>mm1(0),bcdcode=>mm1_7bcd);

mm0bcd:

BCDCODEnPORTMAP(d3=>mm0(3),d2=>mm0

(2),d1=>mm0

(1),d0=>mm0(0),bcdcode=>mm0_7bcd);

ss1bcd:

BCDCODEnPORTMAP(d3=>'0',d2=>ss1

(2),d1=>ss1

(1),d0=>ss1(0),bcdcode=>ss1_7bcd);

ss0bcd:

BCDCODEnPORTMAP(d3=>ss0(3),d2=>ss0

(2),d1=>ss0

(1),d0=>ss0(0),bcdcode=>ss0_7bcd);

ENDrtl;

60进制计数器VHDL源文件:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

ENTITYcnt60IS

PORT

(

clk,clr,enable:

INSTD_LOGIC;

c60:

outSTD_LOGIC;

qh:

bufferSTD_LOGIC_VECTOR(2downto0);

ql:

bufferSTD_LOGIC_VECTOR(3downto0)

);

ENDcnt60;

ARCHITECTURErtlOFcnt60IS

COMPONENTcnt10a

PORT(clk,clr,ena:

INSTD_LOGIC;

q:

outSTD_LOGIC_VECTOR(3downto0));

ENDCOMPONENT;

COMPONENTcnt6a

PORT(clk,clr,ena:

INSTD_LOGIC;

q:

outSTD_LOGIC_VECTOR(2downto0));

ENDCOMPONENT;

signalen:

STD_LOGIC;

BEGIN

cnt10:

cnt10aPORTMAP(clk,clr,enable,ql);

en<=ql(0)andql(3)andenable;

cnt6:

cnt6aPORTMAP(clk,clr,en,qh);

c60<=ql(0)andql(3)andqh(0)andqh

(2);

ENDrtl;

24进制计数器VHDL源文件:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

ENTITYcnt24IS

PORT

(

clk,clr,enable:

INSTD_LOGIC;

qh:

bufferSTD_LOGIC_VECTOR(1downto0);

ql:

bufferSTD_LOGIC_VECTOR(3downto0)

);

ENDcnt24;

ARCHITECTURErtlOFcnt24IS

COMPONENTcnt10a

PORT(clk,clr,ena:

INSTD_LOGIC;

q:

outSTD_LOGIC_VECTOR(3downto0));

ENDCOMPONENT;

COMPONENTcnt4a

PORT(clk,clr,ena:

INSTD_LOGIC;

q:

outSTD_LOGIC_VECTOR(1downto0));

ENDCOMPONENT;

signalen,clear:

STD_LOGIC;

BEGIN

clear<=clror(qh

(1)andql

(2));

en<=ql(0)andql(3)andenable;

cnt10:

cnt10aPORTMAP(clk,clear,enable,ql);

cnt4:

cnt4aPORTMAP(clk,clear,en,qh);

ENDrtl;

BCD编码VHDL源文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYBCDCODEnIS

PORT

(

d3,d2,d1,d0:

INSTD_LOGIC;

bcdcode:

OUTSTD_LOGIC_VECTOR(6downto0)

);

ENDBCDCODEn;

ARCHITECTUREbehaveOFBCDCODEnIS

signaltmp:

STD_LOGIC_VECTOR(3downto0);

BEGIN

tmp<=d3&d2&d1&d0;

PROCESS(d3,d2,d1,d0)

BEGIN

CASEtmpIS

WHEN"0000"=>bcdcode<="0000001";

WHEN"0001"=>bcdcode<="1001111";

WHEN"0010"=>bcdcode<="0010010";

WHEN"0011"=>bcdcode<="0000110";

WHEN"0100"=>bcdcode<="1001100";

WHEN"0101"=>bcdcode<="0100100";

WHEN"0110"=>bcdcode<="0100000";

WHEN"0111"=>bcdcode<="0001111";

WHEN"1000"=>bcdcode<="0000000";

WHEN"1001"=>bcdcode<="0000100";

WHENOTHERS=>bcdcode<="1111111";

ENDCASE;

ENDPROCESS;

ENDbehave;

10进制计数器VHDL源文件:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

ENTITYcnt10aIS

PORT

(

clk,clr,ena:

INSTD_LOGIC;

q:

outSTD_LOGIC_VECTOR(3downto0)

);

ENDcnt10a;

ARCHITECTUREbehaveOFcnt10aIS

signaltmp:

STD_LOGIC_VECTOR(3downto0);

BEGIN

PROCESS(clk,clr)

BEGIN

IFclr='1'THEN

tmp<="0000";

ELSIF(clk'EVENTANDclk='1')THEN

IFena='1'THEN

IF(tmp="1001")THENtmp<="0000";

ELSEtmp<=tmp+'1';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

q<=tmp;

ENDbehave;

6进制计数器VHDL源文件:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

ENTITYcnt6aIS

PORT

(

clk,clr,ena:

INSTD_LOGIC;

q:

outSTD_LOGIC_VECTOR(2downto0)

);

ENDcnt6a;

ARCHITECTUREbehaveOFcnt6aIS

signaltmp:

STD_LOGIC_VECTOR(2downto0);

BEGIN

PROCESS(clk,clr)

BEGIN

IFclr='1'THEN

tmp<="000";

ELSIF(clk'EVENTANDclk='1')THEN

ifena='1'then

if(tmp="101")thentmp<="000";

elsetmp<=tmp+'1';

endif;

endif;

ENDIF;

ENDPROCESS;

q<=tmp;

ENDbehave;

4进制计数器VHDL源文件:

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

E