电路板设计规范.docx

《电路板设计规范.docx》由会员分享,可在线阅读,更多相关《电路板设计规范.docx(100页珍藏版)》请在冰豆网上搜索。

电路板设计规范

印制电路板(PCB)设计规范

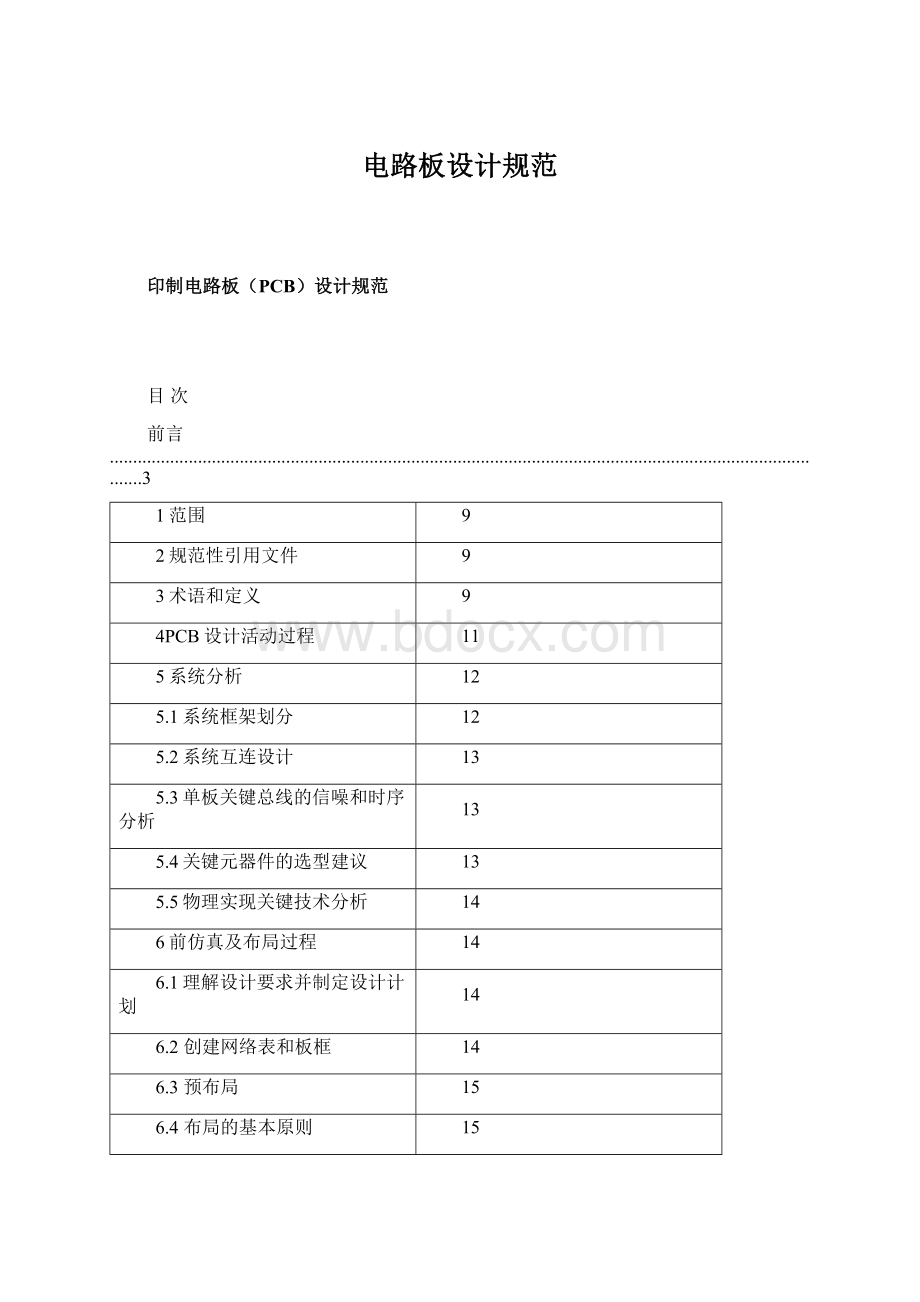

目次

前言..............................................................................................................................................................3

1范围

9

2规范性引用文件

9

3术语和定义

9

4PCB设计活动过程

11

5系统分析

12

5.1系统框架划分

12

5.2系统互连设计

13

5.3单板关键总线的信噪和时序分析

13

5.4关键元器件的选型建议

13

5.5物理实现关键技术分析

14

6前仿真及布局过程

14

6.1理解设计要求并制定设计计划

14

6.2创建网络表和板框

14

6.3预布局

15

6.4布局的基本原则

15

6.5信号质量

17

6.5.1规则分析

17

6.5.1.1时序计算

17

6.5.1.2关键网络拓扑分析

18

6.5.1.3串扰

18

6.5.1.4差分线

18

6.5.1.5时钟线

19

6.5.1.6其他规则

19

6.5.2层设计与阻抗控制

19

6.5.2.1层设计

19

6.5.2.2阻抗控制

21

6.5.3信号质量测试需求

22

6.6DFM

23

6.6.1PCB尺寸设计一般原则

23

6.6.2基准点ID的设计

24

6.6.3器件布局的通用要求

24

6.6.4SMD器件布局要求

24

6.6.4.1SMD器件布局的一般要求

24

6.6.4.2SMD器件的回流焊接器件布局要求

24

6.6.4.3SMD器件的波峰焊布局要求

25

6.6.5THD布局要求

26

6.6.6压接件器件布局要求

27

6.6.7通孔回流焊器件布局要求

27

6.6.7.1布局要求

27

6.6.7.2禁布区要求

28

6.6.8走线设计

28

6.6.8.1线宽/线距

28

6.6.8.2出线方式

28

6.6.8.3走线的安全性

30

6.6.8.4走线的热设计

30

6.6.9孔设计

31

6.6.9.1安装孔

31

6.6.9.2定位孔

32

6.6.9.3过孔

32

6.6.9.4埋、盲孔设计

32

6.6.10阻焊设计

32

6.6.10.1阻焊设计原则

32

6.6.10.2孔的阻焊设计

33

6.6.10.3BGA的过孔塞孔和阻焊设计

33

6.6.10.4走线的阻焊设计

33

6.6.10.5金手指的阻焊设计

33

6.6.11表面处理

33

6.6.12丝印设计

34

6.6.12.1丝印设计通用要求

34

6.6.12.2元器件丝印设计要求

34

6.6.12.3板名版本丝印

34

6.6.12.4条形码丝印

34

6.6.12.5其他丝印

35

6.6.13尺寸和公差标注

36

6.6.13.1尺寸标注的标准化要求

36

6.6.13.2需要标注的尺寸及其公差

36

6.6.14背板部分

36

6.6.14.1背板尺寸设计

36

6.6.14.2背板布局

37

6.6.14.3禁布区设计

37

6.6.14.4丝印设计

37

6.7DFT设计要求

38

6.7.1PCB的ICT设计要求

38

6.7.1.1ICT设计规定

38

6.7.1.2定位孔设计要求

39

6.7.1.3测试点设计要求

39

6.7.1.4ICT更改原则

41

6.7.2功能和信号测试点的添加

41

6.8EMC设计要求

41

6.8.1电源地系统的设计

42

6.8.1.1单板接口电源的设计

42

6.8.1.2板内分支电源的设计

42

6.8.1.3关键芯片的电源设计

43

6.8.2布局与EMC

43

6.8.2.1接口电路

43

6.8.2.1时钟电路

44

6.8.2.2其它

44

6.8.3布线与EMC

44

6.8.3.1接口电路

44

6.8.3.2时钟电路

45

6.8.3.3其它

45

6.9热设计要求

45

6.10安规设计要求

46

6.10.1线宽与所承受的电流关系

46

6.10.2-48V电源输入口规范

47

6.10.3有隔离变压器的接口(E1/T1口和类似端口)的安规要求

48

6.10.4网口安规要求(类似有隔离变压器的接口)

48

6.10.5串口(类似无隔离变压器的接口、如V35等)

48

6.10.6PGND电路要求

48

6.10.7ESD防静电标志

49

6.10.8保险丝标记

49

7布线及后仿真验证过程

50

7.1布线的基本要求

50

7.1.1布线次序考虑

50

7.1.2约束规则设置基本要求

51

7.1.3布线处理的基本要求

51

7.1.4布线所遵循的基本规则

52

7.2布线约束规则设置

56

7.2.1物理规则设置

56

7.2.1.1孔设置

56

7.2.1.2间距规则设置

57

7.2.1.3特殊布线区间的设定

58

7.2.2通用属性设置

59

7.2.3电气规则设置

59

7.3交互式规则驱动布线策略

59

7.3.1规则驱动布线可行性判断依据

59

7.3.2交互布线策略

60

7.3.3自动布线前期处理

60

7.3.3.1文件保护性操作

60

7.3.3.2Fanout设计要求与设置

60

7.3.3.3Fanout策略

60

7.3.4不同类型单板布线策略

61

7.3.4.1类型一PCB布线策略

61

7.3.4.2类型二PCB布线策略

62

7.3.4.3类型三PCB布线策略

63

7.3.4.4类型四PCB布线策略

65

7.3.5规则驱动布线后期处理

65

7.3.5.1测试点处理

65

7.3.5.2SpreadWires

65

7.3.5.3倒角

65

7.4仿真验证

66

8投板前需处理事项

66

8.1光绘层图纸标注和设计文件命名

66

8.1.1光绘层文件命名和图纸标注

66

8.1.2压缩文件名和包含的文件

67

8.2质量保证活动

67

8.2.1自检活动

67

8.2.2组内QA审查

68

8.2.3短路断路问题检查

68

8.2.4评审活动

69

8.3流程数据填写和文件提交

69

8.3.1投板流程中填写的项目:

69

8.3.2投板流程上粘贴5个压缩文件

70

8.4数据记录

70

8.4.1单板设计评审记录数据库的填写

70

8.4.2设计档案的填写

70

8.5PCB厂家工程问题确认和对外合作PCB设计的规定

70

9测试验证过程

71

9.1信号质量测试工程师具备的知识

71

9.2测试目的及测试内容

71

9.3测试方法

71

9.3.1示波器及探头的选择与使用

71

9.3.2信号波形参数定义

73

9.3.2.1信号波形参数的概念

73

9.3.2.2导致信号波形问题的一般原因

73

9.3.3测试点的选择原则

75

9.3.4信号质量测试应覆盖各功能块的信号

75

9.3.5各类信号的重点测试项目

75

9.3.5.1时钟信号测试项

75

9.3.5.2数据地址信号测试项

76

9.3.5.3电平控制信号测试项

76

9.3.5.4边沿控制信号测试项

76

9.3.5.5差分传输信号测试项

76

9.3.5.6同步总线的时序测试

76

9.3.5.7异步总线的时序测试

76

9.3.6各类信号测试方法和注意事项

77

10附录

79

10.1部门最新规范制度的查询与使用

79

10.2规则驱动布局布线的设计思想

79

10.3PCB设计投板作业流程

79

10.4SI工程设计任务及外包设计ECO更改作业流程

81

10.5PCB设计过程更改项填写规定

81

10.6自检工作监控办法

82

10.7归档PCB图框标题栏及填写说明

82

10.8测试验证过程附录

84

10.8.1同步总线时序测试实例参考

84

10.8.2示波器和探头带宽对测试信号边沿的影响

86

10.8.3测试探头的地回路对测试信号的影响

87

10.8.4高速差分眼图测试方法

89

11参考文献

92

印制电路板(PCB)设计规范

1范围

本规范规定了我司CAD/SI开发人员参与产品的设计过程和必须遵守的设计原则。

本规范适用于我司CAD/SI设计生产的所有印制电路板(简称PCB)。

2规范性引用文件

下列文件中的条款通过本规范的引用而成为本规范的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本规范,然而,鼓励根据本规范达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本规范。

序号

编号

名称

1

GB4588.3—88

印制电路板设计和使用

2

无

CAD/SI开发组活动过程

3

DKBA3128-2001.10

PCB工艺设计规范

3术语和定义

•印制电路板(PCB-printedcircuitboard):

在绝缘基材上,按预定设计形成印制器件或印制线路以及两者结合的导电图形的印制板。

•原理图(schematicdiagram):

电路原理图,用原理图设计工具绘制的、表达硬件电路中各种器件之间的连接关系的图。

•网络表(SchematicNetlist):

由原理图设计工具自动生成的、表达元器件电气连接关系的文本文件,一般包含元器件封装、网络列表和属性定义三部分。

•背板(backplaneboard):

用于互连更小的单板的电路板。

•TOP面:

封装和互连结构的一面,该面在布设总图上就作了规定(通常此面含有最复杂的或多数的元器件。

此面在通孔插装技术中有时称做“元器件面”)。

•BOTTOM面:

封装及互连结构的一面,它是TOP面的反面。

(在通孔插装技术中此面有时称做“焊接面”)。

•细间距器件:

pitch≤0.65mm的翼形引脚器件;

pitch≤1.0mm的面阵列器件。

•StandOff:

器件安装在PCB上后,本体底部与PCB表面的距离。

•护套:

和长针的背板连接器配合使用,安装在连接器的另一面,保护连接器的插针。

•右插板:

单板插入到背板上,从插板方向看,PCB在右边,器件面在左边。

•板厚(boardthickness):

包括导电层在内的包覆金属基材板的厚度。

板厚有时可能包括附加的镀层和涂敷层。

•金属化孔(platedthroughhole):

孔壁镀覆金属的孔。

用于内层和外层导电图形之间的连接。

同义词:

镀覆孔

•非金属化孔(NPTH—unsupportedhole):

没有用电镀层或其他导电材料加固的孔。

•过孔(Viahole)用作贯通连接的金属化通孔,内部不需插装器件引脚或其他加固材料。

•盲孔(blindvia):

来自TOP面或BOTTOM面,而不穿过整个印制电路板的过孔。

•埋孔(埋入孔,buriedvia):

完全被包在板内层的孔。

从任何表面都不能接近它。

•盘中孔(Viainpad):

在焊盘上的过孔或盲孔。

•阻焊膜(soldermaskorsolderresist):

是用于在焊接过程中及焊接之后提供介质和机械屏蔽的一种覆膜。

阻焊膜的材料可以采用液体的或干膜形式。

•焊盘(连接盘,Land):

用于电气连接、器件固定或两者兼备的部分导电图形。

•双列直插式封装(DIP—dual-in-linepackage):

一种元器件的封装形式。

两排引线从器件的侧面伸出,并与平行于元器件本体的平面成直角。

•单列直插式封装(SIP—single-inlinepackage):

一种元器件的封装形式。

一排直引线或引脚从器件的侧面伸出。

•小外型集成电路(SOIC—small-outlineintegratedcircuit)。

•THT:

通孔插件技术。

•SMT:

表面安装技术。

•压接式插针:

为压入金属化孔且不需要额外焊接而设计的具有专门形状截面的插针。

•波峰焊(wavesoldering):

印制板与连续循环的波峰状流动焊料接触的焊接过程。

•回流焊(reflowsoldering):

是一种将零、部件的焊接面涂覆焊料后组装在一起,加热至焊料熔融,再使焊接区冷却的焊接方式。

•压接:

由弹性的可变形的插针,或实体(刚性)的插针与PCB的金属化孔配合而形成的一种连接。

在插针与金属化孔之间形成紧密的接触点。

•桥接(solderbridging):

导线之间由焊料形成的多余导电通路。

•锡球(solderball):

焊料在层压板、阻焊层或导线表面形成的小球(一般发生在波峰焊或再流焊之后)。

•锡尖(拉尖,solderprojection):

出现在凝固的焊点上或涂覆层上的多余焊料凸起物。

•墓碑(器件直立,Tombstonedcomponent):

一种缺陷,无引线器件只有一个金属化焊端焊在焊盘上,另一个金属化焊端翘起,没有焊在焊盘上。

•当前层(Activelayer):

当前正在编辑的层。

当前层与辅助层配对。

•反标注(反向标注,Backannotation):

根据PCB设计文件中所作的改动更新原理图文件,通常采用程序进行执行完成此项工作。

在更换管脚、更换门、参考标号重新编号以后必须进行反标注。

•材料清单(BOM-Billofmaterials):

装备部件的格式化清单。

•光绘(photoplotting):

由绘图仪产生电路板工艺图的过程,绘图仪使胶片曝光从而将被绘制部分制成照片。

•设计规则检查(DRC-Designruleschecking):

通过通知您设计违规,确保建立的设计符合规定的设计规则的程序。

•电磁兼容EMC(Electromagneticcompatibility):

设备或系统在其电磁环境中能正常工作且不对该环境中任何事物构成不能承受的电磁骚扰的能力(ANSIC64.14-1992)。

4PCB设计活动过程

CAD/SI开发人员的活动贯穿于整个产品开发过程中,为产品开发提供全流程的信号完整性分析、布局布线设计、测试验证等系统和单板物理设计与实现方面的技术服务。

CAD/SI开发人员参与产品的活动过程分为四个阶段:

•CAD/SI系统分析过程;

•前仿真及布局过程;

•布线及仿真验证过程;

•测试验证过程。

如图1所示:

PCB设计活动过程图

1)系统分析:

CAD/SI系统分析工程师根据硬件总体框架,对系统高速互连进行信号完整性分析,确定系统框架分割的合理性。

其内容涉及系统互连设计,单板关键总线的信噪和时序分析,关键元器件的应用分析及选型建议,物理实现关键技术分析等内容。

2)布局:

在综合考虑信号质量、EMC、热设计、DFM/DFT、结构、安规等方面要求的基础上,将器件合理的放置到板面上。

3)仿真:

在器件IBIS、SPICE等模型的支持下,利用EDA工具对PCB的预布局、布线进行信号质量和时序分析,得出一定的物理电气规则参数,并运用于布局布线中,从而在单板的物理实现之前解决PCB设计中存在的时序问题和信号完整性问题。

仿真通常分为前仿真分析和后仿真验证两部分。

4)布线:

在遵循信号质量、DFM、EMC等规则要求下,实现器件管脚间的物理连接设计。

5)测试验证:

CAD/SI工程师从PCB物理实现的角度参与硬件测试中的信号完整性测试部分,进行信号质量和时序测试,并对出现的信号质量问题进行处理。

测试验证主要涉及信号质量测试、信号时序测试和容限测试等三个方面工作。

5系统分析

.1系统框架划分

在硬件系统方案中,根据系统的功能模块对系统框架进行了划分。

这里,我们从CAD/SI的实现角度,对其框架划分方案进行验证。

若验证后发现有不合理的地方,应给出解决方法,提出合理的框架划分方案。

对于大部分已经有继承性的产品来说,其系统各功能模块的划分已经过相关产品的验证,这时可省略这部分的分析内容。

这里单独提出这一部分的分析要求,主要针对部分新产品,尤其是预研产品,由于新技术或新方案中选用的套片或部分芯片使用了较新的接口、电平类型或封装,须结合有关技术资料,从CAD设计实现和SI仿真方面进行分析。

分析时首先要对当前硬件总体划分的模块中涉及的总线及电平特点,该总线的驱动负载能力,多负载情况下的信号完整性问题等进行分析阐述,论证系统框架划分是否合理,若不合理,给出推荐的划分方案和分析数据。

其次,若系统中有器件密度及可能布线密度较大的单板,需要分析其信号完整性问题和PCB实现难度等,通过分析论证这种划分的合理性。

.2系统互连设计

系统互连有框间互连、板间互连、模块间互连三种形式,可根据具体情况进行分析。

分析要点如下:

1)分析系统互连的电平的特点,使用中的匹配方式,若同一种接口电平不同厂家不同器件的性能差别明显,应给出优选方案;

2)若互连采用的是同步或准同步总线需要进行静态时序分析;

3)对多负载网络需要根据不同的拓扑结构给出仿真波形;

4)点到点结构的网络可酌情给出不同匹配情况的仿真波形;

5)对信号排布较密或对串扰敏感的电平需要给出信号在连接器上不同排布情况下的串扰仿真分析;

6)根据仿真波形给出噪声裕量分析。

.3单板关键总线的信噪和时序分析

对系统的关键单板需要进行重点分析,分析要点有两个:

总线信噪分析和时序分析。

1)信噪分析主要是串扰分析。

首先确定信号电平的直流噪声容限,分析当器件工作在最坏情况下时,对关键总线在不同线宽/线间距时的串扰进行分析,综合设计难度、加工难度等因素,在满足直流噪声容限的情况下,确定PCB实现的线宽/线间距约束条件。

2)时序分析。

这里指静态时序分析。

根据单板中时钟的同步方式,用计算静态时序的方法,计算出关键总线的PCB传输延迟,从而得出各接口间的PCB走线长度。

.4关键元器件的选型建议

从信号质量、封装、时序等方面进行分析:

1)从信号完整性分析的角度,分析相同功能的不同器件,在相同的工作条件下,根据仿真波形,根据信号质量的不同,给出优选器件。

对于只有一种器件的情况,也可仿真出不同条件下(高、低温,单负载或多负载等)的信号波形,分析其接口性能,给出该器件是否满足系统要求的选型建议。

2)若同一器件有多种封装,应该结合当前我们的供应商的技术水平和我们生产的工艺水平,选择易于设计和实现的PCB封装形式,给出选型建议。

.5物理实现关键技术分析

物理实现即PCB设计实现方案。

根据系统中不同的信号特性,可选择从如下几个方面进行分析。

1)当系统中有高速总线时,如果需要在PCB板上传输较长的距离,且收发器对传输中的信号抖动、损耗有严格要求;或者信号要求有较高的传输线特征阻抗,预计用普通FR4材料设计单板将严重超出结构要求的厚度。

这时可考虑使用低损耗、低介电常数的材料。

2)若预测单板布线密度很大,采用常规的通孔设计方法无法在有限的PCB信号层内完成布线时,可考虑使用埋盲孔设计方法或采用HDI设计及加工方法等。

但是,是否采用这种方法需要与中试单板工艺、采购等专家进行研究协商,综合成本和生产加工等因素再决定。

因为,由于目前国内PCB加工厂家的加工工艺有限,同时我们的测试手段也受限制,所以采用埋盲孔和HDI设计的单板,加工直通率相对较低,若预计今后单板批量生产量较大时,应尽量避免使用这些非常规设计方法。

6前仿真及布局过程

.6理解设计要求并制定设计计划

1)仔细审读原理图和功能框图,在与原理图设计者充分交流的基础上,确认PCB设计的电气性能要求。

2)在与原理图设计者交流的基础上制定出单板的PCB设计计划,填写设计记录表,计划要包含设计过程中原理图调入、预布局、仿真分析、布局完成、布局评审、布线完成、布线评审、光绘完成等关键检查点的时间要求。

设计计划应由PCB设计者和原理图设计者双方签字认可。

如果出现由于种种原因导致设计计划推迟的情况,要制定相应的调整计划,而且需注明原因并由相关人员签字确认。

.7创建网络表和板框

1)对于改板、归档或套用板框的PCB文件必须从文档室申请。

2)对原理图的规范性进行检查,积极协助原理图设计者排除错误,保证网络表的正确性和完整性。

3)协助原理图设计者根据器件编码与封装对应相关数据库确定器件的封装。

4)对于新器件或新模型,将器件的封装资料或模型资料提供给相关的建库人员或模型验证人员。

5)根据原理图和PCB设计工具的特性,选用正确的网络表格式,创建符合要求的网络表。

6)根据结构要素图或对应的标准板框,创建PCB设计文件。

坐标原点必须为选择单板左边、下边的延长线交汇点。

7)板框四周倒圆角,倒角半径5mm/197mil。

特殊情况参考结构设计要求。

.8预布局

1)参考原理图和功能框图根据信号流向放置重要的单元电路和核心器件。

2)对关键信号进行前仿真分析。

仿真分析方法详见本规范6.5章节的信号质量。

3)根据仿真分析结果来确定重要单元电路和核心器件的大概布局位置,使关键信号能够满足时序和信号质量等要求。

.9布局的基本原则

1)与相关人员沟通以满足结构、SI、DFM、DFT、EMC方面的特殊要求。

2)根据结构要素图,放置接插件、安装孔、指示灯等需要定位的器件,并给这些器件赋予不可移动属性,并进行尺寸标注。

3)根据结构要素图和某些器件的特殊要求,设置禁止布线区、禁止布局区域。

4)综合考虑PCB性能和加工的效率选择工艺加工流程(优先为单面SMT;单面SMT+插件;双面SMT;双面SMT+插件),并根据不同的加工工艺特点布局。

5)布局时参考预布局的结果,根据“先大后小,先难后易”的布局原则。

6)布局应尽量满足以下要求:

总的连线尽可能短,关键信号线最短;高电压、大电流信

号与低电压、小电流信号的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间距要充分。

在满足仿真和时序分析要求的前提下,局部调整。

7)相同电路部分尽可能采用对称式模块化布局,具体操作参见《PCB分组模块化布局介绍》。

8)布局设置建议栅格为50mil,IC器件布局,栅格建议为25252525mil。

布局密度较高时,小型表面贴装器件,栅格设置建议不少于5mil。

9)布局时,考虑fanout和测试点的位置,以器件中心点参考移动,考虑在两个过孔中间走两根走线,如下图2、图3所示:

FANOUT图例

(1)

FANOUT图例

(2)

测试点ICT的要求详见本规范第6.5章节的DFT设计要求。

10)根据信号质量、EMC的要求,合理的确定布线层设置,完成电源地分割。

信号质量的布局规则详见本规范第6.5章节的信号质量,EMC要求详见本规范第6.8章节的EMC设计要求。

11)布完局后所有器件必须放置在PC