计算机组成原理课程设计.docx

《计算机组成原理课程设计.docx》由会员分享,可在线阅读,更多相关《计算机组成原理课程设计.docx(29页珍藏版)》请在冰豆网上搜索。

计算机组成原理课程设计

计算机组成原理课程设计报告

专业名称:

计算机学院

班级学号:

网络10013100610019

学生姓名:

李嘉利

指导教师:

丁伟

设计时间:

2012年6月11日——2012年6月19日

第一天取操作数微程序的设计和调试

一、设计目标

设计并调试取操作数的微程序。

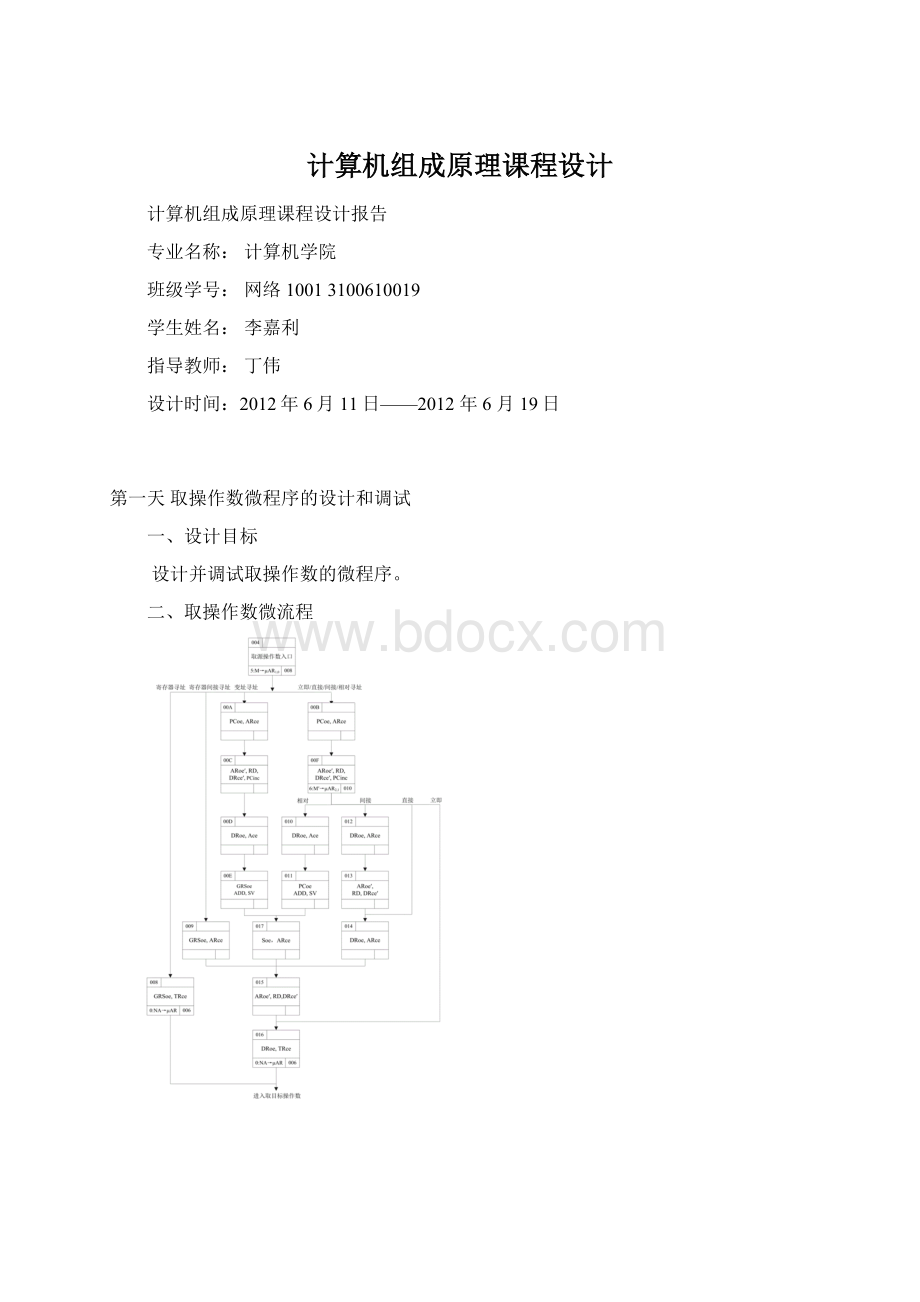

二、取操作数微流程

三、测试程序、数据及运行结果

格式如下:

1、测试内容:

直接寻址

测试指令(或程序):

MOV#5678H,0010H

运行结果及分析:

此指令将5678存入到0010单元

机器码:

内存地址(H)

机器码(H)

汇编指令

0000

077A56780010

MOV#5678H,0010H

运行结果及分析:

此指令将5678存入到0010单元

四、设计中遇到的问题及解决办法

在设计过程中开始对调试程序的运行不是特别熟悉,通过反复验证和询问熟悉的了解了此程序的运行,另外,在操作过程中,产生了输入二进制代码的顺序错误,经过重新输入解决了此问题。

通过此次试验,详细的了解了取操作数微程序的设计和调试,了解了它的整个过程和对于每一步的分析和验证,对流程有了更深入的认识。

第二天运算指令的微程序设计与调试

一、设计目标

设计并调试运算指令的微程序。

二、运算指令微程序入口地址

指令助记符

指令编码

入口地址(H)

F

E

D

C

B

A

9

8

7

6

5

4

3

2

1

0

MOVsrc,dst

0

0

0

0

0

1

源地址码

目的地址码

044

ADDsrc,dst

0

0

0

0

1

0

源地址码

目的地址码

048

ADDCsrc,dst

0

0

0

0

1

1

源地址码

目的地址码

04C

SUBsrc,dst

0

0

0

1

0

0

源地址码

目的地址码

050

SUBBsrc,dst

0

0

0

1

0

1

源地址码

目的地址码

054

CMPsrc,dst

0

0

0

1

1

0

源地址码

目的地址码

058

ANDsrc,dst

0

0

0

1

1

1

源地址码

目的地址码

05C

ORsrc,dst

0

0

1

0

0

0

源地址码

目的地址码

060

XORsrc,dst

0

0

1

0

0

1

源地址码

目的地址码

064

TESTsrc,dst

0

0

1

0

1

0

源地址码

目的地址码

068

INCdst

0

0

0

0

0

0

1

0

0

0

1

目的地址码

0A4

DECdst

0

0

0

0

0

0

1

0

0

1

0

目的地址码

0A8

NOTdst

0

0

0

0

0

0

1

0

0

1

1

目的地址码

0AC

三、运算类指令微程序

微地址(H)

微指令(H)

微命令

BM

NA

注释

007

00000800

OP

4

XXX

指令执行入口

048

9870006F

TRoe,ADD,Sce,PSWce

0

06F

ADD

04C

98B0006F

TRoe,ADDC,SV,PSWce

0

06F

ADDC

050

98F0006F

TRoe,SUB,SV,PSWce

0

06F

SUB

06F

00000E70

7

070

存结果

070

68000000

Soe,GRSce

0

000

ALU运算,结果送寄存器

071

60030072

Soe,DRce

0

072

结果送存储器

072

00052000

DRoe’,ARoe’,WR

0

000

四、测试程序、数据及运行结果

1、测试内容:

ADD#1234H,0010H

运行数据:

0B7A12340010

运行结果及分析:

将值1234与0010单元内容相加所得的结果,并且将此结果存入到主存中。

2、测试内容:

OR#F000H,2(R0)

运行数据:

2370F0000002

运行结果及分析:

将值F000与R0寄存器中的值0010进行或运算得到结果0000存入到R0中。

3、测试内容:

INCR1

运行数据:

0221

运行结果及分析:

将R1中的内容进行加1操作,结果存入R1中。

测试内容:

TEST#1,(R0)

运行数据:

07600100

运行结果:

五、设计中遇到的问题及解决办法

指令的机器码写正确,否则会带来一些不必要的麻烦和错误,要将指令在写微程序时有一些不懂,后来经过老师的讲解明白了大概,又有同学帮忙改错,终于完成微程序的输入,输入时由于不太仔细有一些错误,经过调试发现并改正完善了微程序。

第三天CPU硬件的初级设计与验证

一、设计目标

在运算器实验的基础上对硬件进行扩充,建立初级CPU的数据通路,构造一个只支持运算指令的初级CPU。

二、硬件设计

1、PC模块设计

`timescale1ns/1ps

modulePC(d,q,n_reset,clk,ce,PCinc);

input[15:

0]d;

inputn_reset,clk,ce;

inputPCinc;

output[15:

0]q;

reg[15:

0]data;

always@(posedgeclkornegedgen_reset)//程序计数器PC采用异步复位

begin

if(!

n_reset)//当n_reset有效时,PC清0

data=0;

elseif(ce)//在时钟信号clk的上升沿如果数据装入,且使能ce有效则d→q(通过中间变量data)

data=d;

elseif(PCinc)//如果自加信号PCinc有效则q+1→q(通过中间变量data)

data=data+1;

end

assignq=data;

endmodule

2、DR模块设计//DR连接内部总线IB和系统总线的DB

//DR有两路数据输入data_IB、data_DB,分别来自IB、DB,相应的有两//个装入使能信号DRce_IB、DRce_DB

`timescale1ns/1ps

moduleDR#(

parameterDATAWIDTH=16)

(inputwire[DATAWIDTH-1:

0]data_IB,

inputwire[DATAWIDTH-1:

0]data_DB,

inputwireclk,

inputwireDRce_IB,

inputwireDRce_DB,

inputn_reset,

outputreg[DATAWIDTH-1:

0]q);

always@(posedgeclkornegedgen_reset)//DR采用异步复位

begin

if(!

n_reset)//当n_reset有效时,DR清0

q=0;

elseif(DRce_IB)//在时钟信号的上升沿,当DRce_IB有效时则data_IB→q

q=data_IB;

elseif(DRce_DB)//当DRce_DB有效时则data_DB→q

q=data_DB;

end

endmodule

3、IR模块设计

//TR

//TR寄存器的实例化

R#(DATAWIDTH)TR(.q(TR_out),.d(IB),.clk(clock),.ce(TRce),.n_reset(n_reset));

buffer#(DATAWIDTH)reg_buffer(.q(IB),.d(TR_out),.oe(TRoe));

//AR

//AR寄存器的实例化

R#(DATAWIDTH)AR(.q(AR_out),.d(IB),.clk(clock),.ce(ARce),.n_reset(n_reset));

buffer#(ADDRWIDTH)AR_AB(.q(AB),.d(AR_out),.oe(ARoe_AB));

buffer#(ADDRWIDTH)AR_IB(.q(IB),.d(AR_out),.oe(ARoe_IB));

//IR

//IR寄存器的实例化

R#(DATAWIDTH)IR(.q(IR_out),.d(IB),.clk(clock),.ce(IRce),.n_reset(n_reset));

3、顶层模块设计(自己增加的设计部分)

TR寄存器的实例化:

R#(DATAWIDTH)TR(.q(TR_out),.d(IB),.clk(clock),.ce(TRce),.n_reset(n_reset));

//TR的输出连接到三态门上,输出即为CPU.v中已经定义好的TR_out

//TR的输入是从IB总线上输入的,因此连接IB

//TR的时钟信号,以及复位信号,都是顶层模块中的统一时钟信号和复位信号

//TR的使能信号即为CPU.v中定义的TRce。

AR寄存器的实例化

R#(ADDRWIDTH)AR(.q(AR_out),.d(IB),.clk(clock),.ce(ARce),.n_reset(n_reset));

//AR的输出连接到三态门上,输出即为CPU.v中已经定义好的AR_out

//AR的输入是从IB总线上输入的,因此连接IB

//AR的时钟信号,以及复位信号,都是顶层模块中的统一时钟信号和复位信号

//AR的使能信号即为CPU.v中定义的ARce。

IR寄存器的实例化

R#(DATAWIDTH)IR(.q(IR_out),.d(IB),.clk(clock),.ce(IRce),.n_reset(n_reset));

//IR的输出连接到三态门上,输出即为CPU.v中已经定义好的IR_out

//IR的输入是从IB总线上输入的,因此连接IB

//IR的时钟信号,以及复位信号,都是顶层模块中的统一时钟信号和复位信号

//IR的使能信号即为CPU.v中定义的IRce。

三、验证

1.MOV#56780010

077A56780010

2.测试内容:

OR#F000H,2(R0)

运行数据:

2370F0000002

运行结果及分析:

3.测试内容:

INCR1

运行数据:

0221

运行结果及分析:

4.测试内容:

TEST#1,(R0)

运行数据:

07600100

运行结果及分析:

四、设计中遇到的问题及解决办法

在验证PC.v程序代码的正确性时,出现错误,仔细观察代码发现,代码上面已经定义了一个中间变量data,而q只是一个信号,不能够参加运算,应用data写相关程序,再将数据送给q,程序实现才会正确。

第四天为CPU扩充转移指令

一、设计要求

在初级CPU的基础上进行功能扩充,使其支持转移类指令。

二、硬件uAG模块设计

(自己修改的设计部分,加上适当注释)

3'd3:

uAGout={NA[8:

1],BM3_uAR0};//条件转移指令产生两条分支(即条件满足

//条件不满足两种情况)

2'b00:

Flag_MUX<=SZOC[0];//IR7,IR6为00时,选择PSW的最低位,即CF

2'b01:

Flag_MUX<=SZOC[1];//IR7,IR6为01时,选择PSW的倒数第二位,即OF

2'b10:

Flag_MUX<=SZOC[2];//IR7,IR6为10时,选择PSW的第二位,即ZF

2'b11:

Flag_MUX<=SZOC[3];//IR7,IR6为11时,选择PSW的最高位,即SF

三、转移指令微程序的设计

四、测试程序、数据及运行结果

1、测试内容:

01MOV#10H,R1

02MOV#1234H,R0

03ADD#5678H,R0

04JZ(R1)

运行数据:

07610010

07601234

0B605678

0189

运行结果及分析:

将0010送人到R1中,将1234送入到R0中,将5678与R0中的1234进行加法运算得到结果为68AC存入到R0中,而相加结果不产生进位,CF=0,条件不满足,不执行JC,PC的值顺序执行

2、测试内容:

01MOV#10H,R1

02MOV#0001H,R2

03ADD#FFFFH,R2

04JZ(R1)

运行数据:

07610010

07620001

0B62FFFF

0189

运行结果及分析:

把0010存入R1中,把0001存入R2中,将FFFF与R2中的0001相

加,相加之后产生进位,CF=1,且结果为零,ZF=1,满足条件uAR0=1,可执行JC,

PC的值由007直接跳转至010。

五、设计中遇到的问题及解决办法

起先对转移指令不了解,经过老师讲解明白了转移指令的条件。

第五天为CPU扩充移位指令

一、设计目标

在前面CPU的基础上扩充硬件,使其支持移位指令。

二、硬件设计

1、SHIFTER模块设计

(加上适当注释)

moduleSHIFTER(q,d,clk,sv,sl,sr,n_reset,IR76,CF);

parameterDATAWIDTH=16;

output[DATAWIDTH-1:

0]q;

input[DATAWIDTH-1:

0]d;

input[1:

0]IR76;

inputclk,n_reset,CF;

inputsv,sl,sr;

reg[DATAWIDTH-1:

0]data;

wiredata_lsb;

wiredata_hsb;

mux#

(1)mux_1(.d1(0),.d2(0),.d3(d[15]),.d4(CF),.addr(IR76),.q(data_lsb));

//实例化最低有效位生成的四选一多路选择器

//addr选择哪种移位操作,为01时,选择逻辑左移(与

//算术左移相同),最低位补0;为10时,选择循环左移

//最低位用最高位补;为11时,选择带进位循环左移,

//最低位用CF补

mux#

(1)mux_2(.d1(d[15]),.d2(0),.d3(d[0]),.d4(CF),.addr(IR76),.q(data_hsb));

//实例化最高有效位生成的四选一多路选择器

//addr选择哪种移位操作,为00时,选择算是右移,最高

//位复制;为01时,选择逻辑右移,最高位补0;为10时,

//选择循环左移最高位用最低位补;为11时,选择带进位

//循环左移,最高位用CF补

always@(posedgeclkornegedgen_reset)

begin

if(!

n_reset)

data=0;

elseif(sv)

data=d;

elseif(sl)

data={d[DATAWIDTH-2:

0],data_lsb};

elseif(sr)

data={data_hsb,d[DATAWIDTH-1:

1]};

end

assignq=data;

endmodule

2、CF模块设计

`timescale1ns/1ps

moduleCF(d15,d0,Cout,q,SL,SR);

inputd15,d0,Cout;

inputSL,SR;

outputq;

regq;

always@(*)

begin

case({SL,SR})

3'b01:

q=d0;//右移时,最低位送CF

3'b10:

q=d15;//左移时,最高位送CF

default:

q=Cout;//其他情况CF不变

endcase

end

endmodule

3、IR_DECODE模块设计

2'b00:

BM4_uA<={5'b01001,IR[7:

5],1'b0};//移位类指令微程序的入口地形成规则

4、顶层模块设计

wireCF_out;

CF#(DATAWIDTH)

CF(.d15(ALU_out[15]),.d0(ALU_out[0]),.Cout(Cout),.q(CF_out),.SL(SL),.SR(SR));

//CF实例化,ALU_out[15],输入,来自移位数据的最高位;ALU_out[0],输入,来自移位数据的最低位;Cout,输入,来自ALU的进位输出;SL,输入,SHIFTER移位器的左移信号;SR,输入,SHIFTER移位器的右移信号;q,输出,来自进位的输出。

三、移位指令微程序的设计

微地址(H)

微指令(H)

微指令字段(H)

微命令

F0

F1

F2

F3

F4

F5

F6

F7

F8

F9

092

1810006F

0

6

0

1

0

0

0

0

0

06F

SR,PSWce

094

1820006F

0

6

0

2

0

0

0

0

0

06F

SL,PSWce

096

1810006F

0

6

0

1

0

0

0

0

0

06F

SR,PSWce

098

1820006F

0

6

0

2

0

0

0

0

0

06F

SL,PSWce

09A

1810006F

0

6

0

1

0

0

0

0

0

06F

SR,PSWce

09C

1820006F

0

6

0

1

0

0

0

0

0

06F

SL,PSWce

09E

1810006F

0

6

0

1

0

0

0

0

0

06F

SR,PSWce

四、测试程序、数据及运行结果

1、测试内容:

MOV#0101R1

SARR1

运算数据:

076101010021

指令功能:

将0101送入R1中再将R1算术右移

2.测试内容:

SHL0100H3

.

运算数据:

005A,0100

指令功能:

将0100单元中的内容逻辑左移

3、测试内容:

ROR(0011H)

运算数据:

00B90011

指令功能:

将0011单元中的地址中的内容循环右移

4、测试内容:

RCL+0101H

运算数据:

00D80101

指令功能:

将0101+PC单元中的内容带进位循环左移

5、测试内容:

SHR0011H

运算数据:

007A0011

指令功能:

将0010单元中的内容逻辑右移

6、测试内容:

ROL(0011H)

运算数据:

00990011

指令功能:

将0010单元中的地址中的内容循环左移

7、测试内容:

RCR+0011H

运算数据:

00F80011

指令功能:

将0011+PC单元中的内容带进位循环右移

四、设计中遇到的问题及解决办法

第六天为CPU扩充堆栈类指令

一、设计目标

在前面CPU的基础上增加堆栈,使其支持与堆栈有关的PUSH,POP,CALL,RET指令。

二、硬件设计

1、SP模块设计

(加上适当注释)

`timescale1ns/1ps

moduleSP(q,d,clk,ce,n_reset);

parameterDATAWIDTH=16;

output[DATAWIDTH-1:

0]q;

input[DATAWIDTH-1:

0]d;

inputclk,ce,n_reset;

reg[DATAWIDTH-1:

0]q;

always@(posedgeclkornegedgen_reset)

begin

if(!

n_reset)

q=16'h003F;//当复位信号有效时,SP的输出为03F

elseif(ce)//当使能信号有效时,输出就是输入的内容

q=d;

end

endmodule

2、顶层模块设计

SP#(DATAWIDTH)SP(.d(IB),.q(SP_out),.clk(clock),.ce(SPce),.n_reset(n_reset));

//堆栈SP的输入来自总线IB;输出为SP_out;时钟信号以及复位信号就是总的定义的信号;

//使能为SPce.

buffer#(DATAWIDTH)SP_IB(.q(IB),.d(SP_out),.oe(SPoe));

//三态门的输入来自SP的输出;输出连接到总线IB;使能为SPoe.

三、PUSH、POP、CALL、RET指令微程序的设计

PUSH(堆栈指令)

微地址(H)

微指令(H)

微命令

BM

NA

注释

0C0

F43000C1

SV,SPoe,Ace

0

0C1

0C1

62B300C2

Soe,DRce,DEC,SV

0

0C2

0C2

7C0800C3

Soe,SPce,ARce

0

0C3

0C3

00052000

DRoe’,ARoe’,WR

0

000

POP(压栈指令)

微地址(H)

微指令(H)

微命令

BM

NA

注释

0C8

B00000C9

ARoe,TRce

0

0C9

0C9

F40800CA

SPoe,ARce,Ace

0

0CA

0CA

027610CB

RD,ARoe’,DRce’,INC,SV

0

0CB

0CB

800800CC

TRoe,ARce

0

0CC

0CC

7C052000

ARoe’,DRoe’,WR,Soe,SPce

0

000

CALL(子程序调用指令)

微地址(H)

微指令(H)

微命令

BM

NA

注释

0D0

F40000D1

SPoe,Ace

0

0D1

栈顶单元减一,并保存原PC内容

0D1

B2B000D2

DEC,SV,ARoe,TRce

0

0D2

0D2

7C0800D3

Soe,ARce,SPce

0

0D3

将新地址送入SP和AR中

0D3

200300D4

PCoe,DRce

0

0D4

将PC内容放入DR

0D4

84052000

ARoe’,DRoe’,WR,TRoe,PCce

0

000

写入栈顶单元