pld实验报告.docx

《pld实验报告.docx》由会员分享,可在线阅读,更多相关《pld实验报告.docx(19页珍藏版)》请在冰豆网上搜索。

pld实验报告

数字系统设计与PLD应用实验报告

041010204欧阳琼

一、实验目的

1、了解并学习HDPLD设计数字系统的设计思路和设计过程。

2、通过自行设计数字系统实例,更好的掌握数字系统设计方法以及设计软件的使用,让书本知识在教学实践中得到成功应用.

二、实验内容

1、高速并行乘法器的设计

(1)、实验原理

采用以下算法:

被乘数的数值位左移,它和乘数的各个数值位进行累加运算.且用与门、4位加法器来实现.

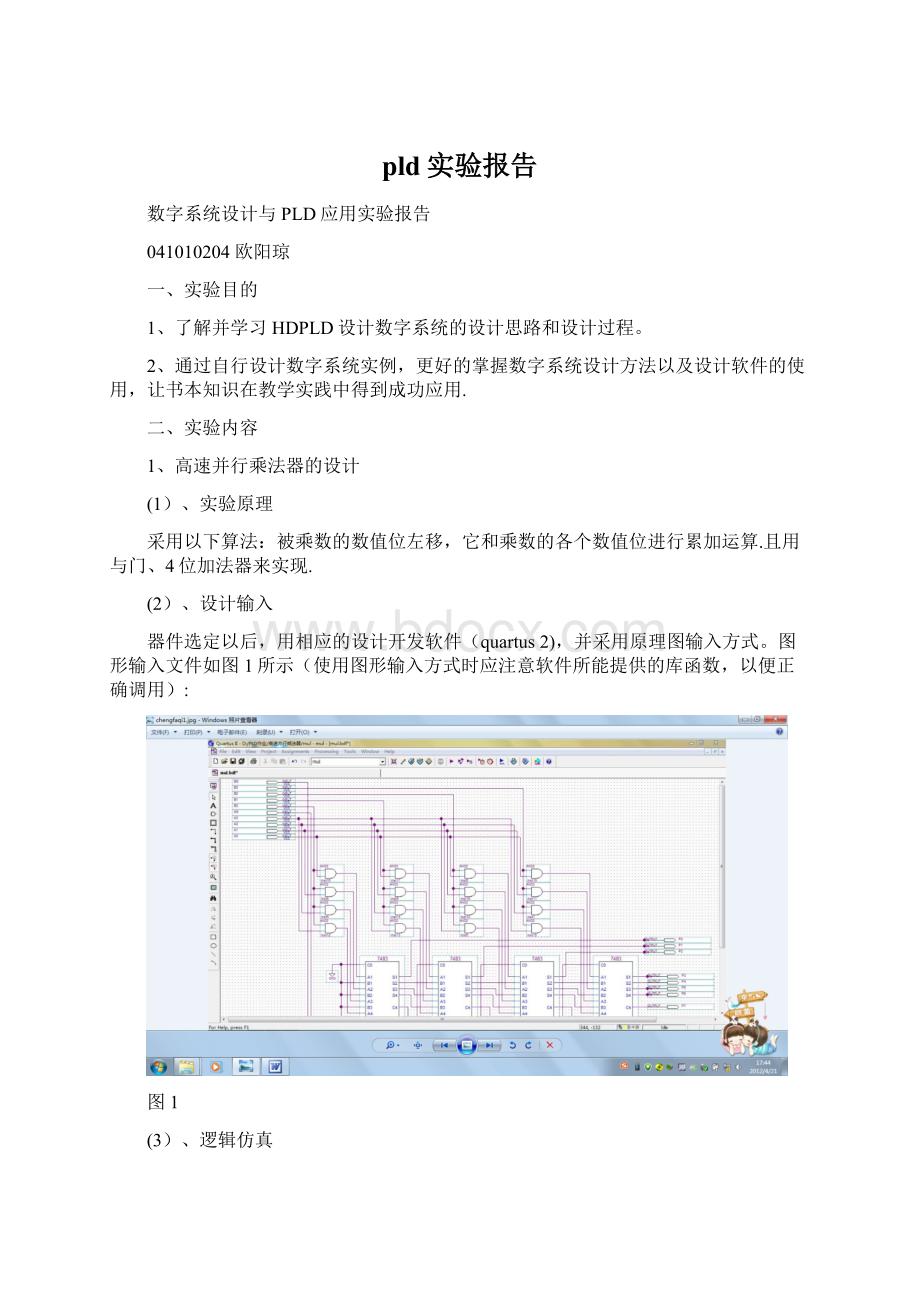

(2)、设计输入

器件选定以后,用相应的设计开发软件(quartus2),并采用原理图输入方式。

图形输入文件如图1所示(使用图形输入方式时应注意软件所能提供的库函数,以便正确调用):

图1

(3)、逻辑仿真

逻辑仿真是设计校验的重要步骤。

本例使用开发软件的波形编辑器直接画出输入激励波形,启动仿真器,得到显示功能仿真的结果如图2所示:

图2

2、十字路口交通管理器的设计

(1)、实验原理

用一片HDPLD和若干外围电路实现十字路口交通管理器。

该管理器控制甲乙两道的的红黄绿三色灯,指挥车辆和行人安全通行。

该交通管理器是由控制器和受其控制的三个定时器及六个交通管理灯组成。

(2)设计输入

本设计采用分层次描述方式,且用图形输入和文本输入结合的方式建立描述文件。

在顶层图形输入文件中的各模块,其功能用第二层次VHDL原文件描述如下:

控制器control源文件

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYtraffic_controlIS

PORT(

clk:

INSTD_LOGIC;

c1,c2,c3:

OUTSTD_LOGIC;

w1,w2,w3:

INSTD_LOGIC;

r1,r2:

OUTSTD_LOGIC;

y1,y2:

OUTSTD_LOGIC;

g1,g2:

OUTSTD_LOGIC;

reset:

INSTD_LOGIC);

ENDtraffic_control;

ARCHITECTUREaOFtraffic_controlIS

TYPESTATE_SPACEIS(S0,S1,S2,S3);

SIGNALstate:

STATE_SPACE;

BEGIN

PROCESS(reset,clk)

BEGIN

IFreset=’1’THEN

state〈=S0;

ELSIF(clk'EVENTANDclk='1')THEN

CASEstateIS

WHENS0=>

IFw1=’1’THEN

state〈=S1;

ENDIF;

WHENS1=>

IFw2='1’THEN

state<=S2;

ENDIF;

WHENS2=〉

IFw3='1'THEN

state<=S3;

ENDIF;

WHENS3=>

IFw2=’1’THEN

state〈=S0;

ENDIF;

ENDCASE;

ENDIF;

ENDPROCESS;

c1〈=’1’WHENstate=S0ELSE’0';

c2<=’1'WHENstate=S1ORstate=S3ELSE’0’;

c3〈=’1’WHENstate=S2ELSE'0';

r1<=’1’WHENstate=S1ORstate=S0ELSE’0’;

y1〈=’1'WHENstate=S3ELSE’0’;

g1〈=’1’WHENstate=S2ELSE’0’;

r2〈=’1'WHENstate=S2ORstate=S3ELSE’0’;

y2〈=’1’WHENstate=S1ELSE'0';

g2<=’1'WHENstate=S0ELSE’0’;

ENDa;

模30计数器

LIBRARYIEEE;

USEIEEE。

STD_LOGIC_1164.ALL;

ENTITYcount30IS

PORT(

clk:

INSTD_LOGIC;

enable:

INSTD_LOGIC;

c:

OUTSTD_LOGIC);

ENDcount30;

ARCHITECTUREaOFcount30IS

BEGIN

PROCESS(clk)

VARIABLEcnt:

INTEGERRANGE30DOWNTO0;

BEGIN

IF(clk’EVENTANDclk='1')THEN

IFenable='1’ANDcnt<30THEN

cnt:

=cnt+1;

ELSEcnt:

=0;

ENDIF;

ENDIF;

IFcnt=30THEN

C〈='1’;

ELSEC<='0’;

ENDIF;

ENDPROCESS;

ENDa;

模5计数器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYcount05IS

PORT(

clk:

INSTD_LOGIC;

enable:

INSTD_LOGIC;

c:

OUTSTD_LOGIC);

ENDcount05;

ARCHITECTUREaOFcount05IS

BEGIN

PROCESS(clk)

VARIABLEcnt:

INTEGERRANGE05DOWNTO0;

BEGIN

IF(clk'EVENTANDclk='1')THEN

IFenable=’1’ANDcnt<05THEN

cnt:

=cnt+1;

ELSEcnt:

=0;

ENDIF;

ENDIF;

IFcnt=05THEN

C〈='1’;

ELSEC<='0';

ENDIF;

ENDPROCESS;

ENDa;

模26计数器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164。

ALL;

ENTITYcount26IS

PORT(

clk:

INSTD_LOGIC;

enable:

INSTD_LOGIC;

c:

OUTSTD_LOGIC);

ENDcount26;

ARCHITECTUREaOFcount26IS

BEGIN

PROCESS(clk)

VARIABLEcnt:

INTEGERRANGE26DOWNTO0;

BEGIN

IF(clk’EVENTANDclk='1')THEN

IFenable=’1’ANDcnt〈26THEN

cnt:

=cnt+1;

ELSEcnt:

=0;

ENDIF;

ENDIF;

IFcnt=26THEN

C<=’1’;

ELSEC<='0’;

ENDIF;

ENDPROCESS;

ENDa;

其电路图如图3所示:

图3

(3)、逻辑仿真

仿真结果波形文件如图4所示:

图4

3、九九乘法表系统的设计

(1)、设计输入

对于此较复杂的系统,采用层次化设计思路.首先,建立VHDL文本输入文件:

程序包PLUS_LIB的描述源文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

PACKAGEPLUS_LIBIS

COMPONENTPLUSCONTROL

PORT(CLK:

INSTD_LOGIC;

START,ARH,TT,EE:

INSTD_LOGIC;

DONE,CRT,S,ENT:

OUTSTD_LOGIC);

ENDCOMPONENT;

COMPONENTCOUNT8

PORT(CLK:

INSTD_LOGIC;

CRT,ENT:

INSTD_LOGIC;

TT:

OUTSTD_LOGIC);

ENDCOMPONENT;

COMPONENTCNT1

PORT(CLK:

INSTD_LOGIC;

CRT:

INSTD_LOGIC;

OC:

OUTSTD_LOGIC;

QA:

OUTINTEGERRANGE0TO9);

ENDCOMPONENT;

COMPONENTCNT2

PORT(CLK:

INSTD_LOGIC;

CRT:

INSTD_LOGIC;

EN2:

INSTD_LOGIC;

EE:

OUTSTD_LOGIC;

QB:

OUTINTEGERRANGE0TO9);

ENDCOMPONENT;

COMPONENTMUX1

PORT(BB,QB:

ININTEGERRANGE0TO9;

S:

INSTD_LOGIC;

B:

OUTINTEGERRANGE0TO9);

ENDCOMPONENT;

COMPONENTMUX2

PORT(AA,QA:

ININTEGERRANGE0TO9;

S:

INSTD_LOGIC;

A:

OUTINTEGERRANGE0TO9);

ENDCOMPONENT;

系统顶层设计的源文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164。

ALL;

USEWORK.PLUS_LIB.ALL;

ENTITYPLUS_TOPIS

PORT(CLK:

INSTD_LOGIC;

AA,BB:

ININTEGERRANGE0TO9;

A,B:

BUFFERINTEGERRANGE0TO9;

EE,OC:

BUFFERSTD_LOGIC;

BD1,BD2:

OUTINTEGERRANGE0TO9;

START,ARH:

INSTD_LOGIC);

ENDPLUS_TOP;

ARCHITECTUREXYBOFPLUS_TOPIS

SIGNALENT,CRT,DONE,S,TT:

STD_LOGIC;

SIGNALQA,QB,TA,TB:

INTEGERRANGE0TO9;

SIGNALM:

INTEGERRANGE0TO81;

BEGIN

A<=TA;

B〈=TB;

CONTROL:

PLUSCONTROL

PORTMAP(CLK,START,ARH,TT,EE,DONE,CRT,S,ENT);

COUNT1:

COUNT8

PORTMAP(CLK,CRT,ENT,TT);

COUNT2:

CNT1

PORTMAP(CLK,CRT,OC,QA);

COUNT3:

CNT2

PORTMAP(CLK,CRT,OC,EE,QB);

M1:

MUX1

PORTMAP(BB,QB,S,TB);

M2:

MUX2

PORTMAP(AA,QA,S,TA);

P1:

PLUS

PORTMAP(TA,TB,M);

P2:

TRANS

PORTMAP(M,BD1,BD2);

ENDXYB;

系统第二层描述含较多模块的VHDL源文件,分别如下所示:

LIBRARYIEEE;

USEIEEE。

STD_LOGIC_1164。

ALL;

ENTITYCNT1IS

PORT(CLK:

INSTD_LOGIC;

CRT:

INSTD_LOGIC;

OC:

OUTSTD_LOGIC;

QA:

OUTINTEGERRANGE0TO9);

END;

ARCHITECTUREXYBOFCNT1IS

BEGIN

PROCESS(CLK)

VARIABLECOUNT:

INTEGERRANGE0TO9;

BEGIN

IFCLK'EVENTANDCLK='1’THEN

IFCRT=’1'THEN

IFCOUNT=9THEN

COUNT:

=0;

OC<='0’;

ELSIFCOUNT=8THEN

COUNT:

=COUNT+1;

OC〈='1’;

ELSE

COUNT:

=COUNT+1;

OC<='0’;

ENDIF;

ENDIF;

ENDIF;

QA〈=COUNT;

ENDPROCESS;

ENDXYB;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYCNT2IS

PORT(CLK:

INSTD_LOGIC;

CRT:

INSTD_LOGIC;

EN2:

INSTD_LOGIC;

EE:

OUTSTD_LOGIC;

QB:

OUTINTEGERRANGE0TO9);

END;

ARCHITECTUREXYBOFCNT2IS

BEGIN

PROCESS(CLK)

VARIABLECOUNT:

INTEGERRANGE0TO9;

BEGIN

IFCLK'EVENTANDCLK=’1'THEN

IFCRT=’1'THEN

IFEN2=’1'THEN

IFCOUNT=9THEN

COUNT:

=0;

EE〈=’1';

ELSE

COUNT:

=COUNT+1;

ENDIF;

ELSE

EE<=’0';

ENDIF;

ENDIF;

ENDIF;

QB<=COUNT;

ENDPROCESS;

ENDXYB;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYCOUNT8IS

PORT(CLK:

INSTD_LOGIC;

CRT,ENT:

INSTD_LOGIC;

TT:

OUTSTD_LOGIC);

END;

ARCHITECTUREXYBOFCOUNT8IS

BEGIN

PROCESS(CLK)

VARIABLECOUNT:

INTEGERRANGE0TO7;

BEGIN

IFCLK’EVENTANDCLK='1’THEN

IFCRT=’1’ANDENT='1'THEN

IFCOUNT=7THEN

COUNT:

=0;

TT〈=’1’;

ELSE

COUNT:

=COUNT+1;

TT<='0';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDXYB;

LIBRARYIEEE;

USEIEEE。

STD_LOGIC_1164.ALL;

ENTITYMUX1IS

PORT(BB,QB:

ININTEGERRANGE0TO9;

S:

INSTD_LOGIC;

B:

OUTINTEGERRANGE0TO9

);

ENDMUX1;

ARCHITECTUREXYBOFMUX1IS

BEGIN

B<=QBWHENS=’1’ELSEBB;

ENDXYB;

LIBRARYIEEE;

USEIEEE。

STD_LOGIC_1164。

ALL;

ENTITYMUX2IS

PORT(AA,QA:

ININTEGERRANGE0TO9;

S:

INSTD_LOGIC;

A:

OUTINTEGERRANGE0TO9

);

ENDMUX2;

ARCHITECTUREXYBOFMUX2IS

BEGIN

A〈=QAWHENS='1'ELSEAA;

ENDXYB;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164。

ALL;

ENTITYplusIS

PORT(a:

ININTEGERRANGE0TO9;

b:

ININTEGERRANGE0TO9;

m:

OUTINTEGERRANGE0TO81);

ENDplus;

ARCHITECTUREXYBOFplusIS

BEGIN

m<=a*b;

ENDXYB;

LIBRARYIEEE;

USEIEEE。

STD_LOGIC_1164。

ALL;

ENTITYPLUSCONTROLIS

PORT(CLK:

INSTD_LOGIC;

START,ARH,TT,EE:

INSTD_LOGIC;

DONE,CRT,S,ENT:

OUTSTD_LOGIC);

ENDPLUSCONTROL;

ARCHITECTUREXYBOFPLUSCONTROLIS

TYPESTATE_SPACEIS(S0,S1,S2,S3);

SIGNALSTATE:

STATE_SPACE;

BEGIN

PROCESS(CLK)

BEGIN

IFCLK’EVENTANDCLK=’1’THEN

CASESTATEIS

WHENS0=>

IFSTART='1'THEN

STATE〈=S1;

ENDIF;

WHENS1=>

IFARH=’1’THEN

STATE<=S3;

ELSE

STATE〈=S2;

ENDIF;

WHENS2=〉

IFTT=’1’THEN

STATE<=S0;

ELSE

STATE〈=S2;

ENDIF;

WHENS3=>

IFEE=’1'THEN

STATE〈=S1;

ENDIF;

ENDCASE;

ENDIF;

ENDPROCESS;

DONE<='1'WHENSTATE=S0ELSE'0';

CRT〈=’0’WHENSTATE=S0ELSE'1';

S〈=’1'WHENSTATE=S3ELSE'0';

ENT〈='1’WHENSTATE=S2ELSE'0’;

ENDXYB;

LIBRARYIEEE;

USEIEEE。

STD_LOGIC_1164。

ALL;

ENTITYtransIS

PORT(m:

ININTEGERRANGE0TO81;

bd2,bd1:

outINTEGERRANGE0TO9);

ENDtrans;

ARCHITECTUREXYBOFtransIS

BEGIN

process(m)

begin

ifm<=9then

bd2〈=0;

bd1〈=m;

elsifm<=19then

bd2<=1;

bd1<=m—10;

elsifm<=29then

bd2<=2;

bd1〈=m—20;

elsifm〈=39then

bd2〈=3;

bd1〈=m-30;

elsifm<=49then

bd2〈=4;

bd1〈=m—40;

elsifm<=59then

bd2<=5;

bd1〈=m—50;

elsifm〈=69then

bd2〈=6;

bd1<=m—60;

elsifm〈=79then

bd2<=7;

bd1〈=m—70;

else

bd2〈=8;

bd1<=m-80;

endif;

endprocess;

endxyb;

本题的实验电路如图5所示

图5

(2)、逻辑仿真

设计输入文件经适当的软件开发系统编译处理,由功能仿真器进行逻辑模拟,获得该电路仿真结果如图6所示:

图6

三、实验心得

通过这三个数字系统的设计,我学会了用QUARTUS2这个软件,利用它进行数字系统的设计与仿真。

这三个实验由简到繁,由易到难,由功能电路到系统的原则排序,有些实例给出图形,有些是VHDL文本输入方式,有些是图形文本结合。

多种多样的设计方法让我更好更熟练的掌握了数字系统设计软件的操作与应用。