计算机组织与系统结构第四章习题答案.docx

《计算机组织与系统结构第四章习题答案.docx》由会员分享,可在线阅读,更多相关《计算机组织与系统结构第四章习题答案.docx(19页珍藏版)》请在冰豆网上搜索。

计算机组织与系统结构第四章习题答案

第4章习题答案

3.已知某机主存空间大小为64KB,按字节编址。

要求:

〔1〕假设用1K×4位的SRAM芯片构成该主存储器,需要多少个芯片?

〔2〕主存地址共多少位?

几位用于选片?

几位用于片内选址?

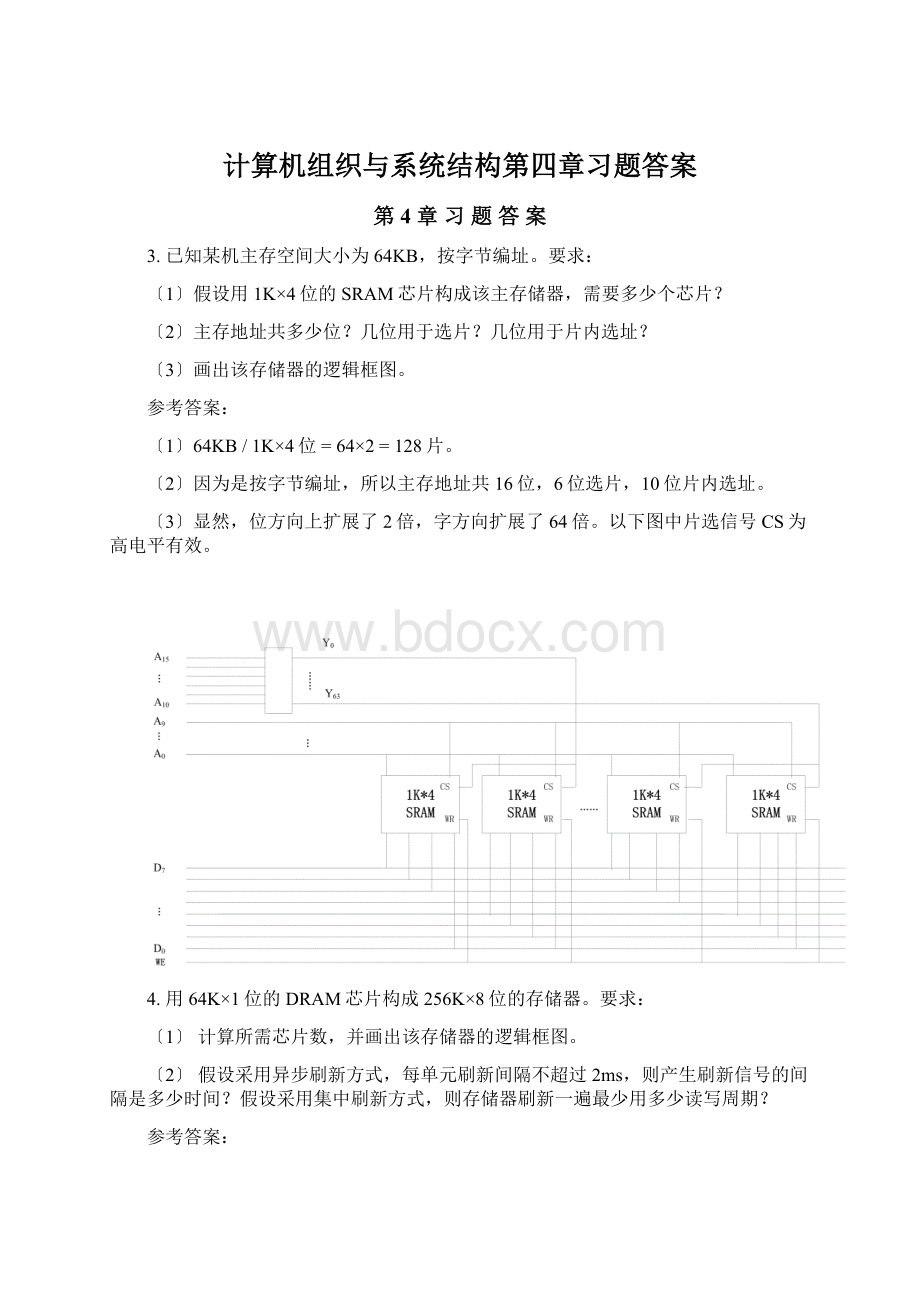

〔3〕画出该存储器的逻辑框图。

参考答案:

〔1〕64KB/1K×4位=64×2=128片。

〔2〕因为是按字节编址,所以主存地址共16位,6位选片,10位片内选址。

〔3〕显然,位方向上扩展了2倍,字方向扩展了64倍。

以下图中片选信号CS为高电平有效。

4.用64K×1位的DRAM芯片构成256K×8位的存储器。

要求:

〔1〕计算所需芯片数,并画出该存储器的逻辑框图。

〔2〕假设采用异步刷新方式,每单元刷新间隔不超过2ms,则产生刷新信号的间隔是多少时间?

假设采用集中刷新方式,则存储器刷新一遍最少用多少读写周期?

参考答案:

〔1〕256KB/64K×1位=4×8=32片。

存储器逻辑框图见下页〔图中片选信号CS为高电平有效〕。

〔2〕因为每个单元的刷新间隔为2ms,所以,采用异步刷新时,在2ms内每行必须被刷新一次,且仅被刷新一次。

因为DRAM芯片存储阵列为64K=256×256,所以一共有256行。

因此,存储器控制器必须每隔产生一次刷新信号。

采用集中刷新方式时,整个存储器刷新一遍需要256个存储〔读写〕周期,在这个过程中,存储器不能进行读写操作。

5.用8K×8位的EPROM芯片组成32K×16位的只读存储器,试问:

〔1〕数据寄存器最少应有多少位?

〔2〕地址寄存器最少应有多少位?

〔3〕共需多少个EPROM芯片?

〔4〕画出该只读存储器的逻辑框图。

参考答案:

〔1〕数据寄存器最少有16位。

〔2〕地址寄存器最少有:

15位〔假设按16位的字编址〕;16位〔假设按字节编址〕。

〔3〕共需要32K×16位/8K×8位=4×2=8片。

〔4〕该只读存储器的逻辑框图如下〔假定按字编址,图中片选信号CS为高电平有效〕。

6.某电脑中已配有0000H~7FFFH的ROM区域,现在再用8K×4位的RAM芯片形成32K×8位的存储区域,CPU地址总线为A0-A15,数据总线为D0-D7,控制信号为R/W#〔读/写〕、MREQ#〔访存〕。

要求说明地址译码方案,并画出ROM芯片、RAM芯片与CPU之间的连接图。

假定上述其他条件不变,只是CPU地址线改为24根,地址范围000000H~007FFFH为ROM区,剩下的所有地址空间都用8K×4位的RAM芯片配置,则需要多少个这样的RAM芯片?

参考答案:

CPU地址线共16位,故存储器地址空间为0000H~FFFFH,其中,8000H~FFFFH为RAM区,共215=32K个单元,其空间大小为32KB,故需8K×4位的芯片数为32KB/8K×4位=4×2=8片。

因为ROM区在0000H~7FFFH,RAM区在8000H~FFFFH,所以可通过最高位地址A15来区分,当A15为0时选中ROM芯片;为1时选中RAM芯片,此时,根据A14和A13进行译码,得到4个译码信号,分别用于4组字扩展芯片的片选信号。

〔图略,可参照图4.15〕

假设CPU地址线为24位,ROM区为000000H~007FFFH,则ROM区大小为32KB,总大小为16MB=214KB=512×32KB,所以RAM区大小为511×32KB,共需使用RAM芯片数为511×32KB/8K×4位=511×4×2个芯片。

7.假定一个存储器系统支持4体交叉存取,某程序执行过程中访问地址序列为3,9,17,2,51,37,13,4,8,41,67,10,则哪些地址访问会发生体冲突?

参考答案:

对于4体交叉访问的存储系统,每个存储模块的地址分布为:

Bank0:

0、4、8、12、16……

Bank1:

1、5、9、13、17…37…41…

Bank2:

2、6、10、14、18……

Bank3:

3、7、11、15、19…51…67

如果给定的访存地址在相邻的4次访问中出现在同一个Bank内,就会发生访存冲突。

所以,17和9、37和17、13和37、8和4发生冲突。

8.现代电脑中,SRAM一般用于实现快速小容量的cache,而DRAM用于实现慢速大容量的主存。

以前超级电脑通常不提供cache,而是用SRAM来实现主存〔如,Cray巨型机〕,请问:

如果不考虑成本,你还这样设计高性能电脑吗?

为什么?

参考答案:

不这样做的理由主要有以下两个方面:

主存越大越好,主存大,缺页率降低,因而减少了访问磁盘所需的时间。

显然用DRAM芯片比用SRAM芯片构成的主存容量大的多。

程序访问的局部性特点使得cache的命中率很高,因而,即使主存没有用快速的SRAM芯片而是用DRAM芯片,也不会影响到访问速度。

9.分别给出具有以下要求的程序或程序段的例如:

〔1〕对于数据的访问,几乎没有时间局部性和空间局部性。

〔2〕对于数据的访问,有很好的时间局部性,但几乎没有空间局部性。

〔3〕对于数据的访问,有很好的空间局部性,但几乎没有时间局部性。

〔4〕对于数据的访问,空间局部性和时间局部性都好。

参考答案〔略〕:

可以给出许多类似的例如。

例如,对于按行优先存放在内存的多维数组,如果按列优先访问数组元素,则空间局部性就差,如果在一个循环体中某个数组元素只被访问一次,则时间局部性就差。

10.假定某机主存空间大小1GB,按字节编址。

cache的数据区〔即不包括标记、有效位等存储区〕有64KB,块大小为128字节,采用直接映射和全写〔write-through〕方式。

请问:

〔1〕主存地址如何划分?

要求说明每个字段的含义、位数和在主存地址中的位置。

〔2〕cache的总容量为多少位?

参考答案:

〔1〕主存空间大小为1GB,按字节编址,说明主存地址为30位。

cache共有64KB/128B=512行,因此,行索引〔行号〕为9位;块大小128字节,说明块内地址为7位。

因此,30位主存地址中,高14位为标志〔Tag〕;中间9位为行索引;低7位为块内地址。

〔2〕因为采用直接映射,所以cache中无需替换算法所需控制位,全写方式下也无需修改〔dirty〕位,而标志位和有效位总是必须有的,所以,cache总容量为512×(128×8+14+1)K位。

11.假定某电脑的cache共16行,开始为空,块大小为1个字,采用直接映射方式。

CPU执行某程序时,依次访问以下地址序列:

2,3,11,16,21,13,64,48,19,11,3,22,4,27,6和11。

要求:

〔1〕说明每次访问是命中还是缺失,试计算访问上述地址序列的命中率。

〔2〕假设cache数据区容量不变,而块大小改为4个字,则上述地址序列的命中情况又如何?

参考答案

(1)cache采用直接映射方式,其数据区容量为16行×1字/行=16字;主存被划分成1字/块,所以,主存块号=字号。

因此,映射公式为:

cache行号=主存块号mod16=字号mod16。

开始cache为空,所以第一次都是miss,以下是映射关系〔字号-cache行号〕和命中情况。

2-2:

miss,3-3:

miss,11-11:

miss,16-0:

miss,21-5:

miss,13-13:

miss,64-0:

miss、replace,

48-0:

miss、replace,19-3:

miss、replace,11-11:

hit,3-3:

miss、replace,22-6:

miss,

4-4:

miss,27-11:

miss、replace,6-6:

miss、replace,11-11:

miss、replace。

只有一次命中!

〔2〕cache采用直接映射方式,数据区容量不变,为16个字,每块大小为4个字,所以,cache共有4行;主存被划分为4个字/块,所以,主存块号=[字号/4]。

因此,映射公式为:

cache行号=主存块号mod4=[字号/4]mod4。

以下是映射关系〔字号-主存块号-cache行号〕和命中情况。

2-0-0:

miss,3-0-0:

hit,11-2-2:

miss,16-4-0:

miss、replace,21-5-1、13-3-3:

miss,

64-16-0、48-12-0、19-4-0:

miss,replace,11-2-2:

hit,3-0-0:

miss、replace,

22-5-1:

hit,4-1-1:

miss、replace,27-6-2:

miss、replace,6-1-1:

hit,11-2-2:

miss、replace。

命中4次。

由此可见,块变大后,能有效利用访问的空间局部性,从而使命中率提高!

12.假定数组元素在主存按从左到右的下标顺序存放。

试改变以下函数中循环的顺序,使得其数组元素的访问与排列顺序一致,并说明为什么修改后的程序比原来的程序执行时间短。

intsum_array(inta[N][N][N])

{

inti,j,k,sum=0;

for(i=0;ifor(j=0;jfor(k=0;kreturnsum;

}

参考答案:

intsum_array(inta[N][N][N])

{

inti,j,k,sum=0;

for(k=0;kfor(i=0;ifor(j=0;jreturnsum;

}

修改后程序的数组元素的访问与排列顺序一致,使得空间局部性比原程序好,故执行时间更短。

13.分析比较以下三个函数的空间局部性,并指出哪个最好,哪个最差?

#defineN1000

typedefstruct{

intvel[3];

intacc[3];

}point;

pointp[N];

voidclear3(point*p,intn)

{

inti,j;

for(j=0;j<3;j++){

for(i=0;ip[i].vel[j]=0;

for(i=0;ip[i].acc[j]=0;

}

}

参考答案:

对于函数clear1,其数组访问顺序与在内存的存放顺序完全一致,因此,空间局部性最好。

对于函数clear2,其数组访问顺序在每个数组元素内跳越式访问,相邻两次访问的单元最大相差3个int型变量〔假定sizeof(int)=4,则相当于12B〕,因此空间局部性比clear1差。

假设主存块大小比12B小的话,则大大影响命中率。

对于函数clear3,其数组访问顺序与在内存的存放顺序不一致,相邻两次访问的单元都相差6个int型变量〔假定sizeof(int)=4,则相当于24B〕因此,空间局部性比clear2还差。

假设主存块大小比24B小的话,则大大影响命中率。

14.以下是计算两个向量点积的程序段:

floatdotproduct(floatx[8],floaty[8])

{

floatsum=0.0;

inti,;

for(i=0;i<8;i++)sum+=x[i]*y[i];

returnsum;

}

要求:

〔1〕试分析该段代码中数组x和y的时间局部性和空间局部性,并推断命中率的高低。

〔2〕假定该段程序运行的电脑的数据cache采用直接映射方式,其数据区容量为32字节,每个主存块大小为16字节。

假定编译程序将变量sum和i分配给寄存器,数组x存放在00000040H开始的32字节的连续存储区中,数组y紧跟在x后进行存放。

试计算该程序数据访问的命中率,要求说明每次访问的cache命中情况。

〔3〕将上述〔2〕中的数据cache改用2-路组相联映射方式,块大小改为8字节,其他条件不变,则该程序数据访问的命中率是多少?

〔4〕在上述〔2〕中条件不变的情况下,如果将数组x定义为float[12],则数据访问的命中率是多少?

参考答案:

〔1〕数组x和y都按存放顺序访问,不考虑映射的情况下,空间局部性都较好,但都只被访问一次,故没有时间局部性。

命中率的高低与块大小、映射方式等都有关,所以,无法推断命中率的高低。

〔2〕cache采用直接映射方式,块大小为16字节,数据区大小为32字节,故cache共有2行。

数组x的8个元素〔共32B〕分别存放在主存40H开始的32个单元中,共有2个主存块,其中x[0]~x[3]在第4块,x[4]~x[7]在第5块中;数组y的8个元素〔共32B〕分别在主存第6块和第7块中。

所以,x[0]~x[3]和y[0]~y[3]都映射到cache第0行;

x[4]~x[7]和y[4]~y[7]都映射到cache第1行。

cache

第0-3次循环

第4-7次循环

第0行

x[0-3],y[0-3]

第1行

x[4-7],y[4-7]

每调入一块,装入4个数组元素,因为x[i]和y[i]总是映射到同一行,相互淘汰对方,故每次都不命中,命中率为0.

〔3〕改用2路组相联,块大小为8B,则cache共有4行,每组两行,共两组。

数组x有4个主存块,x[0]~x[1]、x[2]~x[3],x[4]~x[5],x[6]~x[7]分别在第8~11块中;

数组y有4个主存块,y[0]~y[1]、y[2]~y[3],y[4]~y[5],y[6]~y[7]分别在第12~15块中;

cache

第0行

第1行

第0组

x[0-1],x[4-5]

y[0-1],y[4-5]

第1组

x[2-3],x[6-7]

y[2-3],y[6-7]

每调入一块,装入两个数组元素,第二个数组元素的访问总是命中,故命中率为50%。

〔4〕假设〔2〕中条件不变,数组x定义了12个元素,共有48B,使得y从第7块开始,因而,x[i]和y[i]就不会映射到同一个cache行中,即:

x[0]~x[3]在第4块,x[4]~x[7]在第5块,x[8]~x[11]在第6块中,y[0]~y[3]在第7块,y[4]~x[7]在第8块。

cache

第0-3次循环

第4-7次循环

第0行

x[0-3]

y[4-7]

第1行

y[0-3]

x[4-7]

每调入一块,装入4个数组元素,第一个元素不命中,后面3个总命中,故命中率为75%。

15.以下是对矩阵进行转置的程序段:

typedefintarray[4][4];

voidtranspose(arraydst,arraysrc)

{

inti,j;

for(i=0;i<4;i++)

for(j=0;j<4;j++)

dst[j][i]=src[i][j];

}

假设该段程序运行的电脑中sizeof(int)=4,且只有一级cache,其中L1datacache的数据区大小为32B,采用直接映射、写回方式,块大小为16B,初始为空。

数组dst从地址0000C000H开始存放,数组src从地址0000C040H开始存放。

填写下表,说明数组元素src[row][col]和dst[row][col]映射到cache的哪一行,其访问是命中〔hit〕还是失效〔miss〕。

假设L1datacache的数据区容量改为128B时,重新填写表中内容。

src数组

dst数组

32B

col=0

col=1

col=2

col=3

col=0

col=1

col=2

col=3

row=0

0/miss

0/miss

0/hit

0/miss

0/miss

0/miss

0/miss

0/miss

row=1

1/miss

1/hit

1/miss

1/hit

1/miss

1/miss

1/miss

1/miss

row=2

0/miss

0/miss

0/hit

0/miss

0/miss

0/miss

0/miss

0/miss

row=3

1/miss

1/hit

1/miss

1/hit

1/miss

1/miss

1/miss

1/miss

src数组

dst数组

128B

col=0

col=1

col=2

col=3

col=0

col=1

col=2

col=3

row=0

4/miss

4/hit

4/hit

4/hit

0/miss

0/hit

0/hit

0/hit

row=1

5/miss

5/hit

5/hit

5/hit

1/miss

1/hit

1/hit

1/hit

row=2

6/miss

6/hit

6/hit

6/hit

2/miss

2/hit

2/hit

2/hit

row=3

7/miss

7/hit

7/hit

7/hit

3/miss

3/hit

3/hit

3/hit

参考答案:

从程序来看,数组访问过程如下:

src[0][0]、dst[0][0]、src[0][1]、dst[1][0]、src[0][2]、dst[2][0]、src[0][3]、dst[3][0]

src[1][0]、dst[0][1]、src[1][1]、dst[1][1]、src[1][2]、dst[2][1]、src[1][3]、dst[3][1]

src[2][0]、dst[0][2]、src[2][1]、dst[1][2]、src[2][2]、dst[2][2]、src[2][3]、dst[3][2]

src[3][0]、dst[0][3]、src[3][1]、dst[1][3]、src[3][2]、dst[2][3]、src[3][3]、dst[3][3]

因为块大小为16B,每个数组元素有4个字节,所以4个数组元素占一个主存块,因此每次总是调入4个数组元素到cache的一行。

当数据区容量为32B时,L1datacache中共有2行。

数组元素dst[0][i]、dst[2][i]、src[0][i]、src[2][i](i=0~3)都映射到cache第0行,数组元素dst[1][i]、dst[3][i]、src[1][i]、src[3][i](i=0~3)都映射到cache第1行。

因此,从上述访问过程来看,src[0][0]所在的一个主存块〔即存放src[0][i](i=0~3)四个数组元素〕刚调入cache后,dst[0][0]所在主存块又把src[0][0]替换掉了。

……

当数据区容量为128B时,L1datacache中共有8行。

数组元素dst[0][i]、dst[1][i]、dst[2][i]、dst[3][i]、src[0][i]、src[1][i]、src[2][i]、src[3][i](i=0~3)分别映射到cache第0、1、2、3、4、5、6、7行。

因此,不会发生数组元素的替换。

每次总是第一个数组元素不命中,后面三个数组元素都命中。

16.通过对方格中每个点设置相应的CMYK值就可以将方格图上相应的颜色。

以下三个程序段都可实现对一个8×8的方格中图上黄色的功能。

程序段A程序段B程序段C

假设cache的数据区大小为512B,采用直接映射,块大小为32B,存储器按字节编址,sizeof(int)=4。

编译时变量i和j分配在寄存器中,数组square按行优先方式存放在000008C0H开始的连续区域中,主存地址为32位。

要求:

(1)对三个程序段A、B、C中数组访问的时间局部性和空间局部性进行分析比较。

(2)画出主存中的数组元素和cache中行的对应关系图。

(3)计算三个程序段A、B、C中的写操作次数、写不命中次数和写缺失率。

参考答案:

〔1〕对于时间局部性来说:

程序段A、B和C中,都是每个数组元素只被访问一次,所以都没有时间局部性;

对于空间局部性来说:

程序段A访问顺序和存放顺序一致,所以,空间局部性好;

程序段B访问顺序和存放顺序不一致,所以,空间局部性不好;

程序段C虽然访问顺序和存放顺序一致,但同一个主存块有两次访问,所以空间局部性不好;

〔2〕cache的行数为512B/32B=16;数组首地址为00000C80H,因为00000C80H正好是主存第1100100B〔100〕块的起始地址。

所以数组从主存第100块开始存放,一个数组元素占4×4B=16B,所以每2个数组元素占用一个主存块。

8×8的数组共占用32个主存块,正好是cache数据区大小的2倍。

主存中的数组元素与cache行的映射关系图如下:

Cache行号

〔3〕对于程序段A:

每两个数组元素〔共涉及8次写操作〕装入到一个cache行中,总是第一次访问时未命中,后面7次都命中,所以,总的写操作次数为64×4=256次,写不命中次数为256×1/8=32次,因而写缺失率为12.5%。

对于程序段B:

每两个数组元素〔共涉及8次写操作〕装入到一个cache行中,但总是只有一个数组元素〔涉及4次写操作〕在被淘汰之前被访问,并且总是第一次不命中,后面3次命中。

即写不命中次数为256×1/4=64次,因而写缺失率为25%。

对于程序段C:

第一个循环共64次访问,每次装入两个数组元素,第一次不命中,第二次命中;第二个循环,共访问64×3次,每两个数组元素〔共涉及6次写操作〕装入到一个cache行中,并且总是第一次不命中,后面5次命中。

所以总的写不命中次数为32+(3×64)×1/6=64次,因而总缺失率为25%。

17.假设某电脑的主存地址空间大小为64MB,采用字节编址方式。

其cache数据区容量为4KB,采用4路组相联映射方式、LRU替换和回写〔writeback〕策略,块大小为64B。

请问:

〔1〕主存地址字段如何划分?

要求说明每个字段的含义、位数和在主存地址中的位置。

〔2〕该cache的总容量有多少位?

〔3〕假设cache初始为空,CPU依次从0号地址单元顺序访问到4344号单元,重复按此序列共访问16次。

假设cache命中时间为1个时钟周期,缺失损失为10个时钟周期,则CPU访存的平均时间为多少时钟周期?

参考答案:

〔1〕cache的划分为:

4KB=212B=24组×22行/组×26字节/行,所以,cache组号〔组索引〕占4位。

主存地址划分为三个字段:

高16位为标志字段、中间4位为组号、最低6位为块内地址。

即主存空间划分为:

64MB=226B=216组群×24块/组群×26字节/块

〔2〕cache共有64行,每行中有16位标志、1位有效位、1位修改(dirty)位、2位LRU位,以及