超大规模集成电路第四次作业秋段成华.docx

《超大规模集成电路第四次作业秋段成华.docx》由会员分享,可在线阅读,更多相关《超大规模集成电路第四次作业秋段成华.docx(8页珍藏版)》请在冰豆网上搜索。

超大规模集成电路第四次作业秋段成华

超大规模集成电路第四次作业2016秋-段成华

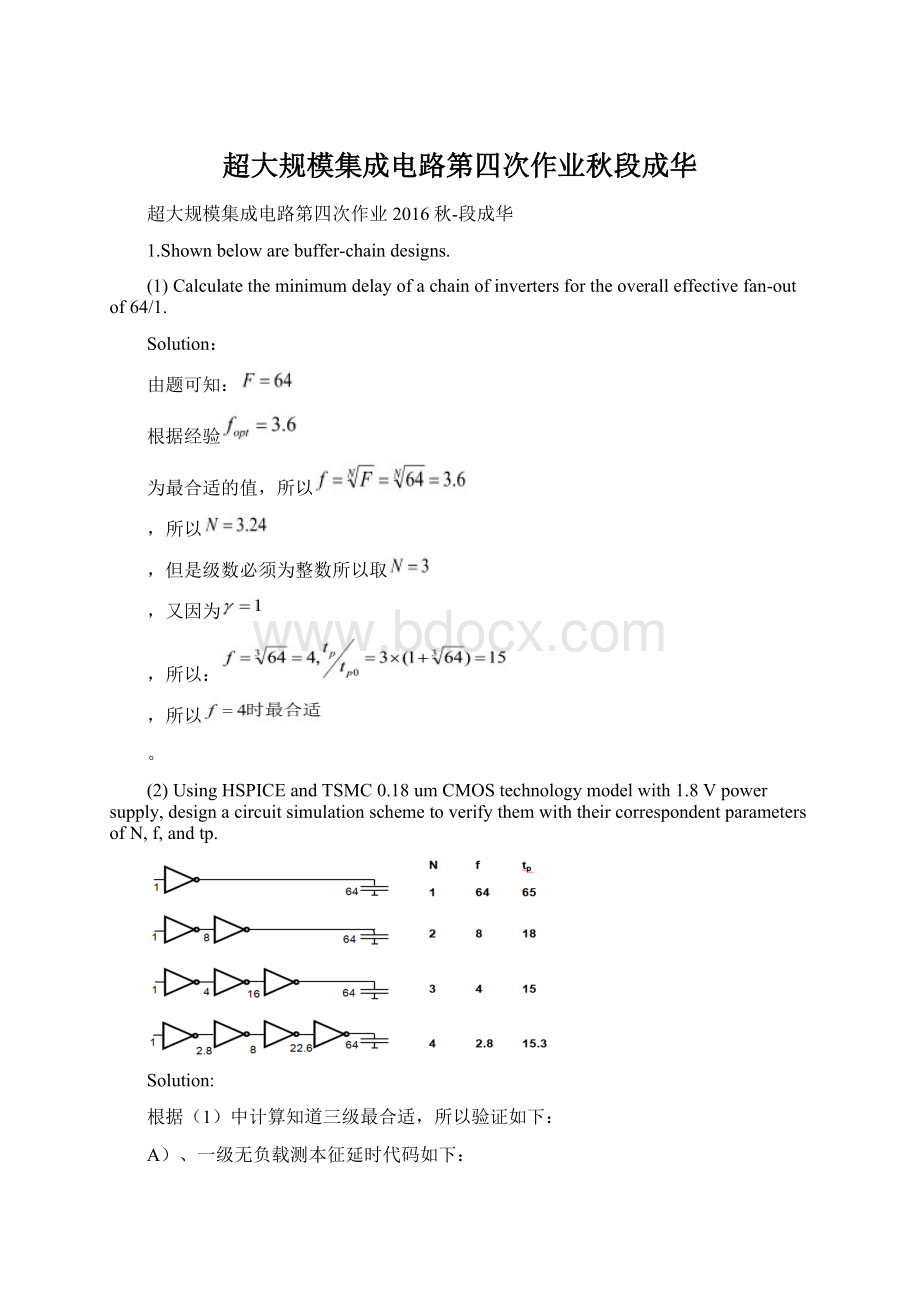

1.Shownbelowarebuffer-chaindesigns.

(1)Calculatetheminimumdelayofachainofinvertersfortheoveralleffectivefan-outof64/1.

Solution:

由题可知:

根据经验

为最合适的值,所以

,所以

,但是级数必须为整数所以取

,又因为

,所以:

,所以

。

(2)UsingHSPICEandTSMC0.18umCMOStechnologymodelwith1.8Vpowersupply,designacircuitsimulationschemetoverifythemwiththeircorrespondentparametersofN,f,andtp.

Solution:

根据

(1)中计算知道三级最合适,所以验证如下:

A)、一级无负载测本征延时代码如下:

.titlebuffer-chain1

.lib'C:

\synopsys\Hspice_D-2010.03-SP1\tsmc018\mm018.l'TT*set0.18umlibrary

.optscale=0.1u*setlambda

.optionspost=2list

.temp27

.globalvdd

+targv(vout)

+val='0.5*(voutmax-voutmin)+voutmin'

+rise=1

.end

1)一级无负载测得本征延时约为17ps;

2)带上64倍Cg1大小的负载测得延时为750.35ps,是本征延时的44倍

B)、三级带负载测延时代码如下:

.titlebuffer-chain3

.lib'C:

\synopsys\Hspice_D-2010.03-SP1\tsmc018\mm018.l'TT*set0.18umlibrary

.optscale=0.1u*setlambda

.optionspost=2list

.temp27

.globalvdd

.paramfan=4

Vddvddgnd1.8

vinvin00.9pulse01.825n5p5p49.99n100n

Clvoutgnd0f$Cg1=2.46fF,负载为CL=157.44fF

.subcktinvinoutwn=3.5wp=10t=7.5

mnoutingndgndNCHl=2w=wnad='wn*t'pd='wn+2*t'as='wn*t'ps='wn+2*t'

mpoutinvddvddPCHl=2w=wpad='wp*t'pd='wp+2*t'as='wp*t'ps='wp+2*t'

.ends

X1vin2invwn=3.5wp=10t=7.5

X223invwn='fan*3.5'wp='fan*10't=5

X33voutinvwn='fan*fan*3.5'wp='fan*fan*10't=5

.op

.tran50p500n

.meastranvoutmaxmaxv(vout)from=50pto=500n

.meastranvoutminminv(vout)from=50pto=500n

$三级

.meastrantphl3

+trigv(vin)

+val=0.9

+rise=1

+targv(vout)

+val='0.5*(voutmax-voutmin)+voutmin'

+fall=1

.meastrantplh3

+trigv(vin)

+val=0.9

+fall=1

+targv(vout)

+val='0.5*(voutmax-voutmin)+voutmin'

+rise=1

1)带上64倍Cg1大小的负载测得延时为174.6ps,是本征延时的10.27倍

总结如下:

经过调整参数近似时每一级的

,所以经过手工计算得到一级带负载和三级带负载的延时比值为:

,而仿真得到的结果为

,所以符合手工计算的比值,同理其他级的延时代码也是如上的写法,经过仿真得到三级延时最小。

.end

2.Considerthelogicnetworkbelow,whichmayrepresentthecriticalpathofamorecomplexlogicblock.Theoutputofthenetworkisloadedwithacapacitancewhichis5timeslargerthantheinputcapacitanceofthefirstgate,whichisaminimum-sizedinverter.TheeffectivefanoutofthepathhenceequalsF=CL/Cg1=5.

UsingHSPICEandTSMC0.18umCMOStechnologymodelwith1.8Vpowersupply,designacircuitsimulationschemetoverifytheOPTIMAZATIONparametersofg,f,andsforeachoftheinverterandgates.

Solution:

由题得到路径逻辑努力

,由于没有分支B=1,所以

,所以使延时最小的逻辑努力为

,得到如下的扇出系数:

,利用书上公式6.18计算得到尺寸系数

。

电路仿真代码如下:

.titleINV2NAND2NOR

.lib'C:

\synopsys\Hspice_D-2010.03-SP1\tsmc018\mm018.l'TT*set0.18umlibrary

.optionspost=2list

.temp27

.globalvdd

Vddvddgnd1.8

vinvin00.9pulse0.01.8150p5p5p290p600p

C1voutgnd12.3f$Cg1=2.46fF,所以负载为12.3fF

.subcktinv1inoutwn=0.35uwp=1ut=0.75u

mnoutingndgndNCHl=0.2uw=wnad='wn*t'pd='wn+2*t'as='wn*t'ps='wn+2*t'

mpoutinvddvddPCHl=0.2uw=wpad='wp*t'pd='wp+2*t'as='wp*t'ps='wp+2*t'

.ends

.subcktnand3NAND-A1NAND-D1NAND-B1NAND-C1wn='0.35u*1.16'wp='1u*1.16't=0.5u$优化尺寸系数S2

*.subcktnand3NAND-A1NAND-D1NAND-B1NAND-C1wn=0.35uwp=1ut=0.5u$未优化尺寸系数S2

mn3NAND-S2NAND-C1gndgndNCHl=0.2uw=wnad='wn*t'pd='wn+2*t'as='wn*t'ps='wn+2*t'

mn2NAND-S1NAND-B1NAND-S2gndNCHl=0.2uw=wnad='wn*t'pd='wn+2*t'as='wn*t'ps='wn+2*t'

mn1NAND-D1NAND-A1NAND-S1gndNCHl=0.2uw=wnad='wn*t'pd='wn+2*t'as='wn*t'ps='wn+2*t'

mp1NAND-D1NAND-A1vddvddPCHl=0.2uw=wpad='wp*t'pd='wp+2*t'as='wp*t'ps='wp+2*t'

mp2NAND-D1NAND-B1vddvddPCHl=0.2uw=wpad='wp*t'pd='wp+2*t'as='wp*t'ps='wp+2*t'

mp3NAND-D1NAND-C1vddvddPCHl=0.2uw=wpad='wp*t'pd='wp+2*t'as='wp*t'ps='wp+2*t'

.ends

.subcktnor2NOR-A1NOR-D1NOR-B1wn='0.35u*1.34'wp='1u*1.34't=0.5u$优化尺寸系数S3

*.subcktnor2NOR-A1NOR-D1NOR-B1wn=0.35uwp=1ut=0.5u$未优化尺寸系数S3

mn2NOR-D1NOR-B1gndgndNCHl=0.2uw=wnad='wn*t'pd='wn+2*t'as='wn*t'ps='wn+2*t'

mn1NOR-D1NOR-A1gndgndNCHl=0.2uw=wnad='wn*t'pd='wn+2*t'as='wn*t'ps='wn+2*t'

mp1NOR-S1NOR-A1vddvddPCHl=0.2uw=wpad='wp*t'pd='wp+2*t'as='wp*t'ps='wp+2*t'

mp2NOR-D1NOR-B1NOR-S1vddPCHl=0.2uw=wpad='wp*t'pd='wp+2*t'as='wp*t'ps='wp+2*t'

.ends

.subcktinv2inoutwn='0.35u*2.6'wp='1u*2.6't=0.5u$优化尺寸系数S4

*.subcktinv2inoutwn=0.35uwp=1ut=0.5u$未优化尺寸系数S4

mnoutingndgndNCHl=0.2uw=wnad='wn*t'pd='wn+2*t'as='wn*t'ps='wn+2*t'

mpoutinvddvddPCHl=0.2uw=wpad='wp*t'pd='wp+2*t'as='wp*t'ps='wp+2*t'

.ends

X1vin2inv1

X223vddvddnand3

X334gndnor2

X44voutinv2

.op

.tran5p3000p

.meastranvoutmaxmaxv(vout)from=5pto=3000p

.meastranvoutminminv(vout)from=5pto=3000p

.meastrantphl

+trigv(vin)

+val=0.9

+rise=2

+targv(vout)

+val='0.5*(voutmax-voutmin)+voutmin'

+rise=2

.meastrantplh

+trigv(vin)

+val=0.9

+fall=2

+targv(vout)

+val='0.5*(voutmax-voutmin)+voutmin'

+fall=2

.end

$Cg1=2.46fF,所以负载为12.3fF仿真结果如下:

尺寸系数全部优化得到的tphl和tplh

尺寸系数全部未优化得到的tphl和tplh

Vout对比图:

粉线是尺寸系数全部未优化、浅蓝线是尺寸系数未优化的输出电压、绿线是输入电压波形;

从结果上来看,未优化的tphl和tplh均比优化过的tphl和tplh值要小几十个ps,所以计算得到的尺寸系数是有效的减少了总的延时时间。

从最后一个图中也可以直观看到,优化后的波形出现较早而且波形与vin相差不多,而未优化的波形变化较大近乎失真,未优化的波形尤其在频率较高的情况下失真很严重(这里的频率为1.67Ghz)而优化后的结果能良好保持波形并且延时较小。