TMS320x2833x Multichannel Buffered Serial Port McBSP Reference Guide 第二章.docx

《TMS320x2833x Multichannel Buffered Serial Port McBSP Reference Guide 第二章.docx》由会员分享,可在线阅读,更多相关《TMS320x2833x Multichannel Buffered Serial Port McBSP Reference Guide 第二章.docx(13页珍藏版)》请在冰豆网上搜索。

TMS320x2833xMultichannelBufferedSerialPortMcBSPReferenceGuide第二章

第二章McBSPOperation

Thissectionaddressesthefollowingtopics:

1.Datatransferprocess

2.Companding(compressingandexpanding)data

3.Clockingandframingdata

4.Framephases

5.McBSPreception

6.McBSPtransmission

7.InterruptsandDMAeventsgeneratedbyMcBSPs

2.1DataTransferProcessofMcBSPs

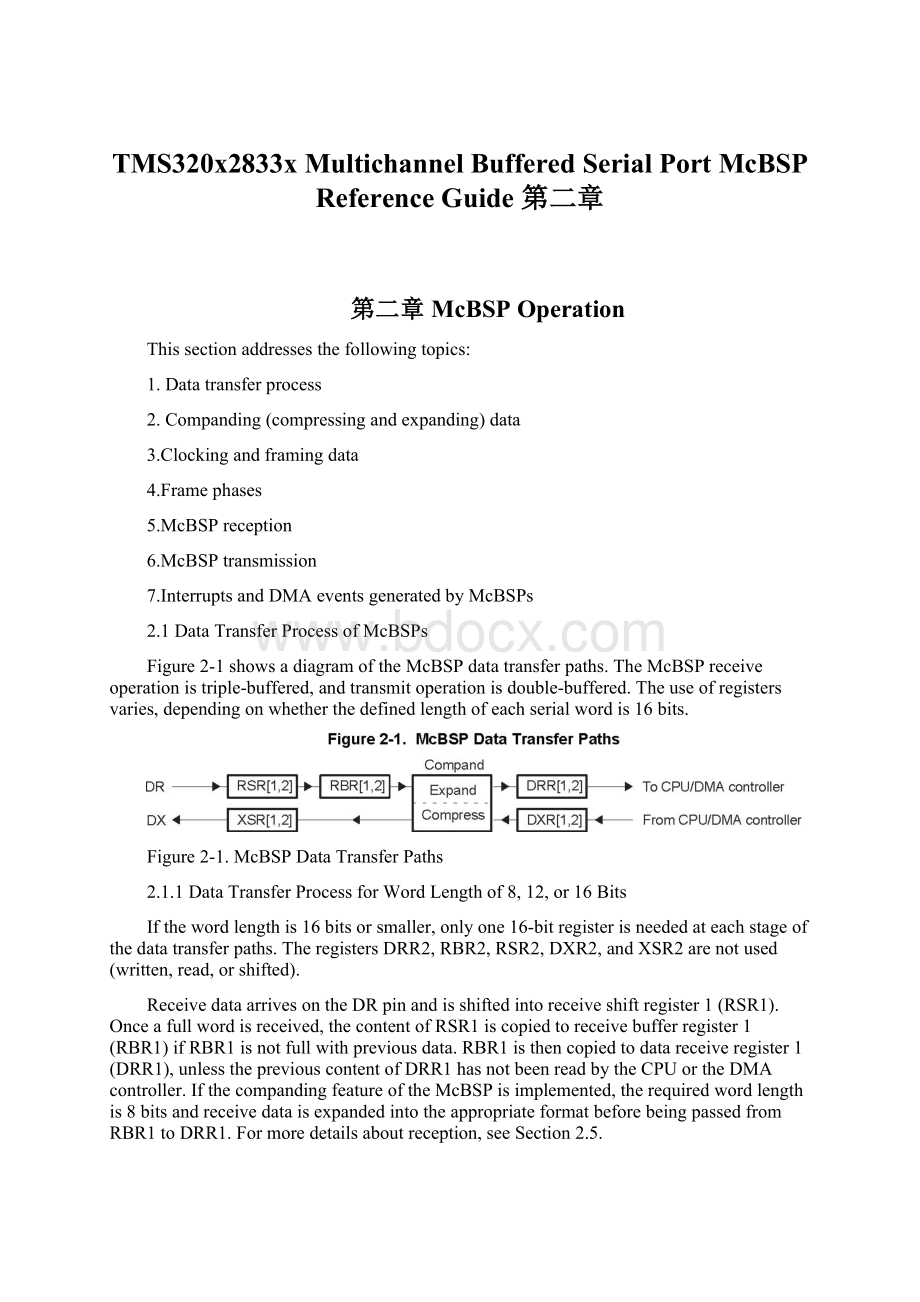

Figure2-1showsadiagramoftheMcBSPdatatransferpaths.TheMcBSPreceiveoperationistriple-buffered,andtransmitoperationisdouble-buffered.Theuseofregistersvaries,dependingonwhetherthedefinedlengthofeachserialwordis16bits.

Figure2-1.McBSPDataTransferPaths

2.1.1DataTransferProcessforWordLengthof8,12,or16Bits

Ifthewordlengthis16bitsorsmaller,onlyone16-bitregisterisneededateachstageofthedatatransferpaths.TheregistersDRR2,RBR2,RSR2,DXR2,andXSR2arenotused(written,read,orshifted).

ReceivedataarrivesontheDRpinandisshiftedintoreceiveshiftregister1(RSR1).Onceafullwordisreceived,thecontentofRSR1iscopiedtoreceivebufferregister1(RBR1)ifRBR1isnotfullwithpreviousdata.RBR1isthencopiedtodatareceiveregister1(DRR1),unlessthepreviouscontentofDRR1hasnotbeenreadbytheCPUortheDMAcontroller.IfthecompandingfeatureoftheMcBSPisimplemented,therequiredwordlengthis8bitsandreceivedataisexpandedintotheappropriateformatbeforebeingpassedfromRBR1toDRR1.Formoredetailsaboutreception,seeSection2.5.

TransmitdataiswrittenbytheCPUortheDMAcontrollertodatatransmitregister1(DXR1).Ifthereisnopreviousdataintransmitshiftregister(XSR1),thevalueinDXR1iscopiedtoXSR1;otherwise,DXR1iscopiedtoXSR1whenthelastbitofthepreviousdataisshiftedoutontheDXpin.Ifselected,thecompandingmodulecompresses16-bitdataintotheappropriate8-bitformatbeforepassingittoXSR1.Aftertransmitframesynchronization,thetransmitterbeginsshiftingbitsfromXSR1totheDXpin.Formoredetailsabouttransmission,seeSection2.6.

2.1.2DataTransferProcessforWordLengthof20,24,or32Bits

Ifthewordlengthislargerthan16bits,two16-bitregistersareneededateachstageofthedatatransferpaths.TheregistersDRR2,RBR2,RSR2,DXR2,andXSR2areneededtoholdthemostsignificantbits.

ReceivedataarrivesontheDRpinandisshiftedfirstintoRSR2andthenintoRSR1.Oncethefullwordisreceived,thecontentsofRSR2andRSR1arecopiedtoRBR2andRBR1,respectively,ifRBR1isnotfull.ThenthecontentsofRBR2andRBR1arecopiedtoDRR2andDRR1,respectively,unlessthepreviouscontentofDRR1hasnotbeenreadbytheCPUortheDMAcontroller.TheCPUortheDMAcontrollermustreaddatafromDRR2firstandthenfromDRR1.WhenDRR1isread,thenextRBR-to-DRRcopyoccurs.Formoredetailsaboutreception,seeSection2.5.

Fortransmission,theCPUortheDMAcontrollermustwritedatatoDXR2firstandthentoDXR1.WhennewdataarrivesinDXR1,ifthereisnopreviousdatainXSR1,thecontentsofDXR2andDXR1arecopiedtoXSR2andXSR1,respectively;otherwise,thecontentsoftheDXRsarecopiedtotheXSRswhenthelastbitofthepreviousdataisshiftedoutontheDXpin.Aftertransmitframesynchronization,thetransmitterbeginsshiftingbitsfromtheXSRstotheDXpin.Formoredetailsabouttransmission,seeSection2.6.

2.2Companding(CompressingandExpanding)Data

Companding(COMpressingandexPANDing)hardwareallowscompressionandexpansionofdataineitherµ-laworA-lawformat.ThecompandingstandardemployedintheUnitedStatesandJapanisµ-law.TheEuropeancompandingstandardisreferredtoasA-law.Thespecificationsforµ-lawandA-lawlogPCMarepartoftheCCITTG.711recommendation.

A-lawandµ-lawallow13bitsand14bitsofdynamicrange,respectively.Anyvaluesoutsidethisrangearesettothemostpositiveormostnegativevalue.Thus,forcompandingtoworkbest,thedatatransferredtoandfromtheMcBSPviatheCPUorDMAcontrollermustbeatleast16bitswide.

Theµ-lawandA-lawformatsbothencodedatainto8-bitcodewords.Compandeddataisalways8bitswide;theappropriatewordlengthbits(RWDLEN1,RWDLEN2,XWDLEN1,XWDLEN2)mustthereforebesetto0,indicatingan8-bitwideserialdatastream.Ifcompandingisenabledandeitheroftheframephasesdoesnothavean8-bitwordlength,compandingcontinuesasifthewordlengthis8bits.

Figure2-2illustratesthecompandingprocesses.Whencompandingischosenforthetransmitter,compressionoccursduringtheprocessofcopyingdatafromDXR1toXSR1.Thetransmitdataisencodedaccordingtothespecifiedcompandinglaw(A-laworµ-law).Whencompandingischosenforthereceiver,expansionoccursduringtheprocessofcopyingdatafromRBR1toDRR1.Thereceivedataisdecodedtotwos-complementformat.

Figure2-2.CompandingProcesses

2.2.1CompandingFormats

Forreception,the8-bitcompresseddatainRBR1isexpandedtoleft-justified16-bitdatainDRR1.Thereceivesign-extensionandjustificationmodespecifiedinRJUSTisignoredwhencompandingisused.

Fortransmissionusingµ-lawcompression,the14databitsmustbeleft-justifiedinDXR1andthattheremainingtwolow-orderbitsarefilledwith0sasshowninFigure2-3.

Figure2-3.µ-LawTransmitDataCompandingFormat

FortransmissionusingA-lawcompression,the13databitsmustbeleft-justifiedinDXR1,withtheremainingthreelow-orderbitsfilledwith0sasshowninFigure2-4.

Figure2-4.A-LawTransmitDataCompandingFormat

2.2.2CapabilitytoCompandInternalData

IftheMcBSPisotherwiseunused(theserialporttransmitandreceivesectionsarereset),thecompandinghardwarecancompandinternaldata.Thiscanbeusedto:

Convertlineartotheappropriateµ-laworA-lawformat

Convertµ-laworA-lawtothelinearformat

Observethequantizationeffectsincompandingbytransmittinglineardataandcompressingandre-expandingthisdata.ThisisusefulonlyifbothXCOMPANDandRCOMPANDenablethesamecompandingformat.

Figure2-5showstwomethodsbywhichtheMcBSPcancompandinternaldata.Datapathsforthesetwomethodsareusedtoindicate:

Whenboththetransmitandreceivesectionsoftheserialportarereset,DRR1andDXR1areconnectedinternallythroughthecompandinglogic.ValuesfromDXR1arecompressed,asselectedbyXCOMPAND,andthenexpanded,asselectedbyRCOMPAND.RRDYandXRDYbitsarenotset.However,dataisavailableinDRR1withinfourCPUclocksafterbeingwrittentoDXR1.

Theadvantageofthismethodisitsspeed.ThedisadvantageisthatthereisnosynchronizationavailabletotheCPUandDMAtocontroltheflow.DRR1andDXR1areinternallyconnectedifthe(X/R)COMPANDbitsaresetto10bor11b(compandusingµ-laworA-law).

TheMcBSPisenabledindigitalloopbackmodewithcompandingappropriatelyenabledbyRCOMPANDandXCOMPAND.Receiveandtransmitinterrupts(RINTwhenRINTM=0andXINTwhenXINTM=0)orsynchronizationevents(REVTandXEVT)allowsynchronizationoftheCPUorDMAtotheseconversions,respectively.Here,thetimeforthiscompandingdependsontheserialbitrateselected.

Figure2-5.TwoMethodsbyWhichtheMcBSPCanCompandInternalData

2.2.3ReversingBitOrder:

OptiontoTransferLSBFirst

Generally,theMcBSPtransmitsorreceivesalldatawiththemostsignificantbit(MSB)first.However,certain8-bitdataprotocols(thatdonotusecompandeddata)requiretheleastsignificantbit(LSB)tobetransferredfirst.IfyousetXCOMPAND=01binXCR2,thebitorderingof8-bitwordsisreversed(LSBfirst)beforebeingsentfromtheserialport.IfyousetRCOMPAND=01binRCR2,thebitorderingof8-bitwordsisreversedduringreception.Similartocompanding,thisfeatureisenabledonlyiftheappropriatewordlengthbitsaresetto0,indicatingthat8-bitwordsaretobetransferredserially.Ifeitherphaseoftheframedoesnothavean8-bitwordlength,theMcBSPassumesthewordlengthiseightbits,andLSB-firstorderingisdone.

2.3ClockingandFramingData

ThissectionexplainsbasicconceptsandterminologyimportantforunderstandinghowMcBSPdatatransfersaretimedanddelimited.

2.3.1Clocking

DataisshiftedonebitatatimefromtheDRpintotheRSR(s)orfromtheXSR(s)totheDXpin.Thetimeforeachbittransferiscontrolledbytherisingorfallingedgeofaclocksignal.

Thereceiveclocksignal(CLKR)controlsbittransfersfromtheDRpintotheRSR(s).Thetransmitclocksignal(CLKX)controlsbittransfersfromtheXSR(s)totheDXpin.CLKRorCLKXcanbederivedfromapinattheboundaryoftheMcBSPorderivedfrominsidetheMcBSP.ThepolaritiesofCLKRandCLKXareprogrammable.

IntheexampleinFigure2-6,theclocksignalcontrolsthetimingofeachbittransferonthepin.

Figure2-6.Example-ClockSignalControlofBitTransferTiming

Note:

TheMcBSPcannotoperateatafrequencyfasterthan½theLSPCLKfrequency.WhendrivingCLKXorCLKRatthepin,chooseanappropriateinputclockfrequency.WhenusingtheinternalsamplerategeneratorforCLKXand/orCLKR,chooseanappropriateinputclockfrequencyanddividedownvalue(CLKDV)(i.e.,becertainthatCLKXorCLKR≤LSPCLK/2).

2.3.2SerialWords

Bitstravelingbetweenashiftregister(RSRorXSR)andadatapin(DRorDX)aretransferredinagroupcalledaserialword.Youcandefinehowmanybitsareinaword.

BitscominginontheDRpinareheldinRSRuntilRSRholdsafullserialword.OnlythenisthewordpassedtoRBR(andultimatelytotheDRR).

Duringtransmission,XSRdoesnotacceptnewdatafromDXRuntilafullserialword