数字电子钟逻辑测试教材.docx

《数字电子钟逻辑测试教材.docx》由会员分享,可在线阅读,更多相关《数字电子钟逻辑测试教材.docx(10页珍藏版)》请在冰豆网上搜索。

数字电子钟逻辑测试教材

课程设计名称:

电子技术课程设计

题目:

数字电子钟逻辑电路设计

学期:

2013-2014学年第2学期

专业:

班级:

姓名:

学号:

指导教师:

辽宁工程技术大学

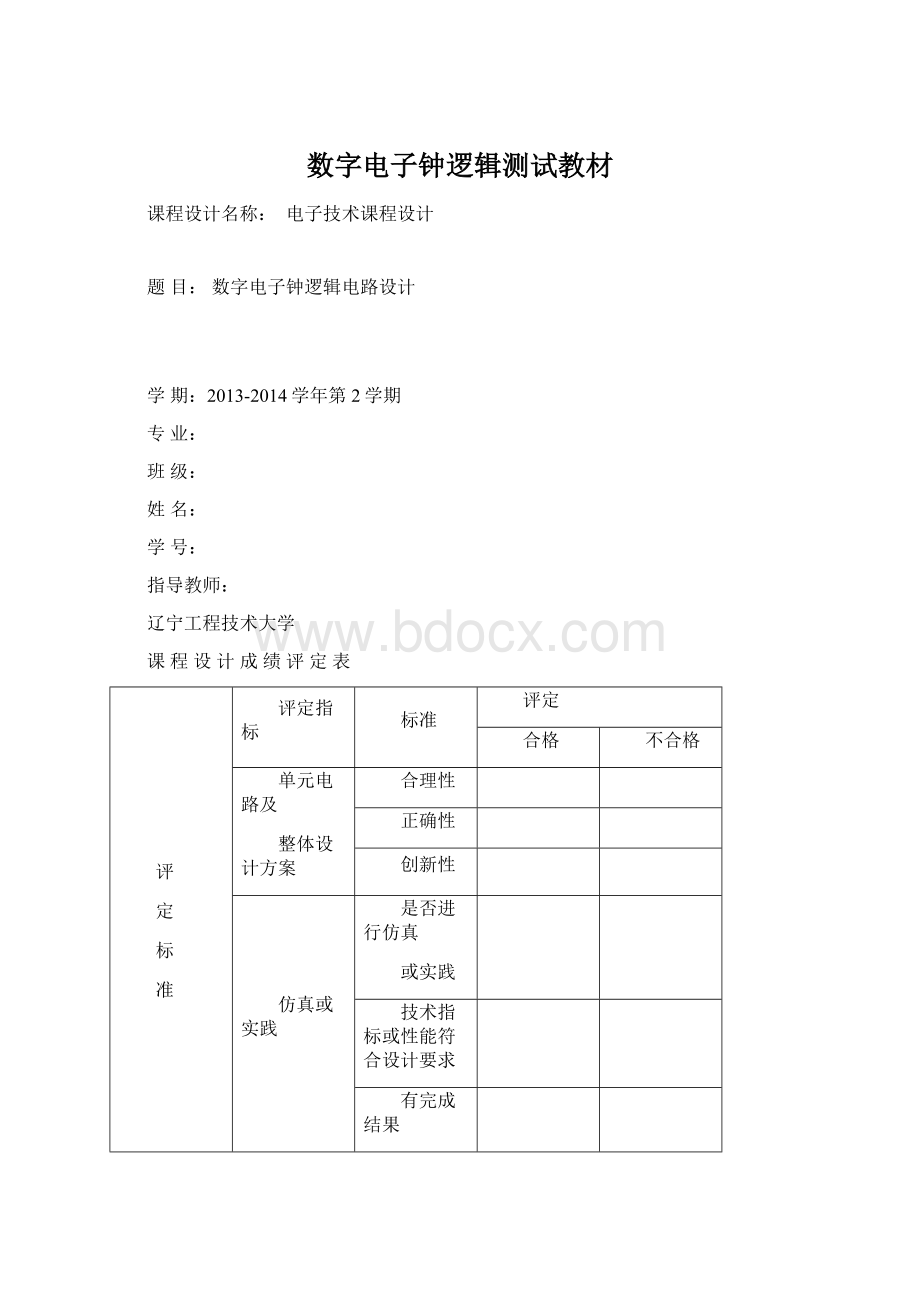

课程设计成绩评定表

评

定

标

准

评定指标

标准

评定

合格

不合格

单元电路及

整体设计方案

合理性

正确性

创新性

仿真或实践

是否进行仿真

或实践

技术指标或性能符合设计要求

有完成结果

设计报告

格式正确

内容充实

语言流畅

标准说明:

以上三大项指标中,每大项中有两小项或三小项合格,视为总成绩合格。

总成绩

日期

年月日

课程设计任务书

一、设计题目

数字电子钟逻辑电路设计

二、设计任务

用中、小规模集成电路设计一台能显示日、时、分、秒的数字电子钟,要求如下:

1.由晶振电路产生1Hz标准秒信号。

2.秒、分为00~59六十进制计数器。

3.时为00~23二十四进制计数器。

4.周显示从1~日为七进制计数器。

5.可手动校时:

能分别进行秒、分、时、日的校时。

6.有整点报时功能。

三、设计计划

电子技术课程设计共1周。

第1天:

查找相关资料;

第2天:

确定总体方案;

第3天:

器件选择;

第4天:

设计硬件电路;

第5天:

整理报告。

四、设计要求

1.确定原理方框图。

2.画出整个系统电路原理图。

3.对所设计的电路进行分析。

4.心得体会。

指导教师:

曹媛

时间:

2014年6月24日

摘要

数字钟计时的标准信号应该是频率相当稳定的1HZ秒脉冲,所以要设置标准时间源。

数字钟计时周期是24小时,因此必须设置24小时计数器,应由模为60的秒计数器和分计数器及模为24的时计数器组成,秒、分、时由七段数码管显示。

为使数字钟走时与标准时间一致,校时电路是必不可少的。

设计中采用开关控制校时直接用秒脉冲先后对“时”,“分”计数器进行校时操作。

能进行整点报时,在从59分50秒开始,每隔2秒钟发出一次“嘟”的信号,连续五次,此信号结束即达到正点。

数字电子钟在我们日常生活中是必不可缺少的,他为我们日常的生活生产提供了极大的方便。

它的作用是十分巨大的,因此我们一定要保证它的准确性。

它的准确才能保证我们生产生活有条不紊的进行,才能让我们过上更加美好的生活。

并且具有整点报时的功能,更加人性化。

电子钟主要用到CD4060,计数器,JK触发器CD4027,74LS90计数器等

关键字振荡器;分频器;译码器;计数器;校时电路;报时电路;

综述..........................................................1

1数字电子钟的构成............................................2

2数字电子钟系统设计...........................................3

2.1CD4060外接晶振的振荡电路..................................3

2.2时间计数器电路............................................3

2.3译码器驱动电路.............................................3

2.4数码管.....................................................3

3数字电子钟电路设计...........................................4

3.1用CD4060外接晶振的振荡电路................................4

3.2时间计数器电路.............................................4

3.3译码显示电路...............................................6

3.4校时电路..................................................6

3.5整点报时电路...............................................7

心得体会......................................................8

结论..........................................................9

参考文献......................................................10

综述

现代电子技术的飞跃发展,各类智能化产品相应而出,数字电路具有电路简单、可靠性高、成本低等优点,本设计就以数字电路为核心设计智能电子钟。

数字钟是采用数字电路实现对时,分,秒数字显示的计时装置,广泛用于个人家庭,车站,码头办公室等公共场所,成为人们日常生活中不可少的必需品,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度,运运超过老式钟表,钟表的数字化给人们生产生活带来了因此,研究数字钟及扩大其应用,有着非常现实的意义。

本设计电路由计时电路、动态显示电路、控制电路、显示电路等部分组成,在数码管上显示24小时计时的时刻,具有清零、保持、校时、报时的功能,并在此基础上增加了星期显示的功能。

现如今,人们对于时间的精确度的要求越来越高,在军事,医学,教育等等各个领域时间的准确都起着至关重要的作用,本实验所设计的数字电子钟是以数字电子技术为基础,因此能够有效地提高时间的准确性,并且具有整点报时功能,因此说本实验所设计的数字电子钟是一项非常实用的电路。

本实验先通过外接CD4060计数器的晶振电路完成标准秒信号的发生。

再接入六十进制,二十四进制和七进制计数器完成适中的技术功能。

同时接有校时电路和整点报时电路完成其相应的功能。

1数字电子钟的构成

数字电子钟由基准频率源、分频器、计数器、译码显示驱动器、数字显示器和校准电路等六部分组成。

如图1.1所示。

图1.1数字钟的组成框图

2数字电子钟系统设计

2.1CD4060外接晶振的振荡电路

由晶体振荡器产生2HZ的标准信号,再接入CD4060计数器进行二分频即可得到1HZ的标准秒信号。

2.2时间计数器电路

时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器、时个位和时十位计数器及星期计数器电路构成,其中秒个位和秒十位计数器、分个位和分十位计数器为60进制计数器,时个位和时十位计数器为24进制计数器,星期计数器为7进制计数器。

2.3译码器驱动电路

译码驱动电路将计数器输出的8421BCD码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

2.4数码管

数码管通常有发光二极管(LED)数码管和液晶(LCD)数码管,本设计提供的为LED数码管。

3数字电子钟电路设计

3.1用CD4060外接晶振的振荡电路

本电路主要由14位二进制串行计数器CD4060和JK触发器CD4027组成。

14位二进制计数器CD4060内部含有一个由非门电路组成的振荡器,在CD4060的10、11脚之间接上一个32.768kHz的晶体,就可以构成一个振荡器,其输出脉冲经过施密特整形电路整形后送入内部进行计数、分频,经214=16384分频,在输出端可得到2Hz(

)的标准信号。

再经一级CD4027组成的2分频电路分频,即可得到秒脉冲信号。

图2.1用晶振产生恒定脉冲电路

3.2时间计数器电路

时间计数单元有时计数、分计数、秒计数和星期计数等几个部分。

时计数单元一般为24进制计数器,其输出为两位8421BCD码形式;分计数和秒计数单元为60进制计数器,其输出也为8421BCD码;星期计数单元为7进制计数器,其输出也为8421BCD码形式。

(1)60进制计数:

“秒”计数器电路与“分”计数器电路都是60进制,它由一级10进制计数器和一级6进制计数器连接构成,如图2.4所示,采用两片中规模集成电路74LS90串接起来构成的“秒”、“分”计数器。

IC1是十进制计数器,QD1作为十进制的进位信号,74LS90计数器是十进制异步计数器,用反馈归零方法实现十进制计数,IC2和与非门组成六进制计数。

74LS90是在CP信号的下降沿翻转计数,QA2和QC2相与0101的下降沿,作为“分”(“时”)计数器的输入信号。

QB2和QC20110高电平1分别送到计数器的清零R0

(1),R0

(2),74LS90内部的R0

(1)和R0

(2)与非后清零而使计数器归零,完成六进制数。

由此可见IC1和IC2串联实现了六十进制计数。

至

分

(时)

计

数

器

的

CP

端

图2.2六十进制计数器

(2)24进制计数器:

小时计数电路是由IC5和IC6组成的24进制计数电路,如图2.5所示。

当“时”个位IC5计数输入端CP5来到第10个触发信号时,IC5计数器复零,进位端QD5向IC6“时”十位计数器输出进位信号,当第24个“时”(来自“分”计数器输出的进位信号)脉冲到达时,IC5计数器的状态为“0100”,IC6计数器的状态为“0010”,此时“时”个位计数器的QC5和“时”十位计数器的QB6输出为“1”。

把它们分别送到IC5和IC6计数器的清零端R0

(1)和R0

(2),通过7490内部的R0

(1)和R0

(2)与非后清零,计数器复零,完成24进制计数。

QC5

图2.324进制计数器

(3)7进制计数器:

星期计数电路是由IC7构成的7进制计数电路。

图2.47进制计数器

3.3译码显示电路

选择CD4511作为显示译码电路;选择LED数码管作为显示单元电路。

由CD4511把输进来的二进制信号翻译成十进制数字,再由数码管显示出来。

计数器实现了对时间的累计并以8421BCD码的形式输送到CD4511芯片,再由4511芯片把BCD码转变为十进制数码送到数码管中显示出来。

如图2.5所示。

图2.5二十四进制和六十进制译码显示电路

3.4校时电路

数字钟应具有分校正和时校正功能,因此,应截断分个位和时个位的直接计数通路,并采用正常计时信号与校正信号可以随时切换的电路接入其中。

开关打向下时,校正信号和0相与的输出为0,而开关的另一端接高电平,校时信号可以顺利通过接通,电路处于校时状态;开关打向上时,情况正好相反,电路处于正常工作状态。

如图2.6所示。

图2.6校时电路

3.5整点报时电路

电路应在整点前10秒钟内开始整点报时,即当时间在59分50秒到59分59秒期间内,蜂鸣器响一秒停一秒的响五次,报时电路控制报时信号。

当时间在59分50秒到59分59秒期间时,分十位、分个位和秒十位均保持不变,分别为5、9和5,因此可将分计数器十位的QC和QA、个位的QD和QA,秒计数器十位的QC和QA和秒个位的反相相与,从而产生报时控制信号。

如图2.7所示。

图2.7整点报时电路

心得体会

结论

综上所述,数字电子钟电路共分为脉冲产生电路,计数器电路和控制电路三大部分。

脉冲产生电路和控制电路负责数字电子钟的计数和显示等主要功能,控制电路负责实现整点报时和校准的功能。

用到的芯片主要有NE555,74LS90,CD4060和与非门及或门电路等。

本实验先通过外接CD4060计数器的晶振电路完成标准秒信号的发生。

再接入六十进制,二十四进制和七进制计数器完成适中的技术功能。

同时接有校时电路和整点报时电路完成其相应的功能。

数字电子钟对于我们的生活生产有着非常重要的作用,本实验所设计的电路能够提供准确的时间并且具有整点报时功能,这对人们的生活生产会提供更大的便利,因此说本实验所设计的电路的作用是十分巨大的。

在设计的过程中虽然遇到了很多困难,但是通过询问老师与同学,去图书馆查阅资料,直到把这些问题一一解决,加深了我对数字电子中各个芯片的理解,知道了各个芯片的功能,并且能够正确且有效的运用他们,最终完成了这一设计。

参考文献

1.阎石.数字电子技术基础.[M].第五版.高等教育出版社.2006

2.康华光.电子技术基础模拟部分(第五版).高等教育出版社,2006年

3.康华光.电子技术基础数字部分(第五版).高等教育出版社,2006年

4.李振声.实验电子技术.国防工业出版社,2001年

5.童诗白华成英.模拟电子技术基础(第四版),高等教育出版社,2006年

6.汤山俊夫.数字电路设计,科学出版社,2006年

7.关静.数字电路应用设计,科学出版社,2009年