8位 SAR ADC设计说明书.docx

《8位 SAR ADC设计说明书.docx》由会员分享,可在线阅读,更多相关《8位 SAR ADC设计说明书.docx(27页珍藏版)》请在冰豆网上搜索。

8位SARADC设计说明书

图目录

表目录

8位SARADC

1关键名词解释

12位ADC的文档中已述

2功能概述

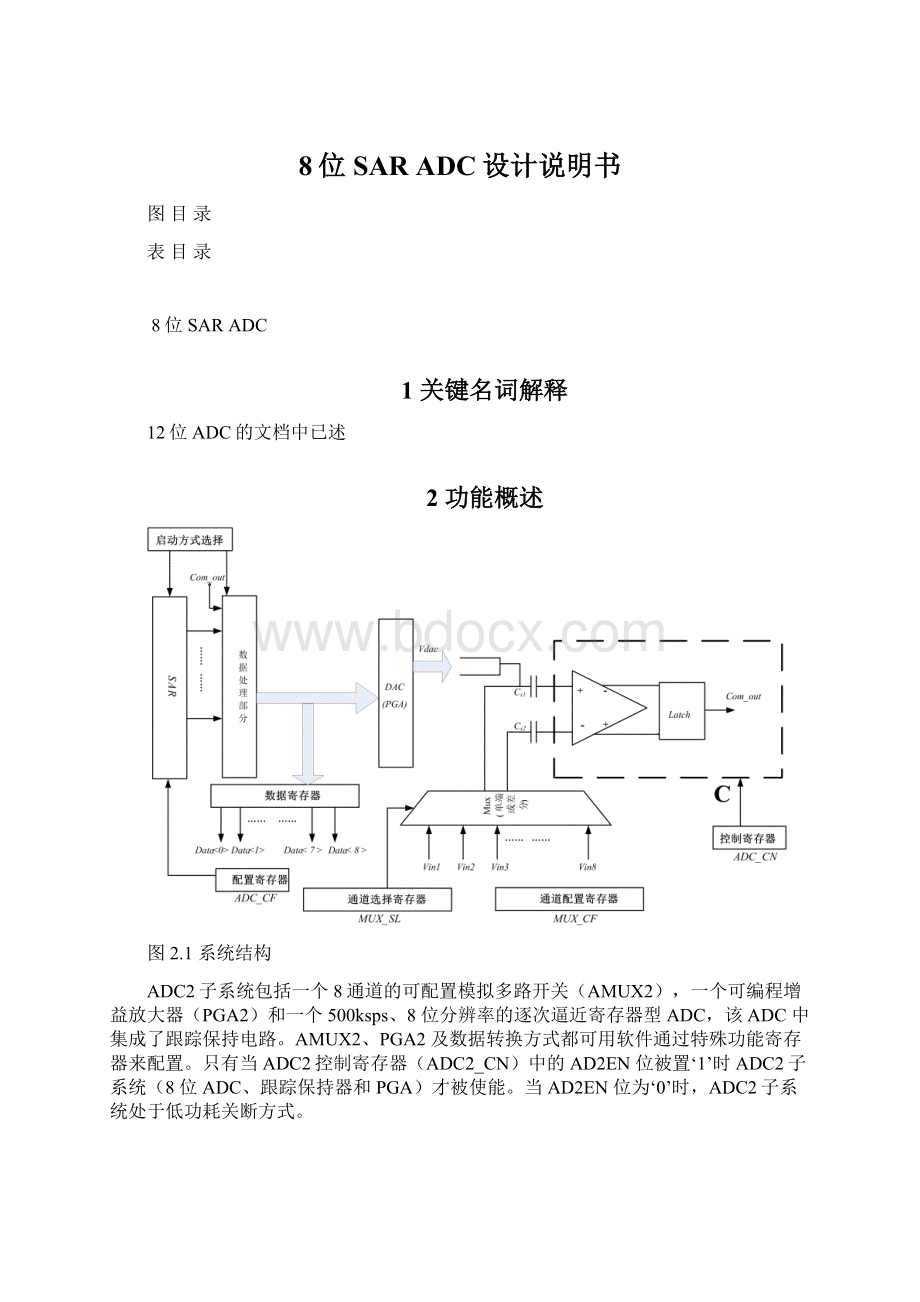

图2.1系统结构

ADC2子系统包括一个8通道的可配置模拟多路开关(AMUX2),一个可编程增益放大器(PGA2)和一个500ksps、8位分辨率的逐次逼近寄存器型ADC,该ADC中集成了跟踪保持电路。

AMUX2、PGA2及数据转换方式都可用软件通过特殊功能寄存器来配置。

只有当ADC2控制寄存器(ADC2_CN)中的AD2EN位被置‘1’时ADC2子系统(8位ADC、跟踪保持器和PGA)才被使能。

当AD2EN位为‘0’时,ADC2子系统处于低功耗关断方式。

ADC2有8个通道用于测量,用寄存器MUX_2SL选择通道。

PGA对AMUX输出信号的放大倍数由ADC2配置寄存器ADC2_CF中的AMP2GN2-0确定。

PGA增益可以用软件编程为0.5、1、2、4,复位时的默认增益为0.5。

接口信号说明

●输入信号列表

序号

信号名

来源

含义

备注

1

P_IN1

启动方式选择信号(为0,选择P_IN2;为1,选择P_IN3)

2

P_IN2

四种内部触发启动方式之一

3

P_IN3

外部上升沿启动

4

P_IN4

ADCCN6,即低功耗方式选择位(为0,连续跟踪;为1,低功耗方式)

5

P_IN5

差分方式标志位,(为1,差分;为0,单端)

6

P_IN6

复位信号(为1,复位整个数字部分)

7

P_IN7

使能信号(与P_IN6同等地位,为0时,复位整个数字部分)

8

P_IN8

G2控制放大2倍

9

P_IN9

G4控制放大4倍

10

P_IN10

与通道控制相关的信号

11

P_IN11

P_IN10的反信号

12

P_IN12

ADC的系统时钟和分频时钟的选择信号(为1,选P_IN13;为0,选系统时钟)

13

P_IN13

系统分频之后的时钟

14

P_IN14

G1控制放大1倍

15

P_IN15

G0.5控制放大0.5倍

16

P_IN16

com_out比较器的输出

17

P_IN17

内部连接信号,与比较器相关

18

P_IN19

在本模块中没有用到

19

CP1

系统时钟

●输出信号列表

序号

信号名

去向

含义

备注

1

P_OUT1

与开始启动转换标志有关

2

P_OUT2

与开始启动转换标志有关

3

P_OUT3

ADC数据寄存器第0位

4

P_OUT4

ADC数据寄存器第1位

5

P_OUT5

ADC数据寄存器第2位

6

P_OUT6

ADC数据寄存器第3位

7

P_OUT7

ADC数据寄存器第4位

8

P_OUT8

ADC数据寄存器第5位

9

P_OUT9

ADC数据寄存器第6位

10

P_OUT10

ADC数据寄存器第7位

3工作原理及电路性能分析

3.1数字部分

控制逻辑比较简单,主要总结控制逻辑的主要特点

1)要注意移位寄存器的第一位逻辑。

开始比较时,SAR的第一位被置为1,随后又被置为0,移位寄存器在工作时只有一位为1,要求在移位寄存器第一个触发器输出Q端和输入D端有反馈逻辑。

2)当移位寄存器移位到使比较完成时,它的下一位会发出完成信号,告知数据寄存器,使所有以前完成比较的位一起输出。

同时,在一次转换结束后,也会告知采样信号,可以进行下一次采样。

3)双端差分输入和单端输入决定译码的最高位,通道配置寄存器提供通道配置信号,与ADC的最高位形成判决逻辑。

4)移位寄存器,数据存储寄存器的复位信号也很重要,它与ADC的启动有关。

3.2模拟部分

3.2.1关于采样精度和采样时间

SAR时钟频率为6MHz,因此比较器的延时应在170ns以内,基准电压2.4v,比较器的分辨率为1/2LSB=4.6875mv。

为此,每一级比较器的输出端都加了限摆幅的反馈电路。

采样的建立时间要求由下式给出:

SA是建立精度,用一个LSB的分数表示(例如,建立精度0.25对应1/4LSB)。

t为所需要的建立时间,以秒为单位。

RTOTAL为ADC2模拟开关电阻与外部信号源电阻之和。

n为ADC的分辨率,用比特表示,对8位ADC,n=8。

3.2.2比较器

图3.1采样期间的第一级比较器的结构图

Vin2端接共模电平,折叠点的nMOS电流源由Vin2端对应的输出P_OUT25偏置。

采样结束时反馈s1开关稍微先于采样开关s2和s3断开,中间开关s4在s2和s3断开之后立即导通。

图3.28位ADC的比较器的结构图

图3.2是8位ADC中比较期间用到的三级比较器,后接一个锁存器和RS触发器。

注意第一级是全差分结构,第二级和第三级不是,因为它们的nMOS输入管的源极接地,没有共用一个电流源。

实际电路中各支路的偏置电流分别设为(I为1个电流单位)M4管8I;M12管7.5I;M7管4I;M8管4I。

例如:

第一级的输出端p_out25和p_out24,分别接了MF1、MF2、MF3、MF4。

这四个管子的工作过程如下:

1)当Vin1与Vin2之差在运放发生转换的电压范围

之内时,会造成M1管和M2管流过的电流失衡。

设输入电压使流过M1管的电流为3.5I,M2管的电流为4.5I,为符合基尔霍夫电流定律,流过MF2的电流为I,MF1没有电流,对应的P_OUT24降到MF1管的阈值电压以下。

第一级的输出电压由MF1管和MF2管的Vgs设定。

这时,MF3和MF4的Vgs都小于Vth,都关断。

2)当Vin1与Vin2之差大于转换电压时,M1和M2一个饱和,一个截止。

例如,Vin2远小于Vin1,M1截止,8I的电流全部流过M2管,此时流过MF2管的电流最大为4.5I,P_OUT25-P_OUT24的差值足以大于MF4管的Vgs,则MF4管有电流流过,使P_OUT24的电压稍微升高,减小P_OUT25-P_OUT24的差值。

升高的幅度取决于MF3和MF4的宽长比。

模拟结果也说明了这一点。

附:

a)当vin相差较大时,有钳位二极管的情况:

P_OUT24=0.872v,P_OUT25=0.0748v

b)当vin相差较大时,没有钳位二极管的情况:

X24=0.95v,x25=0.048v

c)当vin相差较小时,有钳位二极管的情况:

P_OUT24=0.687v,P_OUT25=0.707v

d)当vin相差较小时,没有钳位二极管的情况:

X24=0.687v,x25=0.707v

图3.3ss情况下比较器的仿真结果分析

如图3.3所示,net041和net078为比较器的两个输入端,相差0.462v,第一级比较器的输出端P_OUT24和P_OUT25相差很大,DAC电压是在2.01u时才加进去的,这样比较器的延时为2.061u-2.01u=51ns。

图3.4ss情况下比较器的仿真结果分析

在比较器两端相差7.2mv时,延时明显增加,第一级的两个输出端电压相差56mv左右,反馈的MF1、MF2都打开,MF3、MF4关闭,流过的电流之差就是输入管流过的电流之差。

3.2.3可变增益结构

如图3.5所示,比较器的一个输入端为vp,其输出端为vp_out;另一个为vn,其输出端为vn_out。

采样时,开关S1闭合,vp_out连接到它的输入端vp;S2闭合,vn_out连接到底下的折叠pmos的栅极,作为偏置电压,为比较器提供电流源,而vn则接上vcm,这样形成单位负反馈,输入端vp的电压跟随vcm,失调电压存储在采样电容Cs1上。

图3.5带采样保持电路的第一级

采样结束后,S1先断开,S2随后断开,接着clk变为低电平,即Vs1和Vs2的传输门断开。

此时,控制Mn和Mp的信号将会打开Mn和Mp,DAC电压接入,这时将会发生电荷转移,此时的等效电路如下。

例如:

(a)(b)

图3.6(a)Mn和Mp未开;(b)Mn和Mp导通,DAC电压接入时的情况

(a)(b)

图3.7(a)比较器Vp端的输入(b)比较器Vn端的输入

在实际的电路中,为了方便推导理解,将Vs2和Vn之间接的电容等效为电容C,Vs1与Vp之间和Data<0>~Data<7>与Vp之间接的电容也可以等效为电容C,如图3.7示Vp和Vn各有四个相同的此种输入结构的电容,根据控制信号的不同,它们有不同的输入状态。

设Cs1=nC,Cs2=nC,即Vs1和Vs2都只接入两块电容时,Mn和Mp导通后,由于有接地电容,存在电荷重分配,电容上的电荷转移情况假设如下:

图3.8电荷转移图

易解得

电容Cd上的电压变化量为

则

接上DAC电压后,设接入的DAC电容为Cd’,的有

此时比较器的另一端固定为Vcm.

可见,增益取决于

与

之比,通过逻辑控制,会得到n=2或4,

等于4C,2C,C三种情况,则可以组合出增益为4、2、1、0.5四种情况。

例如,当增益为1时,比较器的一端的电压为Vcm,另一端的电压由下式给出:

3.2.3模拟部分仿真结果

增益Gain=1时比较器一端的电压由下式给出:

表3.1Gain=1时的仿真结果

工艺角

ss

tt

ff

理论值(采样后,v)

0.8526

0.8526

0.8526

理论值(Vdac后,v)

1.1562

1.1562

1.1562

仿真值(v)

1.1641

1.1656

1.1664

误差(mv)

8.9

9.6

10.2

tdelay

75n

70n

68n

com_out

1

1

1

Idiss

条件:

(Cs=2.56p,采样时间700ns)

Gain=0.5时比较器的一端电压由下式给出:

表3.2Gain=0.5时的仿真结果

工艺角

ss

tt

ff

理论值(采样后,v)

0.2563

0.2563

0.2563

理论值(Vdac后,v)

1.1543

1.1543

1.1543

仿真值(v)

1.1482

1.1446

1.1654

误差(mv)

6.1

9.7

11.1

com_out

0

0

0

Idiss

条件:

(Cs=2.56p,采样时间700ns)

Gain=2比较器的一端电压由下式给出:

表3.3Gain=2时的仿真结果

工艺角

ss

tt

ff

理论值(采样后,v)

0.4682

0.4682

0.4682

理论值(Vdac后,v)

1.1623

1.1623

1.1623

仿真值(v)

1.1529

1.1563

1.1602

误差(mv)

9.4

6.0

2.1

tdelay

127n

95n

72n

com_out

0

1

1

Idiss

条件:

(Cs=2.56p,采样时间700ns)

Gain=4比较器的一端电压由下式给出:

表3.4Gain=4时的仿真结果

工艺角

ss

tt

ff

理论值(采样后,v)

0.6548

0.6548

0.6548

理论值(Vdac后,v)

1.1824

1.1824

1.1824

仿真值(v)

1.1795

1.1896

1.1802

误差(mv)

2.9

7.2

2.2

tdelay

32n

32n

32n

com_out

1

1

1

Idiss

条件:

(Cs=2.56p,采样时间700ns)

此时,比较器的一端电压为Vcm=1.151v,另一端电压对应不同的Gain有相应的值。

仿真过程中发现,误差来自如下:

1)加入DAC电压后,误差主要来自有效的8位二进制数所占的权重。

权重越大,所带入的误差越大,这是因为,权重大的位系数要大一些。

2)缩放电容不是严格按照(16/15)U倍单位电容的比例来仿真的,而直接用的是单位电容,这主要是考虑到版图的限制。

因为所有的电容都是按照单位电容和匹配的原则绘制出来的,若专为两个理论上应该是(16/15)U的电容而修改版图,将会影响匹配和布局,从理论上讲,U和(16/15)U的电容的误差是(1/15)U,这也不是太大,多以就没有修改。

3)技术文档中给出的采样电容是5p,限于工艺库文件,按照原照片的面积和原工艺,仿真时用到的采样电容是2.56p左右,实际新工艺版图提出来的电容是3.33pf左右。

4验证结果分析

4.1TT25℃的仿真结果

图4.1TT25℃,差分输入负电压情况下

图4.2TT25℃,差分输入正电压情况下

图4.3TT25℃,单端输入情况下

将以上曲线的结果汇于表4.1中:

表4.1TT25仿真结果参数

参数

积分非线性

±1LSB

微分非线性

±1LSB

偏移误差

0LSB

满度误差

负向,(1LSB);正向,(0LSB)

测量条件:

AVDD=3v,AVREF=2.4v,PGA=1,TT,25

4.2SS85℃的仿真结果

图4.4SS2.7v85℃,双端输入负电压

图4.5SS2.7v85℃,双端输入正电压

图4.6SS2.7v85℃,单端输入正电压

将以上曲线的结果汇于下表中,如表4.2所示:

表4.2SS85℃仿真结果参数

参数

积分非线性

±1LSB

微分非线性

±1LSB

偏移误差

-1LSB

满度误差

负向,(1LSB);正向,(0LSB)

测量条件:

AVDD=2.7v,AVREF=2.4v,PGA=1,SS,85

4.3SS125℃的仿真结果

图4.7SS2.7v125℃,双端输入负电压

图4.8SS2.7v125℃,双端输入正电压

图4.9SS2.7v125℃,单端输入

将以上曲线的结果汇于下表中,如表4.3所示:

表4.3SS125℃仿真结果参数

参数

积分非线性

±1LSB

微分非线性

±1LSB

偏移误差

-1LSB

满度误差

负向,(-1LSB);正向,(1LSB)

测量条件:

AVDD=2.7v,AVREF=2.4v,PGA=1,SS,125

4.4FF-55℃的仿真结果

图4.10FF3.6v-55℃,双端输入负电压

图4.11FF3.6v-55℃,双端输入正电压

图4.12FF3.6v-55℃,单端输入正电压

将以上曲线的结果汇于下表中,如表4.4所示:

表4.4FF-55℃仿真结果参数

参数

积分非线性

±2LSB

微分非线性

±2LSB

偏移误差

1LSB

满度误差

负向,(-2LSB);正向,(0LSB)

测量条件:

AVDD=3.6v,AVREF=2.4v,PGA=1,FF,-55

4.5FF-40℃的仿真结果

图4.13FF3.6v-40℃,双端输入负电压

图4.14FF3.6v-40℃,双端输入正电压

图4.15FF3.6v-40℃,单端输入正电压

将以上曲线的结果汇于下表中,如表4.5所示:

表4.5FF-40℃仿真结果参数

参数

积分非线性

±1LSB

微分非线性

±1LSB

偏移误差

-1LSB

满度误差

负向,(1LSB);正向,(0LSB)

测量条件:

AVDD=3.6v,AVREF=2.4v,PGA=1,FF,-40

4.6总体电气特性表

表4.6原手册结果

表4.7仿真结果汇总

参数

备注

单位

静态参数

分辨率

8

位

积分非线性

±1

LSB

微分非线性

±1

LSB

偏移误差

-1~1(1252,-552)

LSB

满度误差

负向(-1~1);正向,(-1~1)

LSB

偏移温度系数

动态参数(10kHz正弦波输入,满度值的0到-1dB,100ksps)

信号噪声失真比

总谐波失真

到5次谐波

有效动态范围

转换速率

SAR时钟频率

6M

Hz

转换时间

8个SAR时钟

周期

跟踪时间

0.8

μS

转换速率

500

ksps

模拟输入

电压转换范围

0~2.4

V

*共模电压范围

输入电容

一端的采样电容

2.56(cdl)

3.33(spf)

pf

电源指标

-40℃3.6v

25℃3v

85℃2.7v

总体功耗

包括偏置电路

2.13

2.2

2.579

mw

电源抑制

测量条件:

AVDD=2.7or3vor3.6v,AVREF=2.4v,PGA=1,-40℃~85℃

4.7仿真环境说明