杭电计组实验10实现RIJ型指令的CPU设计实验精编版.docx

《杭电计组实验10实现RIJ型指令的CPU设计实验精编版.docx》由会员分享,可在线阅读,更多相关《杭电计组实验10实现RIJ型指令的CPU设计实验精编版.docx(15页珍藏版)》请在冰豆网上搜索。

杭电计组实验10实现RIJ型指令的CPU设计实验精编版

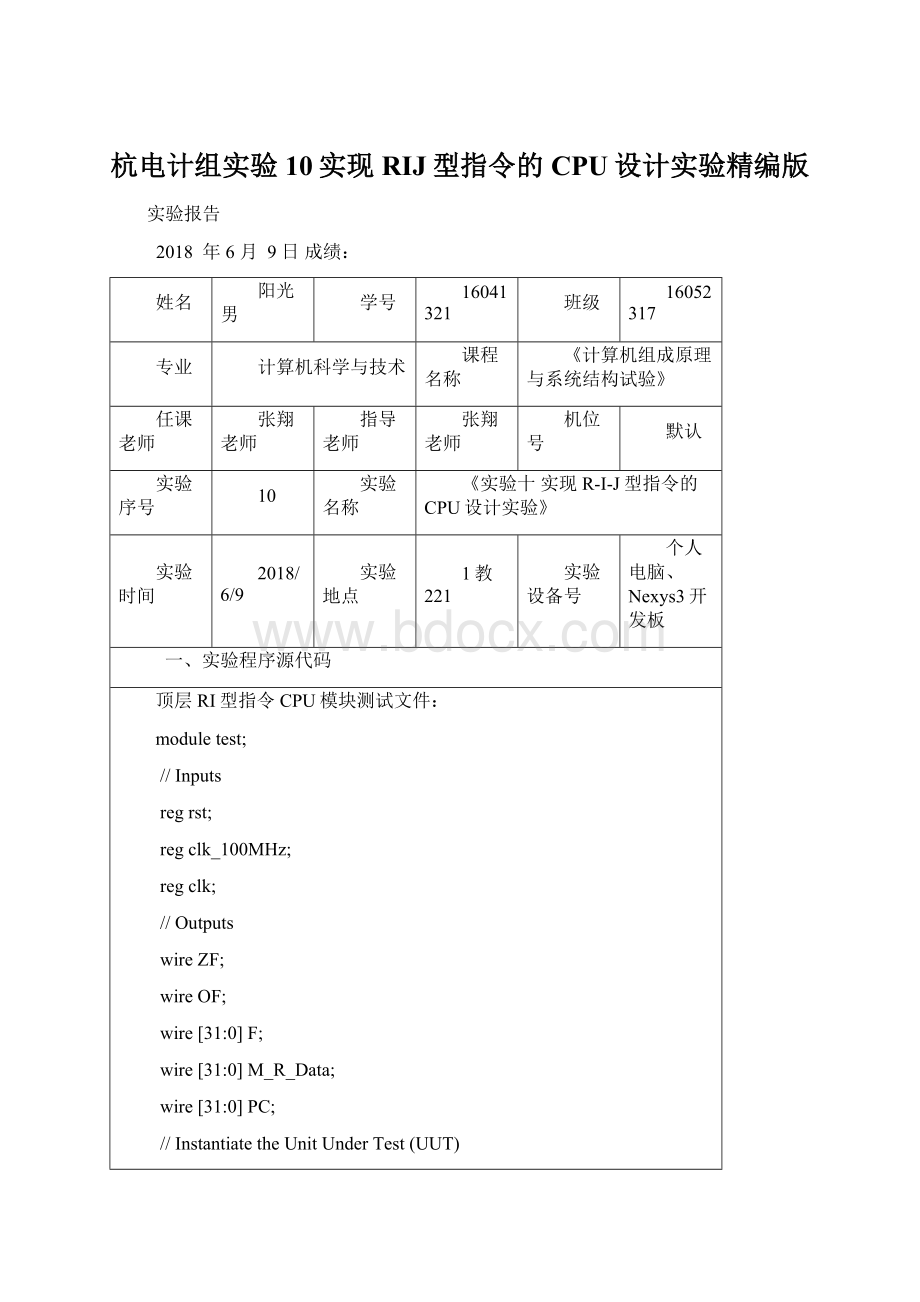

实验报告

2018年6月9日成绩:

姓名

阳光男

学号

16041321

班级

16052317

专业

计算机科学与技术

课程名称

《计算机组成原理与系统结构试验》

任课老师

张翔老师

指导老师

张翔老师

机位号

默认

实验序号

10

实验名称

《实验十实现R-I-J型指令的CPU设计实验》

实验时间

2018/6/9

实验地点

1教221

实验设备号

个人电脑、Nexys3开发板

一、实验程序源代码

顶层RI型指令CPU模块测试文件:

moduletest;

//Inputs

regrst;

regclk_100MHz;

regclk;

//Outputs

wireZF;

wireOF;

wire[31:

0]F;

wire[31:

0]M_R_Data;

wire[31:

0]PC;

//InstantiatetheUnitUnderTest(UUT)

TOP_RIJ_CPUuut(

.rst(rst),

.clk_100MHz(clk_100MHz),

.clk(clk),

.ZF(ZF),

.OF(OF),

.F(F),

.M_R_Data(M_R_Data),

.PC(PC)

);

initialbegin

//InitializeInputs

rst=0;

clk_100MHz=0;

clk=0;

//Wait100nsforglobalresettofinish

#100;

//Addstimulushere

forever

begin

#2;

clk=~clk;

#10;

clk_100MHz=~clk_100MHz;

end

end

endmodule

顶层LED验证模块

moduleTOP_LED(clk_100MHz,oclk,rst,SW,LED);

inputclk_100MHz;

inputoclk,rst;

input[3:

0]SW;

outputreg[7:

0]LED;

wirerclk;

wireZF,OF;

wire[31:

0]F;

wire[31:

0]M_R_Data;

wire[31:

0]PC;

xiaodoudoudong(clk_100MHz,oclk,rclk);

TOP_RIJ_CPU(rst,clk_100MHz,rclk,ZF,OF,F,M_R_Data,PC);

always@(*)

begin

case(SW)

4'b0000:

LED=F[7:

0];

4'b0001:

LED=F[15:

8];

4'b0010:

LED=F[23:

16];

4'b0011:

LED=F[31:

24];

4'b0100:

LED=M_R_Data[7:

0];

4'b0101:

LED=M_R_Data[15:

8];

4'b0110:

LED=M_R_Data[23:

16];

4'b0111:

LED=M_R_Data[31:

24];

4'b1000:

beginLED[7:

2]=0;LED[1]=OF;LED[0]=ZF;end

4'b1100:

LED=PC[7:

0];

4'b1101:

LED=PC[15:

8];

4'b1110:

LED=PC[23:

16];

4'b1111:

LED=PC[31:

24];

default:

LED=0;

endcase

end

endmodule

顶层RIJ型指令CPU验证模块:

moduleTOP_RIJ_CPU(inputrst,inputclk_100MHz,inputclk,outputZF,

outputOF,output[31:

0]F,output[31:

0]M_R_Data,output[31:

0]PC);

wireWrite_Reg;

wire[31:

0]Inst_code;

wire[4:

0]rs;

wire[4:

0]rt;

wire[4:

0]rd;

wire[31:

0]rs_data;

wire[31:

0]rt_data;

wire[31:

0]rd_data;

wire[31:

0]imm_data;//被扩展的立即数

wire[15:

0]imm;

//wirerd_rt_s;

wire[1:

0]w_r_s;

wireimm_s;//判断是否需要扩展

wirert_imm_s;//B端选择rt或者是扩展后的imm

wireMem_Write;

//wirealu_mem_s;

wire[1:

0]wr_data_s;

wire[31:

0]W_Addr;

wire[31:

0]W_Data;

wire[31:

0]R_Data_A;

wire[31:

0]R_Data_B;

wire[31:

0]F;

wire[31:

0]ALU_B;//B端口数据

wire[2:

0]ALU_OP;

wire[1:

0]PC_s;

wire[31:

0]PC_new;

wire[31:

0]PC;

wire[25:

0]address;

pcpc_connect(clk,rst,PC_s,R_Data_A,imm_data,address,Inst_code,PC);

OP_YIMAop(Inst_code,ALU_OP,rs,rt,rd,Write_Reg,imm,imm_s,

rt_imm_s,Mem_Write,address,w_r_s,wr_data_s,PC_s,ZF);

assignW_Addr=(w_r_s[1])?

5'b11111:

((w_r_s[0])?

rt:

rd);

assignimm_data=(imm_s)?

{{16{imm[15]}},imm}:

{{16{1'b0}},imm};

Register_fileR_connect(rs,rt,W_Addr,Write_Reg,W_Data,clk,rst,R_Data_A,R_Data_B);

assignALU_B=(rt_imm_s)?

imm_data:

R_Data_B;

ALUALU_connect(R_Data_A,ALU_B,F,ALU_OP,ZF,OF);

RAM_BData_Mem(

.clka(clk_100MHz),//inputclka

.wea(Mem_Write),//input[0:

0]wea

.addra(F[5:

0]),//input[5:

0]addra

.dina(R_Data_B),//input[31:

0]dina

.douta(M_R_Data)//output[31:

0]douta

);

assignW_Data=(wr_data_s[1])?

PC_new:

((wr_data_s[0])?

M_R_Data:

F);

endmodule

PC取指令模块:

modulepc(inputclk,inputrst,input[1:

0]PC_s,input[31:

0]R_Data_A,

input[31:

0]imm_data,input[25:

0]address,output[31:

0]Inst_code,output[31:

0]PC);

reg[31:

0]PC;

wire[31:

0]PC_new;

initial

PC<=32'h00000000;

Inst_ROMInst_ROM1(

.clka(clk),

.addra(PC[7:

2]),

.douta(Inst_code)

);

assignPC_new=PC+4;

always@(negedgeclkorposedgerst)

begin

if(rst)

PC<=32'h00000000;

else

begin

case(PC_s)

2'b00:

PC<=PC_new;

2'b01:

PC<=R_Data_A;

2'b10:

PC<=PC_new+(imm_data<<2);

2'b11:

PC<={PC_new[31:

28],address,2'b00};

endcase

end

end

endmodule

OP指令功能译码模块:

moduleOP_YIMA(inst,ALU_OP,rs,rt,rd,Write_Reg,

imm,imm_s,rt_imm_s,Mem_Write,address,w_r_s,wr_data_s,PC_s,ZF);

input[31:

0]inst;

outputreg[2:

0]ALU_OP;

outputreg[4:

0]rs;

outputreg[4:

0]rt;

outputreg[4:

0]rd;

outputregWrite_Reg;

outputreg[15:

0]imm;

//outputregrd_rt_s;

outputregimm_s;

outputregrt_imm_s;

outputregMem_Write;

outputreg[25:

0]address;

outputreg[1:

0]w_r_s;

outputreg[1:

0]wr_data_s;

outputreg[1:

0]PC_s;

inputZF;

always@(*)

begin

//----------处理R型指令----------

if(inst[31:

26]==6'b000000)

begin

rd=inst[15:

11];

rt=inst[20:

16];

rs=inst[25:

21];

//alu_mem_s=0;

wr_data_s=2'b00;

Mem_Write=0;

//rd_rt_s=0;

w_r_s=2'b00;

rt_imm_s=0;

case(inst[5:

0])

6'b100000:

beginALU_OP=3'b100;Write_Reg=1;PC_s=2'b00;end

6'b100010:

beginALU_OP=3'b101;Write_Reg=1;PC_s=2'b00;end

6'b100100:

beginALU_OP=3'b000;Write_Reg=1;PC_s=2'b00;end

6'b100101:

beginALU_OP=3'b001;Write_Reg=1;PC_s=2'b00;end

6'b100110:

beginALU_OP=3'b010;Write_Reg=1;PC_s=2'b00;end

6'b100111:

beginALU_OP=3'b011;Write_Reg=1;PC_s=2'b00;end

6'b101011:

beginALU_OP=3'b110;Write_Reg=1;PC_s=2'b00;end

6'b000100:

beginALU_OP=3'b111;Write_Reg=1;PC_s=2'b00;end

6'b001000:

beginALU_OP=3'b100;Write_Reg=0;PC_s=2'b01;end

endcase

end

//---------I型立即数寻址指令-------

if(inst[31:

29]==3'b001)

begin

imm=inst[15:

0];

rt=inst[20:

16];

rs=inst[25:

21];

Mem_Write=0;

//rd_rt_s=1;

rt_imm_s=1;

//alu_mem_s=0;

w_r_s=2'b01;

Write_Reg=1;

wr_data_s=2'b00;

case(inst[31:

26])

6'b001000:

beginimm_s=1;ALU_OP=3'b100;end

6'b001100:

beginimm_s=0;ALU_OP=3'b000;end

6'b001110:

beginimm_s=0;ALU_OP=3'b010;end

6'b001011:

beginimm_s=0;ALU_OP=3'b110;end

endcase

end

//--------处理I型取数/存数指令------

if((inst[31:

30]==2'b10)&&(inst[28:

26]==3'b011))

begin

imm=inst[15:

0];

rt=inst[20:

16];//rt寄存器

rs=inst[25:

21];//rs寄存器

//rd_rt_s=1;//rt作为目的存储器

rt_imm_s=1;//imm作为源操作数

imm_s=1;

w_r_s=2'b01;

wr_data_s=2'b01;

PC_s=2'b00;

case(inst[31:

26])

6'b100011:

beginMem_Write=0;Write_Reg=1;ALU_OP=3'b100;end

6'b101011:

beginMem_Write=1;Write_Reg=0;ALU_OP=3'b100;end

endcase

end

//-----------处理I型跳转指令---------

if(inst[31:

27]==5'b00010)

begin

imm=inst[15:

0];

rt=inst[20:

16];//rt

rs=inst[25:

21];//rs

case(inst[31:

26])

6'b000100:

beginrt_imm_s=0;ALU_OP=3'b101;Write_Reg=0;Mem_Write=0;

PC_s=(ZF?

2'b10:

2'b00);end

6'b000101:

beginrt_imm_s=0;ALU_OP=3'b101;Write_Reg=0;Mem_Write=0;

PC_s=(ZF?

2'b00:

2'b10);end

endcase

end

//----------处理J型跳转指令----------

if(inst[31:

27]==5'b00001)

begin

address=inst[25:

0];

case(inst[31:

26])

6'b000010:

beginw_r_s=2'b00;Write_Reg=0;Mem_Write=0;PC_s=2'b11;end

6'b000011:

beginw_r_s=2'b10;wr_data_s=2'b10;Write_Reg=1;Mem_Write=0;PC_s=2'b11;end

endcase

end

end

endmodule

寄存器堆模块:

moduleRegister_file(R_Addr_A,R_Addr_B,W_Addr,Write_Reg,W_Data,Clk,Reset,R_Data_A,R_Data_B);

input[4:

0]R_Addr_A;

input[4:

0]R_Addr_B;

input[4:

0]W_Addr;

inputWrite_Reg;

input[31:

0]W_Data;

inputClk;

inputReset;

output[31:

0]R_Data_A;

output[31:

0]R_Data_B;

reg[31:

0]REG_Files[0:

31];

reg[5:

0]i;

initial//仿真过程中的初始化

begin

for(i=0;i<=31;i=i+1)

REG_Files[i]=0;

end

assignR_Data_A=REG_Files[R_Addr_A];

assignR_Data_B=REG_Files[R_Addr_B];

always@(posedgeClkorposedgeReset)

begin

if(Reset)

for(i=0;i<=31;i=i+1)

REG_Files[i]<=0;

else

if(Write_Reg&&W_Addr!

=0)

REG_Files[W_Addr]<=W_Data;

end

endmodule

ALU运算模块:

moduleALU(A,B,F,ALU_OP,ZF,OF);

input[31:

0]A,B;

input[2:

0]ALU_OP;

outputregZF,OF;

outputreg[31:

0]F;

regC32;

always@(*)

begin

OF=1'b0;

C32=1'b0;

case(ALU_OP)

3'b000:

F=A&B;

3'b001:

F=A|B;

3'b010:

F=A^B;

3'b011:

F=~(A^B);

3'b100:

begin{C32,F}=A+B;OF=A[31]^B[31]^F[31]^C32;end

3'b101:

begin{C32,F}=A-B;OF=A[31]^B[31]^F[31]^C32;end

3'b110:

if(AF=1;

else

F=0;

3'b111:

F=B<endcase

if(F==0)

ZF=1;

else

ZF=0;

end

endmodule

二、仿真波形

三、电路图

顶层电路模块

顶层电路内部结构:

四、引脚配置(约束文件)

NET"LED[7]"LOC=T11;

NET"LED[6]"LOC=R11;

NET"LED[5]"LOC=N11;

NET"LED[4]"LOC=M11;

NET"LED[3]"LOC=V15;

NET"LED[2]"LOC=U15;

NET"LED[1]"LOC=V16;

NET"LED[0]"LOC=U16;

NET"SW[3]"LOC=M8;

NET"SW[1]"LOC=T9;

NET"SW[0]"LOC=T10;

NET"clk_100MHz"LOC=V10;

NET"oclk"LOC=C9;

NET"rst"LOC=C4;

NET"SW[2]"LOC=V9;

五、思考与探索

(1)R-I-J型指令CPU实验结果记录表

序号指令执行结果标志结论

100004020$8=0000_000000正确

200004820$9=0000_000000正确

3200a0014$10=0000_001400正确

48d2b0010$11=0000_001000正确

5010b4020$8=0000_222200正确

621290004$9=0000_000400正确

7214affff$10=000_001300正确

811400001判断:

$10不为000正确

908000003返回去执行地址为00正确

0000_0010的指令,

即序号4:

8d2b0010

……

……

10ac0b0030存储器地址:

0000_003000正确