组合逻辑电路作业key.docx

《组合逻辑电路作业key.docx》由会员分享,可在线阅读,更多相关《组合逻辑电路作业key.docx(12页珍藏版)》请在冰豆网上搜索。

组合逻辑电路作业key

数字电路基础——组合逻辑电路习题

班级:

学号:

姓名:

一、单项选择题(10小题)

(1)若在编码器中有50个编码对象,则要求输出二进制代码位数为( )位。

A、5 B、6 C、10 D、50

(2)在下列逻辑电路中,不是组合逻辑电路的有

A、译码器 B、编码器 C、全加器 D、寄存器

(3)用四选一数据选择器实现函数

,应使。

A、D0=D2=0,D1=D3=1 B、D0=D2=1,D1=D3=0

C、D0=D1=0,D2=D3=1 D、D0=D1=1,D2=D3=0

(4)当编码器74LS147的输入端I1、I5、I6、I7为低电平,其余输入端为高电平时,输出信号为。

A、1110 B、1010 C、1001 D、1000

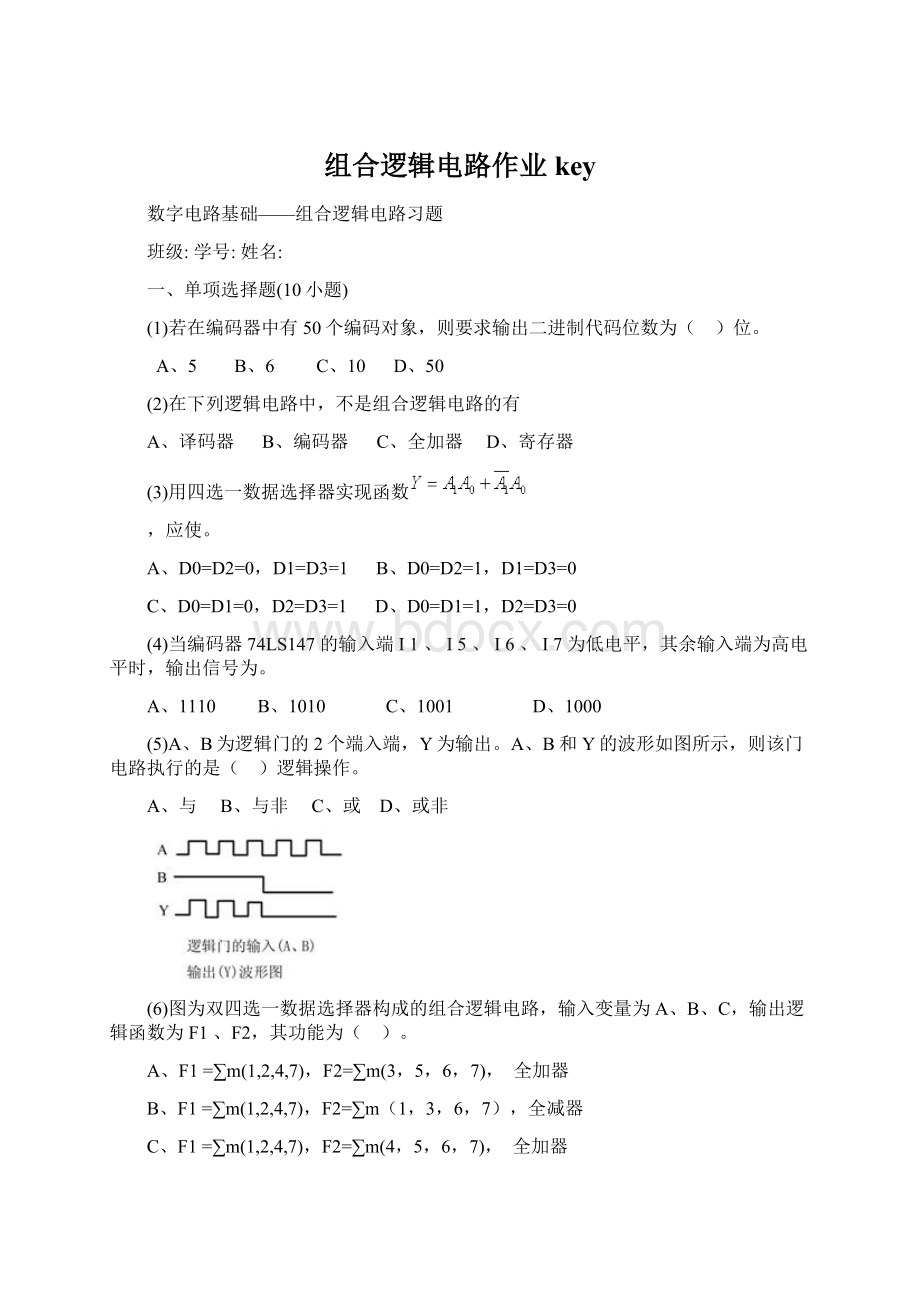

(5)A、B为逻辑门的2个端入端,Y为输出。

A、B和Y的波形如图所示,则该门电路执行的是( )逻辑操作。

A、与 B、与非 C、或 D、或非

(6)图为双四选一数据选择器构成的组合逻辑电路,输入变量为A、B、C,输出逻辑函数为F1、F2,其功能为( )。

A、F1=∑m(1,2,4,7),F2=∑m(3,5,6,7), 全加器

B、F1=∑m(1,2,4,7),F2=∑m(1,3,6,7),全减器

C、F1=∑m(1,2,4,7),F2=∑m(4,5,6,7), 全加器

D、F1=∑m(1,2,3,7),F2=∑m(3,5,6,7),全减器

(7)八路数据分配器,其位置输入端有( )个。

A、1 B、2 C、3 D、4

(8)用四选一数据选择器实现函数

应使。

A、

B、

C、

(9)图的4个逻辑图中不是“异或”逻辑关系的1项是( )。

(10)选出与图所示逻辑图对应的逻辑关系式。

A、Y=A+B+

B、Y=AB+

C、Y=(A+

)(

+B) D、Y=

B+A

=====答案=====

(1)B

(2)C(3)A(4)D(5)A(6)A(7)C(8)C(9)C(10)D

二、多项选择题(5小题)

(1)用三线-八线译码器74LS138实现原码输出的8路数据分配器,应。

A、

=1,

=D,

=0 B、

=1,

=D,

=D

C、

=1,

=0,

=D D、

=D,

=0,

=0

(2)一个8选1数据选择器的数据输入端有( )个,位置输入端有( )个。

A、1 B、2 C、3 D、4 E、8

(3)组合逻辑电路消除竞争冒险的方法有

A、修改逻辑设计 B、在输出端接入滤波电容

C、后级加缓冲电路 D、屏蔽输入信号的尖峰干扰

(4)以下电路中,加以适当辅助门电路,( )适于实现单输出组合逻辑电路。

A、二进制译码器 B、数据选择器 C、数值比较器 D、七段显示译码器

(5)函数

,当变量的取值为( )时,将出现冒险现象。

A、B=C=1 B、B=C=0 C、A=1,C=0 D、A=0,B=0

=====答案=====

(1)ABC

(2)EC(3)AB(4)AB(5)AD

三、判断题(9小题)

(1)二进制译码器相当于是一个最小项发生器,便于实现组合逻辑电路。

( )

(2)液晶显示器的优点是功耗极小、工作电压低。

( )

(3)液晶显示器可以在完全黑暗的工作环境中使用。

( )

(4)共阴接法发光二极管数码显示器需选用有效输出为高电平的七段显示译码器来驱动。

( )

(5)组合逻辑电路中产生竞争冒险的主要原因是输入信号受到尖峰干扰。

( )

(6)组合逻辑电路任意时刻的稳态输出,与输入信号作用前电路原来状态有关。

( )

(7)在二-十进制译码器中,伪码应做约束项处理( )。

(8)编码器在任何时刻只能对一个输入信号进行编码( )。

(9)数据选择器和数据分配器的功能正好相反,互为逆过程( )。

=====答案=====

(1)对

(2)对(3)错(4)对(5)错(6)错(7)对(8)对(9)对

四、填空题(3小题)

(1)半导体数码显示器的内部接法有两种形式:

共( )接法和共( )接法。

(2)对于共阳接法的发光二极管数码显示器,应采用( )电平驱动的七段显示译码器。

(3)消除竟争冒险的方法有( )、( )、( )等。

=====答案=====

(1)阴 阳

(2)低电平(3)修改逻辑设计 接入滤波电容 加选通脉冲

四、解答题(10小题)

(1)化简如图所示电路,并分析其功能。

(2)分析如图所示的逻辑电路,做出真值表,说明其逻辑功能

(3)画出用两片4线-16线译码器74LS154组成5线-32线译码的接线图。

图是74LS154的逻辑框图,图中

、

是两个控制端(亦称片选端)译码器工作时应使

、

同时为低电平,输入信号A3、A2、A1、A0为0000~1111这16种状态时,输出端从

依次给出低电平输出信号。

(4)用74LS138设计一位全减器电路,输入有被减数A、减数B、低位来的借位J0,输出有差D及向高位送出的借位数J1,列出真值表、写出函数式。

(5)用或非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其它状态时输出为0。

(6)试利用两片4位二进制并行加法器74LS283和必要的门电路组成1个二-十进制加法器电路。

(提示:

根据BCD码8421码的加法运算原则,当两数之和小于、等于9(1001)时,相加的结果和按二进制数相加所得到的结果一样。

当两数之和大于9(即等于1010~1111)时,则应在按二进制数相加所得到的结果上加6(0110),这样就可以给出进位信号,同时得到一个小于9的和。

)

(7)试用74LS138型3/8译码器设计一个位置译码器,位置译码器的位置范围为00-3F。

(可适当加其它逻辑门电路)。

(8)设计一个将8421BCD码变换成余3码的组合逻辑电路。

(9)试画出用3线-8线译码器74LS138(见下图)和门电路产生如下多输出逻辑函数的逻辑图。

(10)用8选1数据选择器CC4512产生逻辑函数

(11)图是一个函数发生器,试写出当S0S1S2S3为0000~1111的16种不同取值时,Y关于逻辑变量AB的逻辑函数式。

=====答案=====

(1)

(2)数值比较,

、

、

(3)电路如图所示。

当A4=0时,片

(1)工作,

对应输出低电平;当A4=1时,片

(2)工作,

对应输出低电平。

(4)解:

①列真值表:

A B J0

D

J1

0 0 0

0

0

0 0 1

1

1

0 1 0

1

1

0 1 1

0

1

1 0 0

1

0

1 0 1

0

0

1 1 0

0

0

1 1 1

1

1

②写函数式:

③画出逻辑图:

(5)

A B C D

Y

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

0

0

0

0

0

0

0

1

0

0

0

1

0

1

1

1

(6)由表可见,若将两个8421的二-十进制数A3A2A1A0和B3B2B1B0用二进制加法器相加,则当相加结果

9(1001)时,得到的和S3S2S1S0就是所求的二-十进制的和。

而当相加结果

10(1010)以后,必须将这个结果在另一个二进制加法器加6(0110)进行修正,才能得到二-十进制的和及相应的进为输出。

由表可知,产生进为输出

的条件为

,产生

的同时,应该在S3S2S1S0上加6(0110),得到的

和

就是修正后的结果。

故得到下图电路。

(7)解:

由于位置译码器的范围为00~3F(十六进制数),实际上是64个位置,因此,可用位置扩展的方法来实现,把3/8扩展成4/16,再扩展成6/64译码即可。

(8)设8421BCD码为A3A2A1A0,余3码为B3B2B1B0。

有:

B3=A3+A2A1+A2A0,

(9)

(10)将函数式化为

令

并令

,

即得下图。

(11)解:

根据变量可能的取值和组合,16种函数式为

[文档可能无法思考全面,请浏览后下载,另外祝您生活愉快,工作顺利,万事如意!

]