实验一用VHDL语言设计组合逻辑电路.docx

《实验一用VHDL语言设计组合逻辑电路.docx》由会员分享,可在线阅读,更多相关《实验一用VHDL语言设计组合逻辑电路.docx(11页珍藏版)》请在冰豆网上搜索。

实验一用VHDL语言设计组合逻辑电路

实验一用VHDL语言设计组合逻辑电路

一、实验目的:

掌握用VHDL语言设计组合逻辑电路的方法。

熟悉QuartusⅡ的操作。

二、实验仪器:

PC机一台

三、实验内容:

1.用VHDL语言设计4选1数据选择器。

2.用文本输入法输入

3.建立工程,编译,改错,直至编译通过

4.仿真,验证所设计电路的正确性

四、操作步骤:

1、在所使用的计算机数据盘里建立自己的文件夹

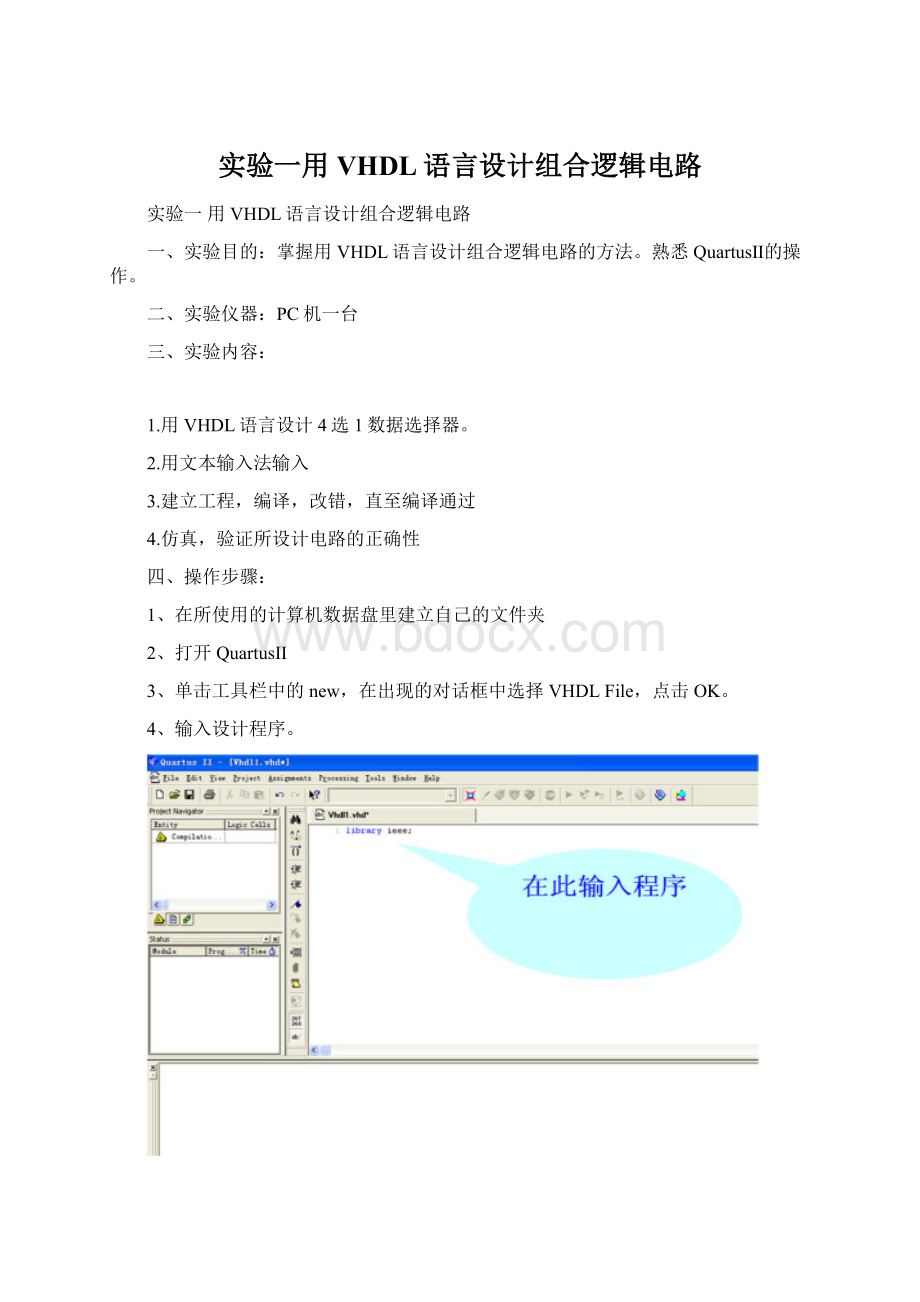

2、打开QuartusII

3、单击工具栏中的new,在出现的对话框中选择VHDLFile,点击OK。

4、输入设计程序。

输入结束后,将程序保存在自己的文件夹中。

注意:

存盘的文件名应该跟实体名相同。

5、

创建工程。

创建工程有两种方法:

第一种方法是在保存文件后出现的对话框中点击‘是’,按提示进行操作;

6、

7、

8、

9、

10、第二种方法是在出现的对话框点击‘否’。

11、

12、第一种方法的具体过程:

13、点击‘是’,出项下面的框

14、

15、点击‘Next’,出项

16、

17、不需要任何修改,继续点击‘Next’,出项

18、

19、继续点击‘Next’,在后面出现的框图中继续点击‘Next’,直到没有‘Next’选项,点击‘Finish’,这样就完成工程的创建。

第二种方法的具体过程:

点击‘否’

此时要创建工程,点击菜单File下的“NewPrejectWizard”。

出现框图:

点击‘Next’,出项

点击最上一行右边的

,寻找你的文件所在的文件夹,点击要创建工程的文件名,点击打开(或双击要创建工程的文件名),出现

项目名称和文件名称相同。

点击‘Next’,出现

点击

,在出现的对话框点击文件名,点击‘打开’,出现

点击右边的‘add’,出现

点击‘Next’,在后面出现的框图中继续点击‘Next’,直到没有‘Next’选项,点击‘Finish’,这样就完成工程的创建。

20、

观察QUARTUS界面

21、

22、

23、点击箭头所指图标,观察箭头上方的变化,点击+号,双击出项的文件

24、

25、

全程编译。

26、

27、点击箭头所指图标,开始全程编译。

如果有错误,编译会自动停止,出现

28、

29、点击确定,按提示到文件中修改错误,保存文件,继续点击全程编译的图标,如还有错误,继续上面的步骤。

如没有错误,会自动完成编译

30、

点击‘确定’。

31、时序仿真

从仿真结果说明电路的功能。

单击new,在出现的对话框中选择第二个标签“OtherFiles”,选择VectorWaveformFile,点击OK。

选择菜单View下“UtilityWindows”中的“NodeFinder”,出现“NodeFinder”对话框。

“NodeFinder”对话框中,上面中间的“Filter”右边下拉列表框中选择“Pins:

all”,点击“list”,将出现的端口信息按需要拖入波形窗口。

设置输入波形,保存波形文件。

如需要修改仿真时间,点击Edit菜单下EndTime。

保存波形文件。

时序仿真。

仔细读仿真报告,判断电路的正确性;如不正确,修改程序,重新编译,仿真,直至设计的电路完全正确。

时序仿真可参照教科书P100。

关闭工程,准备下一个实验内容。

点击菜单File下的closeproject,关闭当前工程。

如需要打开工程,点击菜单File下的openproject,选择文件夹,选择要打开的工程名,点击打开。

五、思考题:

用VHDL语言编写8位奇偶校验电路。

当8位中有奇数个1时输出为1。

六、实验报告要求:

写出正确的程序,并简要说明实验中遇到的问题及解决方法。

Libraryieee;

Usemux41ais

port(s:

instd_logic_vector(1downto0);

d0,d1,d2,d3:

instd_logic;

y:

outstd_logic);

Endmux41a;

Architectureabofmux41ais

Begin

y<=d0whens=“00”else

d1whens=“01”else

d2whens=“10”else

d3;

Endab;