EDA课程设计之十进制计数器流程.docx

《EDA课程设计之十进制计数器流程.docx》由会员分享,可在线阅读,更多相关《EDA课程设计之十进制计数器流程.docx(14页珍藏版)》请在冰豆网上搜索。

EDA课程设计之十进制计数器流程

2.1十进制计数器流程

2.11建立工作库文件夹和编辑设计文件

任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的所有设计文件的文件夹。

此文件夹将被EDA软件默认为工作库(WorkLibrary)。

一般,不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。

在建立了文件夹后就可以将设计文件通过Quartus II的文本编辑器编辑并存盘,步骤如下:

(1)新建一个文件夹。

这里假设本项设计的文件夹取名为CNT10B,在D盘中,路径为d:

\cnt10b。

注意,文件夹名不能用中文,也最好不要用数字。

(2)输入源程序。

打开QuartusII,选择菜单File→New。

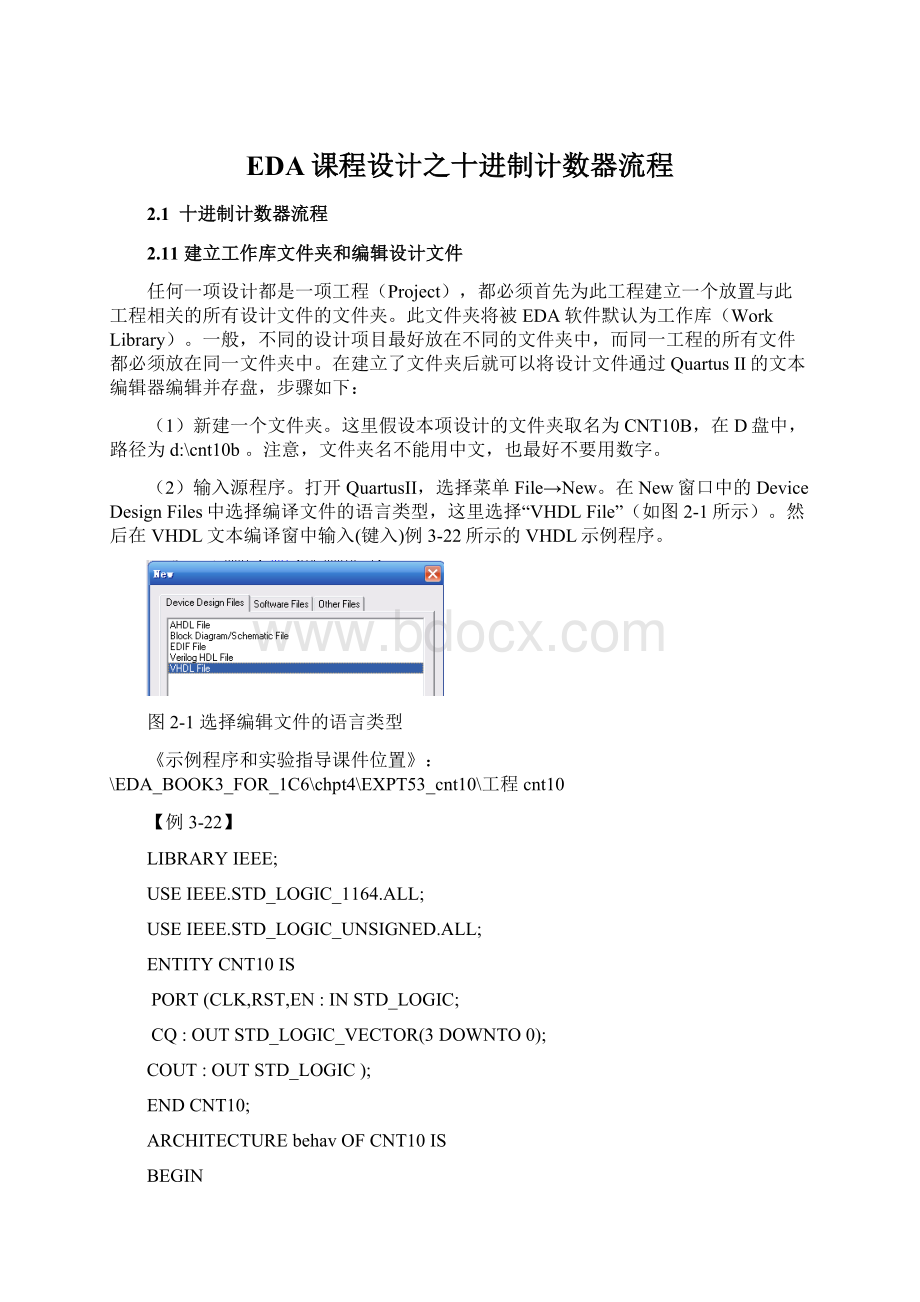

在New窗口中的DeviceDesignFiles中选择编译文件的语言类型,这里选择“VHDLFile”(如图2-1所示)。

然后在VHDL文本编译窗中输入(键入)例3-22所示的VHDL示例程序。

图2-1选择编辑文件的语言类型

《示例程序和实验指导课件位置》:

\EDA_BOOK3_FOR_1C6\chpt4\EXPT53_cnt10\工程cnt10

【例3-22】

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT10IS

PORT(CLK,RST,EN:

INSTD_LOGIC;

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC);

ENDCNT10;

ARCHITECTUREbehavOFCNT10IS

BEGIN

PROCESS(CLK,RST,EN)

VARIABLECQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFRST='1'THENCQI:

=(OTHERS=>'0');--计数器异步复位

ELSIFCLK'EVENTANDCLK='1'THEN--检测时钟上升沿

IFEN='1'THEN--检测是否允许计数(同步使能)

IFCQI<9THENCQI:

=CQI+1;--允许计数,检测是否小于9

ELSECQI:

=(OTHERS=>'0');--大于9,计数值清零

ENDIF;

ENDIF;

ENDIF;

IFCQI=9THENCOUT<='1';--计数大于9,输出进位信号

ELSECOUT<='0';

ENDIF;

CQ<=CQI;--将计数值向端口输出

ENDPROCESS;

(3)文件存盘。

选择File→SaveAs命令,找到已设立的文件夹d:

\cnt10b,存盘文件名应该与实体名一致,即cnt10.vhd。

当出现问句“Doyouwanttocreate…”时,若单击“是”按钮,则直接进入创建工程流程。

若单击“否”按钮,可按以下的方法进入创建工程流程。

2.1.2创建工程

使用NewProjectWizard可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称,还可以指定要在工程中使用的设计文件、其他源文件、用户库和EDA工具,以及目标器件系列和具体器件等。

(1)打开建立新工程管理窗。

选择菜单File→NewPrejectWizard命令,即弹出“工程设置”对话框(图2-2)。

图2-2利用“NewPrejectWizard”创建工程cnt10

单击此对话框最上一栏右侧的“…”按钮,找到文件夹d:

\cnt10b,选中已存盘的文件cnt10.vhd(一般应该设顶层设计文件为工程),再单击“打开”按钮,即出现如图2-2所示的设置情况。

其中第一行的d:

\cnt10b表示工程所在的工作库文件夹;第二行的cnt10表示此项工程的工程名,工程名可以取任何其他的名,也可直接用顶层文件的实体名作为工程名,在此就是按这种方式取的名;第三行是当前工程顶层文件的实体名,这里即为cnt10。

(2)将设计文件加入工程中。

单击下方的Next按钮,在弹出的对话框中单击File栏的按钮,将与工程相关的所有VHDL文件(如果有的话)加入进此工程,即得到如图2-3所示的情况。

此工程文件加入的方法有两种:

第1种是单击AddAll按钮,将设定的工程目录中的所有VHDL文件加入到工程文件栏中;第2种方法是单击“Add…”按钮,从工程目录中选出相关的VHDL文件。

(3)选择仿真器和综合器类型。

单击图2-3所示的Next按钮,这时弹出的窗口是选择仿真器和综合器类型,如果都选默认的“NONE”,表示都选Quartus II中自带的仿真器和综合器。

在此都选择默认项“NONE”(不作任何打勾选择)。

(4)选择目标芯片。

单击Next按钮,选择目标芯片。

首先在Family栏选芯片系列,在此选Cyclone系列,并在此栏下单击Yes按钮,即选择一确定目标器件。

再次单击Next按钮,选择此系列的具体芯片EP1C6T240C8。

这里EP1C6表示Cyclone系列及此器件的规模;T表示TQFP封装;C8表示速度级别。

便捷的方法是通过图2.4所示窗口右边的3个“Filters”窗口过滤选择:

分别选择Package为PQFP;Pin为240和Speed为8。

图2-3将所有相关的文件都加入进此工程图2-4选择目标器件EP1C6T240C8

2.1.3编译前设置

(1)选择FPGA目标芯片。

目标芯片的选择也可以这样来实现:

选择Assignmemts菜单中的settings项,在弹出的对话框中(图2-6)选择Category项下的Device。

首先选择目标芯片为EPIC6T240C8(此芯片已在建立工程时选定了)。

(2)选择配置器件的工作方式。

单击图2-6中的Device&PinOptions按钮,进入选择窗,这将弹出Device&PinOptions窗口,首先选择General项(图2-7),在Configuration选项页,选择配置器件为EPCS4,其配置模式可选择ActiveSerial。

这种方式只对专用的Flash技术的配置器件(专用于Cyclone系列FPGA的EPCS4和EPCS1等)进行编程。

注意,PC机对FPGA的直接配置方式都是JTAG方式,而对于FPGA进行所谓“掉电保护式”编程通常有两种:

主动串行模式(ASMode)和被动串行模式(PSMode)。

对EPCS1/EPCS4的编程必须用ASMode。

图2-8选择配置器件和编程方式

2.1.4全程编译

QuartusII编译器是由一系列处理模块构成的,这些模块负责对设计项目的检错,逻辑综合、结构综合、输出结果的编辑配置,以及时序分析。

在这一过程中,将设计项目适配到FPGA/CPLD目标器中,同时产生多种用途的输出文件,如功能和时序信息文件、器件编程的目标文件等。

编译器首先检查出工程设计文件中可能错误信息,供设计者排除。

然后产生一个结构化的以网表文件表达的电路原理图文件。

编译前首先选择Processing菜单的StartCompilation项,启动全程编译。

这里所谓的全程编译(Compilation)包括以上提到的QuartusII对设计输入的多项处理操作,其中包括排错、数据网表文件提取、逻辑综合、适配、装配文件(仿真文件与编程配置文件)生成,以及基于目标器件的工程时序分析等。

编译过程中要注意工程管理窗下方的“Processing”栏中的编译信息。

如果工程中的文件有错误,启动编译后在下方的Processing处理栏中会显示出来(如图2-9所示)。

对于Processing栏显示出的语句格式错误,可双击此条文,即弹出对应的vhdl文件,在深色标记条处即为文件中的错误,再次进行编译直至排除所有错误。

图2-9全程编译后出现报错信息

如果编译成功,可以见到如图2-9所示的工程管理窗的左上角显示了工程cnt10的层次结构和其中结构模块耗用的逻辑宏单元数(共5LCs);在此栏下是编译处理流程,包括数据网表建立、逻辑综合、适配、配置文件装配和时序分析等。

最下栏是编译处理信息;中栏(CompilationReport栏)是编译报告项目选择菜单,点击其中各项可以详细了解编译与分析结果。

2.1.5时序仿真

对工程编译通过后,必须对其功能和时序性质进行仿真测试,以了解设计结果是否满足原设计要求。

以VWF文件方式的仿真流程的详细步骤如下:

(1)打开波形编辑器。

选择菜单File中的New项,在New窗口中选择OtherFiles中的VectorWavefor

(2-10),单击OK按钮,即出现空白的波形编辑器(图2-11),注意将窗口扩大,以利观察。

(2)设置仿真时间区域。

对于时序仿真来说,将仿真时间轴设置在一个合理的时间区域上十分重要。

通常设置的时间范围在数十微秒间:

在Edit菜单中选择EndTime项,在弹出的窗口中的Time栏处输入50,单位选“μs”,整个仿真域的时间即设定为50μs(图2-12),单击OK按钮,结束设置。

(3)波形文件存盘。

选择File中的Saveas,将以默认名为singt.vwf的波形文件存入文件夹d:

\cnt10b中(图2-13)。

图2-10选择编辑矢量波形文件图2-11波形编辑器

图2-12设置仿真时间长度图2-13vwf激励波形文件存盘

(4)将工程cnt10的端口信号节点选入波形编辑器中。

方法是首先选择View菜单中的UtilityWindows项的NodeFinder选项。

弹出的对话框如图2-14所示,在Filter框中选Pins:

all(通常已默认选此项),然后单击List按钮,于是在下方的NodesFound窗口中出现设计中的cnt10工程的所有端口引脚名。

如果希望NodeFinder窗是浮动的,可以用右键点击此窗边框,在弹出的小窗(图2-14)上消去“EnableDocking”选项。

注意如果此对话框中的“List”不显示cnt10工程的端口引脚名,需要重新编译一次,即选择Processing→StartCompilation,然后再重复以上操作过程。

最后,用鼠标将重要的端口节点CLK、EN、RST、COUT和输出总线信号CQ分别拖到波形编辑窗,结束后关闭NodesFound窗口。

单击波形窗左侧的“全屏显示”按钮,使全屏显示,并单击“放大缩小”按钮后,再用鼠标在波形编辑区域右键单击,使仿真坐标处于适当位置,如图4-14上方所示,这时仿真时间横坐标设定在数十微秒数量级。

(5)编辑输入波形(输入激励信号)。

单击图2-14所示窗口的时钟信号名CLK,使之变成蓝色条,再单击左列的时钟设置键,在Clock窗中设置CLK的时钟周期为2μs;Clock窗口中的Dutycycle是占空比,默认为50,即50%占空比(图2-15)。

然后再分别设置EN和RST的电平。

最后设置好的激励信号波形图如图2-17所示。

(6)总线数据格式设置。

单击如图2-14所示的输出信号“CQ”左旁的“+”,则能展开此总线中的所有信号;如果双击此“+”号左旁的信号标记,将弹出对该信号数据格式设置的对话框(图2-16)。

在该对话框的Radix栏有4种选择,这里可选择无符号十进制整数UnsignedDecimal表达方式。

最后对波形文件再次存盘。

图2-14向波形编辑器拖入信号节点图2-15设置时钟CLK的周期

图2-16选择总线数据格式图2-17设置好的激励波形图

(7)启动仿真器。

现在所有设置进行完毕,在菜单Processing项下选择StartSimulation,

(8)观察仿真结果。

仿真波形文件“SimulationReport”通常会自动弹出(图2-19)。

由图2-20可看出,随着CLK脉冲的出现,DOUT输出的数值与工程中ROM内写入的波形数据完全一致。

图2-19仿真波形输出图2-20选择全时域显示

2.2引脚设置和下载

为了能对此计数器进行硬件测试,应将其输入输出信号锁定在芯片确定的引脚上,编译后下载。

(1)选择Tools菜单中的Assignments项,即进入如图2-23所示的AssignmentEditor编辑器窗。

在Category栏中选择Pin,或直接单击右上侧的Pin按钮。

(2)双击“TO”栏的《new》,在出现的如图2-24所示的下拉栏中分别选择本工程要锁定的端口信号名;然后双击对应的Location栏的《new》,在出现的下拉栏中选择对应端口信号名的器件引脚号,如对应CQ[3],选择42脚。

在此选择GW48-EDA系统的电路模式No.5(图2-22,参阅第一章图13),通过查阅附录有关”芯片引脚对照表”,GWAC3板确定引脚分别为:

主频时钟CLK接Clock0(第93脚,可接在4Hz上);计数使能EN可接电路模式No.5的键1(PIO0对应第1脚);复位RST则接电路模式No.5的键2(PIO1对应第2脚,注意键序与引脚号码并无对应关系);溢出COUT接发光管D1(PIO8对应第11脚);4位输出数据总线CQ[3..0]可由数码1来显示,通过分别接PIO19、PIO18、PIO17、PIO16(它们对应的引脚编号分别为42、41、40、39)。

(如是GWAC6板,CLK:

接28,EN:

233,RST:

234,COUT:

1,CQ[3..0]分别接16,17,18,19)

图2-22GW48实验系统模式5实验电路图图2-23AssignmentEditor编辑器

图2-24已将所有引脚锁定完毕

(4)最后存储这些引脚锁定的信息后,必须再编译(启动StartCompilation)一次,才能将引脚锁定信息编译进编程下载文件中。

2.2.1配置文件下载

将编译产生的SOF格式配置文件配置进FPGA中,进行硬件测试的步骤如下:

(1)打开编程窗和配置文件。

首先将实验系统和并口通信线连接好,打开电源。

在菜单Tool中选择Programmer,于是弹出如图2-25所示的编程窗。

在Mode栏中有4种编程模式可以选择:

JTAG、PassiveSerial、ActiveSerial和In-Socket。

为了直接对FPGA进行配置,在编程窗的编程模式Mode中选JTAG(默认),并选中打勾下载文件右侧的第一小方框。

注意要仔细核对下载文件路径与文件名。

如果此文件没有出现或有错,单击左侧“AddFile”按钮,手动选择配置文件cnt10.sof。

图2-25选择编程下载文件

(2)设置编程器。

若是初次安装的QuartusII,在编程前必须进行编程器选择操作。

这里准备选择ByteBlasterMV[LPT1]。

单击HardwareSetup按钮可设置下载接口方式(图2-25),在弹出的HardwareSetup对话框中(图2-26),选择Hardwaresettings页,再双击此页中的选项ByteBlasterMV之后,单击Close按钮,关闭对话框即可。

这时应该在编程窗右上显示出编程方式:

ByteBlasterMV[LPT1](图2-25)。

如果打开图2-26所示的窗口内“Currentlyselected”右侧显示NoHardware,则必须加入下载方式。

即点击AddHardware钮,在弹出的窗中点击OK,再在图4-27所示的窗口双击ByteBlasterMV,使“Currentlyselected”右侧显示ByteBlasterMV[LPT1]。

(3)选择编程器。

究竟显示哪一种编程方式(ByteBlasterMV或ByteBlasterII)取决于QuartusII对实验系统上的编程口的测试。

以GW48-EDA系统为例,若对此系统左侧的“JP5”跳线选择“Others”,则当进入QuartusII菜单Tool,打开Programmer窗后,将显示ByteBlasterMV[LPT1],如图2-25所示;而若对“JP5”跳线选择“ByBt II”,则当进入菜单Tool,打开Programmer窗后,将显示ByteBlaster II[LPT1],如图2-28所示。

注意对Cyclone的配置器件编程,必须使用此编程方式。

最后单击下载标符Start按钮,即进入对目标器件FPGA的配置下载操作。

当Progress显示出100%,,表示编程成功。

图2-26加入编程下载方式图2-27双击选中的编程方式名

图2-28ByteBlasterII编程下载窗

(4)硬件测试。

成功下载cnt10.sof后,选择实验电路模式5(参考第一章图13),将CLK的时钟通过实验箱上clock0的跳线选择频率为4Hz;键1置高电平,控制EN允许计数;键2先置高电平,后置低电平,使RST产生复位信号。

观察数码1和发光管D1了解计数器工作情况。

2.2.3编程配置器件

为了使FPGA在上电启动后仍然保持原有的配置文件,并能正常工作,必须将配置文件烧写进专用的配置芯片EPCSx中。

EPCSx是Cyclone系列器件的专用配置器件,Flash存储结构,编程周期10万次。

编程模式为ActiveSerial模式,编程接口为ByteBlaster II。

以下给出编程流程:

1.选择编程模式和编程目标文件

在如图4-25所示窗口的Mode栏,选择“ActiveSerialProgramming”编程模式,打开编程文件,选中文件cnt10.pof,并选中打勾3个编程操作项目,如图2-29所示。

2.选择接插模式

GW48主系统上的JP5跳线接“ByBt II”,即选择ByteBlasterII编程方式(JP6接3.3V);适配板上的4个跳线都接插“AS”端,最后将10芯线连接主系统的“ByteBlasterII”接插口和适配板上的10芯AS模式编程口。

3.AS模式编程下载

单击图2-29所示窗口的Start,编程成功后将出现如图2-30所示信息。

编程成功后FPGA将自动被EPCS器件配置而进入工作状态。

此后每次上电,FPGA都能被EPCS1自动配置,进入正常工作状态。

最后要将为AS模式编程而改变的短路帽跳线全部还原。

图2-29ByteBlaster II接口AS模式编程窗口

图2-30AS模式编程成功

2.3SignalTapII实时测试

随着逻辑设计复杂性的不断增加,仅依赖于软件方式的仿真测试来了解设计系统的硬件功能已远远不够了,而不断需要重复进行的硬件系统的测试也变得更为困难。

为了解决这些问题,设计者可以将一种高效的硬件测试手段和传统的系统测试方法相结合来完成。

这就是嵌入式逻辑分析仪的使用。

它可以随设计文件一并下载于目标芯片中,用以捕捉目标芯片内部信号节点处的信息,而又不影响原硬件系统的正常工作。

这就是QuartusII中SignalTapII的目的。

在实际监测中,SignalTapII将测得的样本信号暂存于目标器件中的嵌入式RAM(如ESB、M4K)中,然后通过器件的JTAG端口将采得的信息传出,送入计算机进行显示和分析。

嵌入式逻辑分析仪SignalTapII允许对设计中的所有层次的模块的信号节点进行测试,可以使用多时钟驱动,而且还能通过设置以确定前后触发捕捉信号信息的比例。

本节将以上面设计的计数器为例介绍SignalTapII的使用方法,流程如下:

1.打开SignalTap II编辑窗

选择菜单File中的New项,在New窗口中选择OtherFiles中的SignalTap IIFile(图2-10),单击OK按钮,即出现SignalTap II编辑窗(图2-31)。

图2-31SignalTap II编辑窗

2.调入待测信号

首先单击上排的Instance栏内的“auto_signaltap_0”,更改此名,如cnts,这是其中一组待测信号名。

为了调入待测信号名,在下栏(cnts栏)的空白处双击,即弹出NodeFinder窗口,单击List按钮,即在左栏出现此工程相关的所有信号,包括内部信号。

选择需要观察的信号名:

4位输出总线信号CQ、内部4锁存器总线CQI信号和COUT。

单击OK按钮后即可将这些信号调入SignalTap II信号观察窗(图2-31)。

注意不要将工程的主频时钟信号CLK调入信号观察窗,因为在本项设计中打算调用本工程的主频时钟信号CLK兼作逻辑分析仪的采样时钟。

此外如果有总线信号,只须调入总线信号名即可;慢速信号可不调入;调入信号的数量应根据实际需要来决定,不可随意调入过多的,没有实际意义的信号,这会导致SignalTapII无谓地占用芯片内过多的资源。

3.SignalTapII参数设置

单击全屏按钮和窗口左下角的Setup页,即出现如图2-32所示的全屏编辑窗。

首先输入逻辑分析仪的工作时钟信号Clock。

单击Clock栏左侧的“…”按钮,即出现NodeFinder窗,选中工程的主频时钟信号CLK作为逻辑分析仪的采样时钟;接着在Data框的Sample栏选择采样深度为1K位。

注意这个深度一旦确定,则cnts信号组的每一位信号都获得同样的采样深度,所以必须根据待测信号采样要求、信号组总的信号数量、以及本工程可能占用ESB/M4K的规模,综合确定采样深度,以免发生M4K不够用的情况。

然后是根据待观察信号的要求,在Bufferacquisitionmode框的Circulate栏设定采样深度中起始触发的位置,比如选择前点触发:

“Pretriggerposition”。

最后是触发信号和触发方式选择。

这可以根据具体需求来选定。

在Trigger框的Trigger栏选择1;选中打勾小Trigger框(图2-32右下角),并在Source栏选择触发信号。

在此选择cnts工程中的EN作为触发信号;在Pattern栏选择上升沿触发方式。

即当测得EN的上升沿后,SignalTapII在CLK的驱动下根据设置cnts信号组的信号进行连续或单次采样。

图2-32SignalTapII编辑窗

4.文件存盘

选择菜单File中的SaveAs项,输入此SignalTap II文件名为cnt10.stp1(默认名)。

单击“保存”按钮后,将出现一个提示(图2-32):

“DoyouwanttoenableSignalTapII…”,应该单击“是”按钮。

表示同意再次编译时将此SignalTapII文件(核)与工程(cnt10)捆绑在一起综合/适配,以便一同被下载进FPGA芯片中去完成实时测试任务。

5.编译下载

首先选择Processing菜单的StartCompilation项,启动全程编译。

编译结束后,SignalTap II的观察窗通常会自动打开,但若没有打开,可选择菜单Tools中的SignalTap IIAnalyzer,打开SignalTap II。

接着打开实验开发系统的电源,连接JTAG口,设定通信模式。

单击图2-32所示右上角的Setup按钮,选择硬件通信模式:

ByteBlaster II或ByteBlasterMV。

然后单击下方的Device栏的ScanChain按钮,对实验板进行扫描。

如果在栏中出现板上FPGA的型号名,表示系统JTAG通信情况正常,可以进行下载。

最后是在File栏选中下载文件(cnt10.sof)。

单击左侧的下载标号,观察左下角下载信息。

下载成