微机原理与接口技术复习笔记.docx

《微机原理与接口技术复习笔记.docx》由会员分享,可在线阅读,更多相关《微机原理与接口技术复习笔记.docx(21页珍藏版)》请在冰豆网上搜索。

微机原理与接口技术复习笔记

程序(program):

实现特定应用数据定义和指令序列。

其中,数据是计算机自动计算对象,而指令(instruction)是指挥计算机执行各种基本操作指令,一条指令相应一种基本操作。

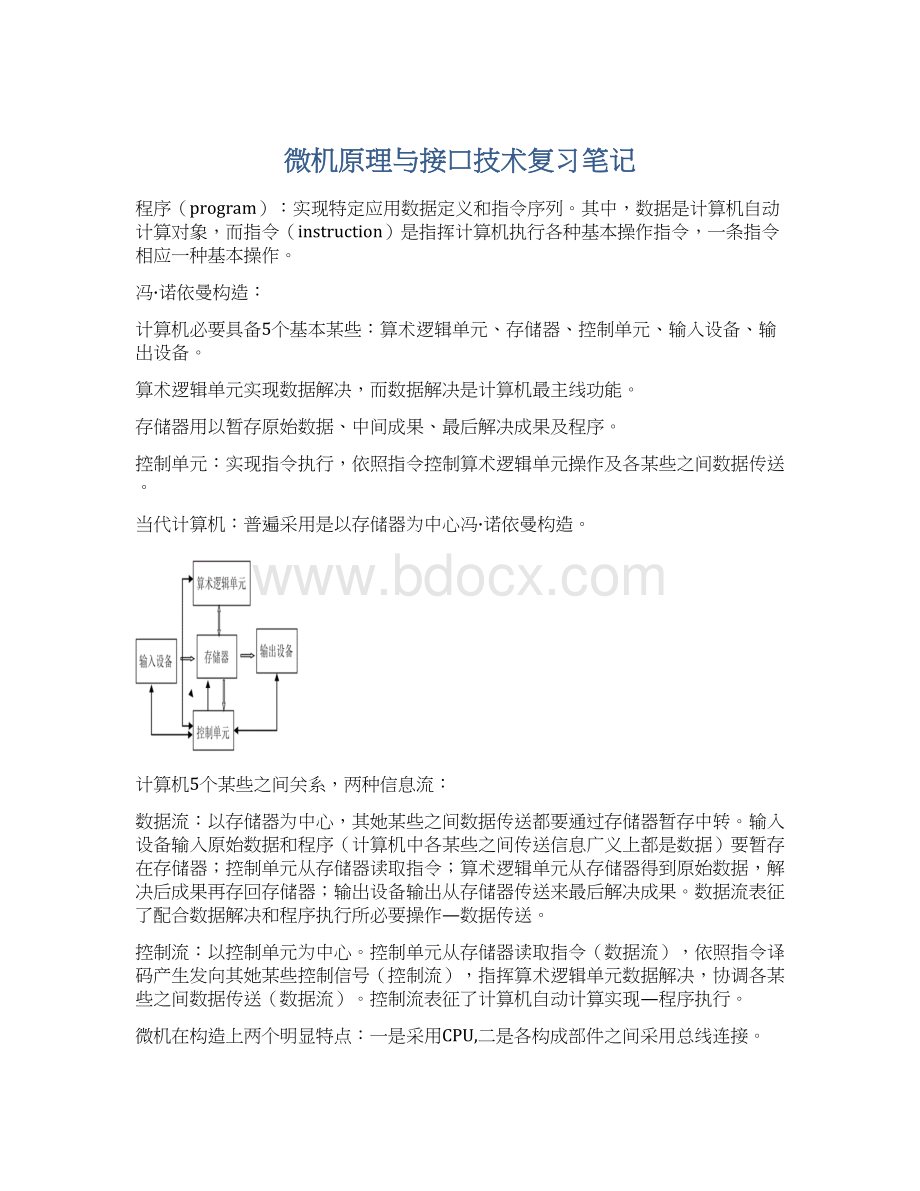

冯·诺依曼构造:

计算机必要具备5个基本某些:

算术逻辑单元、存储器、控制单元、输入设备、输出设备。

算术逻辑单元实现数据解决,而数据解决是计算机最主线功能。

存储器用以暂存原始数据、中间成果、最后解决成果及程序。

控制单元:

实现指令执行,依照指令控制算术逻辑单元操作及各某些之间数据传送。

当代计算机:

普遍采用是以存储器为中心冯·诺依曼构造。

计算机5个某些之间关系,两种信息流:

数据流:

以存储器为中心,其她某些之间数据传送都要通过存储器暂存中转。

输入设备输入原始数据和程序(计算机中各某些之间传送信息广义上都是数据)要暂存在存储器;控制单元从存储器读取指令;算术逻辑单元从存储器得到原始数据,解决后成果再存回存储器;输出设备输出从存储器传送来最后解决成果。

数据流表征了配合数据解决和程序执行所必要操作—数据传送。

控制流:

以控制单元为中心。

控制单元从存储器读取指令(数据流),依照指令译码产生发向其她某些控制信号(控制流),指挥算术逻辑单元数据解决,协调各某些之间数据传送(数据流)。

控制流表征了计算机自动计算实现—程序执行。

微机在构造上两个明显特点:

一是采用CPU,二是各构成部件之间采用总线连接。

时序脉冲频率就是CPU工作频率。

时钟周期:

时序脉冲周期。

时钟周期是微机最小定期单位。

总线周期:

CPU访问一次总线时间即为总线周期。

由四个时钟周期构成。

指令周期:

执行一条指令时间即为指令周期。

指令周期由若干时钟周期够成。

指令周期涉及取指周期和执行周期,执行周期涉及译码、取操作数、数据解决和存操作数等若干基本操作。

微机构成构造:

1、总线:

是连接各部件一组公共信号线;

2、CPU:

算术逻辑单元与控制逻辑单元合称为CPU,即中央解决器;

3、存储器:

存储数据和程序;

4、I/O接口:

输入/输出设备与总线之间缓冲电路。

在外设侧以输入/输出设备通信原则信号实现数据互换,在总线侧则与存储器类似,被CPU通过总线原则信号访问。

在微机构造中,CPU与输入/输出设备不有关,双方可以独立发展。

寻址:

CPU从存储器取指令时,必要发出指令所在存储器单元地址,程序计数器就是暂存在这个地址寄存器。

CPU依照指令访问存储器单元或I/O接口中数据时,也必要发出相应地址,地址寄存器就是暂存在这个地方。

地址总线从CPU向存储器和I/O接口译码电路传送地址。

译码电路对地址译码之后,即可定位到相应存储器单元或I/O端口。

总线功能:

地址总线:

用于CPU寻址存储器和I/O端口,针对采用独立寻址方式和存储器单元数目,定义为8位宽度。

(功能是从CPU向存储器和I/O接口译码电路传送地址。

)

数据总线:

是各部件之间数据传送公共通道。

控制总线:

用于CPU控制单元控制数据总线上传送过程。

三类信号线不是独立作用,协调完毕数据传送:

CPU一方面通过地址总线和M/IO信号线寻址存储器单元或I/O端口,然后通过RD或WR控制线拟定数据传送方向,最后被选通寄存器与CPU通过数据总线实现数据传送。

数据传送是要实现目,数据总线是传送通道,地址总线定位数据所在,控制总线控制数据传送方向,三总线协调作用,共同实现数据传播目。

数据传播一端一定是CPU内部寄存器,由控制单元在CPU内部直接控制,且同一时刻只能有一种CPU工作。

模型机指令集:

共8条。

2条数据解决指令(加法和减法操作),2条存储器访问指令,2条输入/输出访问指令,1条流程控制指令(无条件转移)和1条空操作指令。

伪指令:

用于向汇编程序批示存储器分派汇编命令(directive)。

操作系统:

一种控制硬件和调度软件全面管理计算机资源程序。

执行指令:

涉及取指令和译码发出控制信号两个阶段。

后一阶段是通过指令译码器和控制逻辑电路对设计指令集实现译码,并转换成相应控制信号。

程序计数器(PC):

是控制单元中一种重要寄存器。

其内容是控制单元要执行下一字节指令地址,控制单元依照这个地址从存储器去一字节指令后,就对程序计数器加1,始终批示下一字节指令地址,这样控制单元就可以不断获得指令(取指令后自加1)。

I/O接口数据传送方式:

1、查询方式(Query):

不需增长额外硬件,CPU输入或输出数据时,必要先查询相应I/O接口与否就绪,若就绪则进行数据传送,否则继续查询直到满足条件。

(耗时)

2、中断方式(Interrupt):

当相应I/O接口满足数据传送条件时积极向CPU发出申请,由CPU中断当前执行程序,调用一种相应子程序完毕数据传送,子程序返回后继续执行被中断程序。

(CPU运营效率高,但I/O接口想CPU申请信号需要占用CPU引脚,而响应此过程也需要一定CPU开销,尚有也许增长硬件)

3、DMA方式(DirectMemoryAccess):

DMA方式是通过增长一种硬件(DMA控制器)来专门完毕I/O接口与存储器直接数据互换。

DMA控制器发出地址信号、控制信号,而采用DMA方式时,CPU要出让总线控制权,这时,CPU可以继续执行当前程序,但不能访问总线,还也许影响到对中断响应。

微解决器:

算术逻辑单元和控制逻辑单元,以及暂存数据和指令寄存器组(RegisterSet)、高速缓冲存储器(Cache)等特殊寄存器,这些部件集中在一片大规模或超大规模集成电路芯片上。

(普通,微解决器不包括程序存储单元)

微机:

以微解决器为核心,配以大规模集成电路只读存储器ROM、读写存储器RAM、输入/输出接口及总线。

(微机已具备独立运营能力)

微机系统:

硬件和软件集合。

8086微解决器

是字长16位定点微解决器,内部寄存器、算术逻辑单元和外部数据引脚均为16位,支持8位和16位符号数/无符号数算术运算和数据传送。

提供20位地址引脚(存储周期20位地址有效;I/O周期16位地址有效),可寻址1M存储器空间和64KI/O地址空间。

流水线:

分段寻址:

把整个存储器地址分为若干段,存储器单元定位被分解为所在段和在段内偏移,一次,存储器单元地址由两某些构成:

段地址和偏移地址。

段地址和偏移地址普通记为segment:

offset。

段地址定位断位置,由8086内专门段寄存器提供。

偏移地址定位存储器单元在段内位置,如果是取指操作,偏移地址由指令指针寄器提供;如果是指令执行中访问存储器操作数,偏移地址在指令中指出。

物理存储器:

连接在系统总线上实际存在存储器。

物理地址:

为了寻址物理存储器,微解决器向系统地址总线发出地址。

物理地址是寻址物理存储器线性地址,线性是指持续而有序意思。

8086分段地址称为逻辑地址。

要访问系统总线上物理存储器,逻辑地址必要转换为物理地址,因此逻辑地址只存在于8086中,即逻辑地址对物理存储器是透明。

总线接口单元BIU

段寄存器:

段寄存器组:

CS、SS、DS、ES。

CS(CodeSegment):

保存代码段段地址,代码段用于存储程序指令。

SS(StackSegment):

保存堆栈段段地址,堆栈段用于形成堆栈区。

DS(DataSegment):

保存数据段段地址,数据段用于暂存原始数据和解决后中间成果及最后成果。

ES(ExtraSegment):

保存扩展段段地址,扩展段与数据段类似,普通状况下,数据段用于存储局部变量,扩展段用于存储全局变量。

地址加法器:

将执行单元提供16位费重定位地址重定位为20位存储器物理地址,用于存储器接口访问总线上实际存无物理存储器。

工作分两步:

1.将段寄存器提供16位段地址左移4位,得到20位段首地址。

2.20位段首地址再加上16位偏移地址,即可得到20位物理地址。

指令指针寄存器:

存储代码段内偏移地址,,与CS仪器构成取指所需程序计数器。

程序计数器由总线接口单元自动变化,始终指向顺序存储下一字节指令。

除控制程序流指令可以变化程序计数器外,其她指令都不能直接修改程序计数器。

(8086复位后,CS所有置位而IP所有复位,程序计数器值为FFFFH:

0000H,转换为物理地址为FFFF0H)

存储器接口:

指令流字节队列:

执行单元EU

控制器:

从指令流字节队列顺序读取指令,依照指令译码控制8086中其她某些进行相应操作,以实现指令规定功能。

控制器依照规定修改程序计数器内容之后,必要等待总线接口单元清空指令流字节队列,并按修改后程序计数器内容重新取指填充指令流字节队列后,控制器才干继续从指令流字节队列取指令。

算术逻辑单元:

这个16位算术逻辑单元,依照控制器控制,可完毕8位或16位二进制算术运算和逻辑运算,实现对数据解决。

标志寄存器:

标志寄存器设计为16位,实际使用9位,其中6位用于存储算术逻辑单元运算后成果特性,称为状态标志;

CF(CarryFlag):

进位/借位标志。

(最高位)

PF(ParityFlag):

奇偶标志。

(置位位个数,为偶则PF=1,表达为PE;为奇则PD=0,表达为PO)

AF(AuxiliaryCarryFlag):

辅助进位/借位标志,用于BCD加法调节。

(运算低四位产生了进位或借位,AF=1,表达为AC;否则AF=0,表达为NA)

ZF(ZeroFlag):

零标志。

(运算成果为0,则标志置位;否则复位)

SF(SignFlag):

符号标志,用于标志符号正负。

(运算成果最高位为1,则标志置位,表达为NG;否则标志复位,表达为PL)

OF(OverflowFlag):

溢出标志,用于标志符号数运算成果与否超过表达范畴(无符号数溢出以CF标志)。

(双高异或鉴别)

此外3位通过人为设立,用以控制80863种特定操作,称为控制标志。

TF(TrapFlag):

陷阱标志,也称为单步标志,用于程序单步执行调试。

IF(InterruptFlag):

中断标志。

(IF=1,表达为EI,即容许响应可屏蔽中断祈求;IF=0,表达为DI,即禁止响应可屏蔽中断祈求)

DF(DirectionFlag):

方向标志。

(DF=1,表达为DN,即down,串操作后地址指针自动减量;DF=0,表达为UP,即up,串操作后地址指针自动增量)

通用寄存器组:

是8086中暂存数据,指针寄存器阵列,相比使用存储器,可以减少访问总线次数,有助于提高数据解决速度。

8086包括8个16位寄存器,使用上普通没有限制,但有些特定操作规定必要使用指定寄存器。

寄存器定义为:

AX(Accumulator),累加寄存器;重要用于乘除运算和输入输出操作时存储操作数、优化移动操作。

BX(Base),基寄存器;重要用于存储器间接寻址时存储数据段基地址。

CX(Counter),计数寄存器;重要用于循环、重复、移位操作时存储计数值。

DX(Data),数据寄存器;重要用于乘除运算时存储操作数、输入输出操作间接寻址时存储I/O地址。

SP(StackPointer),堆栈指针寄存器;用于存储站定偏移地址。

BP(BasePointer)基指针寄存器;重要用于存储器间接寻址时存储堆栈段基地址。

SI(SourceIndex),索引源寄存器;重要用于存储器间接寻址时存储索引地址、串操作时存储原串偏移地址。

DI(DestinationIndex),目索引寄存器;重要用于存储器间接寻址时存储索引地址、串操作时存储目串偏移地址。

如果I/O端口中是字数据时,最佳分派偶地址存储。

计算机中指令由操作码和操作数两某些构成。

操作码也称为指令码,阐明计算机要执行哪种操作,是指令中不可缺少某些;而操作数是参加本指令运算数据,也就是各种操作对象。

为限制指令长度,8086指令系统规定,一条指令操作数最多只能有2个,且它们不能同步位于存储器中。

依照指令不同,操作数可以是1个,即单操作数,也可以是