VHDL音乐播放器.docx

《VHDL音乐播放器.docx》由会员分享,可在线阅读,更多相关《VHDL音乐播放器.docx(16页珍藏版)》请在冰豆网上搜索。

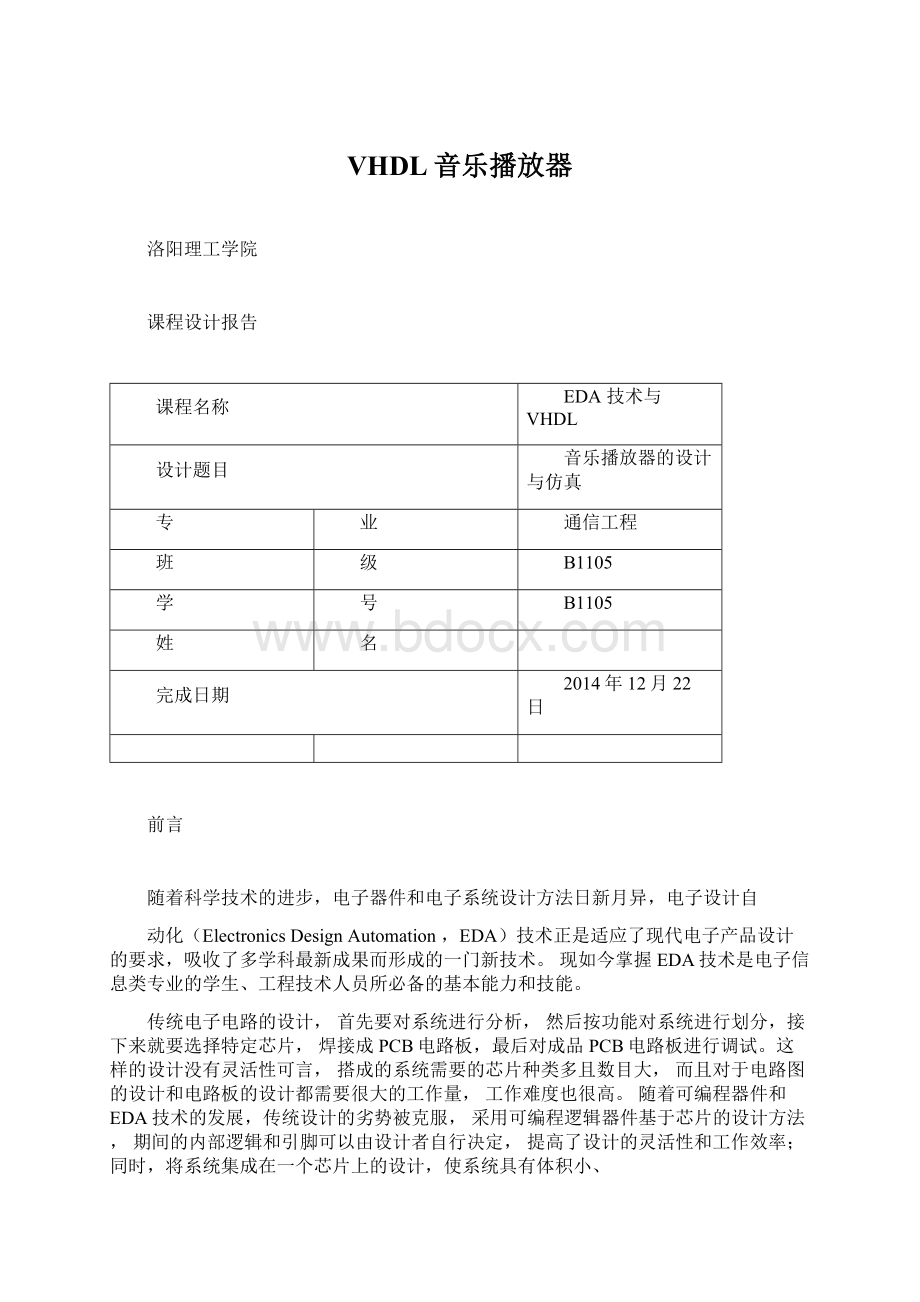

VHDL音乐播放器

洛阳理工学院

课程设计报告

课程名称

EDA技术与VHDL

设计题目

音乐播放器的设计与仿真

专

业

通信工程

班

级

B1105

学

号

B1105

姓

名

完成日期

2014年12月22日

前言

随着科学技术的进步,电子器件和电子系统设计方法日新月异,电子设计自

动化(ElectronicsDesignAutomation,EDA)技术正是适应了现代电子产品设计的要求,吸收了多学科最新成果而形成的一门新技术。

现如今掌握EDA技术是电子信息类专业的学生、工程技术人员所必备的基本能力和技能。

传统电子电路的设计,首先要对系统进行分析,然后按功能对系统进行划分,接下来就要选择特定芯片,焊接成PCB电路板,最后对成品PCB电路板进行调试。

这样的设计没有灵活性可言,搭成的系统需要的芯片种类多且数目大,而且对于电路图的设计和电路板的设计都需要很大的工作量,工作难度也很高。

随着可编程器件和EDA技术的发展,传统设计的劣势被克服,采用可编程逻辑器件基于芯片的设计方法,期间的内部逻辑和引脚可以由设计者自行决定,提高了设计的灵活性和工作效率;同时,将系统集成在一个芯片上的设计,使系统具有体积小、

功耗低、可靠性高等特点。

EDA技术即电子设计自动化技术,它是以可编程逻辑器件(PLD)为载体,以硬件描述语言(HDL)为主要的描述方式,以EDA软件为主要的开发软件的电子设计过程。

它主要采用“自顶向下”的设计方法,设计流程主要包括:

设计输入、综

合、仿真、适配、下载。

EDA技术主要有以下特征:

(1)高层综合的理论和方法取得进展,从而将EDA设计层次由RT级提高到

了系统级,并推出了系统级综合优化工具,缩短了复杂ASIC的设计周期。

(2)采用硬件描述语言来描述10万门以上的设计,并形成了VHDL和

Verilog-HDL两种标准硬件描述语言。

(3)采用平面规划技术对逻辑综合和物理版图设计联合管理,做到在逻辑

设计综合早期阶段就考虑到物理设计信息的影响。

(4)可测性综合设计。

(5)为带有嵌入式IP核的ASIC设计提供软、硬件协同设计工具。

(6)建立并设计工具框架结构的集成化设计环境,以适应当今ASIC规模大

而复杂、数字与模拟电路并存、硬件与软件设计并存、产品上市速度快等特点。

总而言之,EDA技术的出现,给电子信息产业带来了革命性的变革。

一.设计任务及要求

本次课程设计要求使用EDA工具,设计实现简易音乐播放器,理解音名与频率的关系及数控分频原理,经过对整体进行模块化分析、编程、综合、仿真及最终下载,完整实现简易音乐器的播放功能。

用VHDL语言设计乐音的节拍与音符产生电路;用VHDL语言设计分频系数、音符显示数据产生电路;用VHDL语言设计可控分频器电路;理解简易音乐播放器总体设计方案。

掌握基本的VHDL语言;理解音乐播放电路设计方案。

掌握用VHDL语言设计节拍与音符产生电路;掌握用VHDL语言设计分频系数、音符显示数据产生电路;掌握用VHDL语言设计可控分频器电路。

设计结果:

原理图与原程序、电路仿真图、能在实训系统上播放悦耳动听的音乐。

二.设计实现

2.1准备知识

在本次设计中采用了《梁祝》《茉莉花》《虫儿飞》作为要播放的乐曲,

根据声乐知识,组成乐曲的每个音符的发音频率值及其持续的时间是乐曲能连续

演奏所需的两个基本要素,获取这两个要素所对应的数值以及通过纯硬件的手段

来利用这些数值实现所希望乐曲的演奏效果是本实验的关键。

该演奏电路演奏的乐曲是“梁祝”片段,其最小的节拍为1拍。

将1拍的时

长定为0.25秒,则只需要再提供一个4Hz的时钟频率即可产生1拍的时长,演奏的时间控制通过ROM查表的方式来完成。

对于占用时间较长的节拍,如全音符为4拍(重复4),2/4音符为2拍(重复2),1/4音符为1拍(重复1)。

由于音阶频率多为非整数,而分频系数又不能为小数,故必须将得到的分频

数四舍五入取整。

若基准频率过低,则由于分频系数过小,四舍五入取整后的误

差较大,若基准频率过高,虽然误码差变小,但分频结构将变大。

实际的设计应

综合考虑两方面的因素,在尽量减小频率误差的前提下取舍合适的基准频率。

本

设计中选取4MHz的基准频率。

表2-1为简谱中音名与频率的对应关系。

表2.1乐谱编码和乐音频率

音符

编码

频率f

分频数10^6/f

计数值(10^6/2f)-1

1

1

262

10^6/262

1907

2

2

294

10^6/294

1699

3

3

330

10^6/330

1514

低

4

4

349

10^6/349

1431

5

5

392

10^6/392

1274

音

6

6

440

10^6/440

1135

7

7

494

10^6/494

1011

1

8

523

10^6/523

955

2

9

587

10^6/587

850

3

10

659

10^6/659

757

中

4

11

698

10^6/698

715

5

12

784

10^6/784

636

音

6

13

880

10^6/880

567

7

14

988

10^6/988

505

高音

1

15

1047

10^6/1047

476

2.2乐曲演奏电路的结构示意

时钟

乐谱

乐音

存储器

扬声器

分频器

地址

2.3乐曲演奏电路的子结构

顶层结构所包含的模块分别有地址计数器模块(ADDR)、乐音分频器模块

(SPEAKER)、数据存储器(YP)以下便是对各个子模块的分析。

2.3.1地址计数器模块

1.地址计数器功能

在此模块中设置了一个9位二进制计数器(计数最大值为512),这个计数器的计数频率选为4Hz,即每一计数值的停留时间为0.25s,恰好为当全音符设为1s时。

例如,《梁祝》乐曲的第一个音符为“3”,此音在逻辑中停留了4个时钟节拍,即为1s时间,相应地所对应“1”音符分频预置数为1409在ADDR的输入端停留了1s。

随着ADDR中的计数器按4Hz的时钟频率做加法计数时,乐谱逐次被选取,《梁祝》乐曲就开始自然连续的演奏起来了。

2.程序代码

LIBRARYieee;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYADDRIS

PORT(clk:

INSTD_LOGIC;

A:

BUFFERSTD_LOGIC_VECTOR(8DOWNTO0));

END;

ARCHITECTUREONEOFADDRIS

BEGIN

PROCESS(clk)

BEGIN

IF(clk'eventANDclk='1')

THEN

A<=A+1;

ENDIF;

ENDPROCESS;

END;

3.地址计数器符号图

图2.1地址计数器符号图

4.仿真波形图

图2.2地址计数器波形图

图2.3地址计数器波形图

2.3.2乐音分频器

1.乐音分频器模块的功能

此模块的功能首先是提供决定所发音符的分频预置数,而此数在输入端口停

留的时间即为此音符的节拍值。

电路中设置了《梁祝》《茉莉花》《虫儿飞》乐曲全部音符所对应的分频预置数,每一音符的停留时间由音乐节拍和音调发生器模块clk输入频率决定,在此为4Hz。

2.乐音分频器模块的VHDL源程序

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityspeakeris

port(clk:

instd_logic;--1mhz

TN:

instd_logic_vector(3downto0);--乐谱编码

spks:

outstd_logic);

end;

architecturertsofspeakeris

signalFM:

std_logic;

signalcount:

integerrange0to2047;

signaltemp:

integerrange0to2048;

begin

process(TN)

begin

caseTNis

when"0000"=>temp<=2048;

when"0001"=>temp<=1907;

when"0010"=>temp<=1699;

when"0011"=>temp<=1514;

when"0101"=>temp<=1275;

when"0110"=>temp<=1136;

when"0111"=>temp<=1011;

when"1000"=>temp<=955;

when"1001"=>temp<=851;

when"1010"=>temp<=758;

when"1100"=>temp<=637;

when"1101"=>temp<=567;

when"1110"=>temp<=505;

when"1111"=>temp<=477;

whenothers=>temp<=2048;

endcase;

endprocess;

process(clk)

begin

if(clk'eventandclk='1')thencount<=count+1;if(count=temp)thenFM<=notFM;count<=0;endif;

endif;

endprocess;

spks<=FM;

end;

3.乐音分频器符号图

图2.4乐音分频器符号图

4.乐音分频器波形图

图2.5乐音2的波形图

图2.6乐音3的波形图

2.3.3数据存储器

从菜单里的Tools选择MegaWizardPlug-InManager,按照向导完成ROM

的定制,ROM初始化文件见附录。

图2.7数据存储器设计图

2.3.3数据仿真

1.符号图

图2.8存储器和地址计数器符号图

2.波形图

图2.9存储器存入的数据

存储器存入了《梁祝》《茉莉花》《虫儿飞》三首音乐,最小编程单

元是八分音符即每个数字占0.37秒。

每首歌结束之后空0.37*8*2=6秒。

三首

歌共424个地址,即0.37*424=155秒,即两分半左右。

2.3.4时钟分频器

1.二十分频器

程序代码:

libraryieee;

useieee.std_logic_1164.all;

entityfenpin20is

port(clk:

instd_logic;--

out1:

outstd_logic);--

输入

输出

20MHZ信号

1MHZ

end;

architectureoneoffenpin20is

signalT1:

integerrange0to10-1;

signalF1M:

std_logic;

begin

process(clk)

begin

if(clk'eventandclk='1')

then

T1<=T1+1;

if(T1=9)thenF1M<=notF1M;T1<=0;endif;

endif;

endprocess;

out1<=F1M;

end;

符号图:

图2.10分频器符号图

波形图:

图2.11分频器波形图

波形图意义:

此分频器是20分频,即把频率分成其本身频率的1/20。

波形图中clk周期设置为1ns,则cout1的周期是20ns实现20分频。

2.1M分频4hz

程序代码:

libraryieee;

useieee.std_logic_1164.all;

entityFENPIN4HZis

port(clk:

instd_logic;--

输入

1MHZ信号

F:

outstd_logic);--

输出

4HZ

end;

architectureoneofFENPIN4HZis

signalT1:

integerrange0to124999;

signalF1M:

std_logic;

begin

process(clk)

begin

if(clk'eventandclk='1')

then

T1<=T1+1;

if(T1=124999)thenF1M<=notF1M;T1<=0;endif;endif;

endprocess;

F<=F1M;

end;

符号图:

图2.12分频器符号图

波形图:

图2.13分频器波形图

三.整体仿真

3.1符号图

图3.1整体符号图

心得体会

通过这几天的课程设计,使我对VHDL语言有了更加深刻的了解,在书本上

学的理论知识能够运用到了实践中,而课程设计做的成功,增加了我学习EDA

的兴趣,不论在以后的学习中还是工作中,EDA肯定是我们必不可少的设计工具。

通过此次课程设计我已经可以按计划将要求把简易音乐演奏器设计出来,并能实

现所要的功能。

在设计过程中,我遇到了许多问题,通过自己上网、查阅资料、问同学老师,

解决了各个问题,并设计出所需要的要求的程序代码。

在设计过程中,我了解到

设计程序代码的基本过程,首先建立子模块,并对各个模块进行仿真,调试,直

到实现所要的功能为止。

再用元件例化对顶层文件进行仿真,调试,到仿真图正

确止。

最后将程序代码下载到FPGA实验箱上。

总的来说,通过实验,我激发了EDA学习的兴趣,也对这门课程有了更深的理解,对EDA设计软件QuarterⅡ的使用也更加熟练。

更重要的是在此次实验过程中,更好的培养了我们的具体实验的能力。

又因为在在实验过程中有许多实验现象,需要我们仔细的观察,并且分析现象的原因。

特别有时当实验现象与我们预计的结果不相符时,就更加的需要我们仔细的思考和分析了,并且进行适当的调节。

参考文献

[1]张顺兴.数字电路与系统设计.第1版.南京:

东南大学出版社,2004

[2]王玉秀.电工电子基础实验.第1版.南京:

东南大学出版社,2006

[3]孙肖子.模拟电子技术基础.第1版.西安:

西安电子科技大学出版

社,2001.1

[4]谢自美.电子线路设计?

实验?

测试.第2版.武昌:

华中科技大学出版

社,2000.7

[5]张豫滇.电子电路课程设计.第1版.南京:

河海大学出版社,2005.8

[6]沈明山.EDA技术及可编程器件应用实训,科学出版社,2004.6(4):

318-326

[7]刘婷婷,李军.电子设计自动化(EDA).北京师范大学出版社,2007,9

(2):

250-257

[8]赵明富,李立军.EDA技术基础,北京大学出版社,2007.5(5):

221-224

附录:

Addr

+0

+1

+2

+3

+4

+5

+6

+7

0

3

3

3

3

5

5

5

6

8

8

8

8

9

6

8

5

5

16

12

12

12

15

13

12

10

12

24

9

9

9

9

9

9

9

9

32

7

7

6

6

5

5

5

6

40

9

9

9

10

7

7

6

6

48

5

5

5

6

8

8

9

9

56

3

3

8

8

6

5

6

8

64

5

5

5

5

5

5

5

5

72

10

10

10

12

7

7

9

9

80

6

8

5

5

5

5

0

0

88

3

5

5

3

5

6

7

9

96

6

6

6

6

6

6

5

6

104

8

8

8

9

12

12

12

10

112

9

9

10

9

8

8

6

5

120

3

3

3

3

8

8

8

8

128

6

8

6

5

3

5

6

8

136

5

5

5

5

5

5

0

0

144

0

0

0

0

0

0

0

0

152

0

0

0

0

0

0

0

0

160

10

10

10

12

13

15

15

13

168

12

12

12

13

12

12

12

12

176

10

10

10

12

13

15

15

13

184

12

12

12

13

12

12

12

12

192

12

12

12

12

12

12

10

12

200

12

13

13

13

12

12

12

12

梁祝

空6秒

茉莉花

208

10

10

9

10

12

12

10

9+

216

8

8

8

9

8

8

8

8

224

10

9

8

10

9

9

9

10

232

12

12

13

15

12

12

12

12

240

9

9

10

12

9

10

8

6

248

5

5

5

5

6

6

8

8

256

9

9

9

10

8

8

8

6

264

5

5

5

5

5

5

0

0

272

0

0

0

0

0

0

0

0

280

0

0

0

0

0

0

0

0

288

10

10

10

10

11

11

12

12

296

10

10

10

10

9

9

9

9

304

8

8

8

8

9

9

10

10

312

10

10

10

7

7

7

7

7

320

6

6

10

10

9

9

9

9

328

6

6

10

10

9

9

9

9

336

6

6

10

10

9

9

9

8

344

8

8

8

8

8

8

8

8

352

10

9

12

12

12

12

11

10

360

9

9

9

9

12

11

10

9

368

12

12

12

10

9

9

9

9

376

6

6

10

10

9

9

9

9

384

6

6

10

10

9

9

9

9

392

11

10

11

10

9

9

9

9

400

11

10

11

10

15

15

9

8

408

8

8

8

8

8

8

8

8

416

0

0

0

0

0

0

0

0

空6秒

虫儿飞

空3秒