基于verilog的抢答器设计.docx

《基于verilog的抢答器设计.docx》由会员分享,可在线阅读,更多相关《基于verilog的抢答器设计.docx(8页珍藏版)》请在冰豆网上搜索。

基于verilog的抢答器设计

基于verilog的抢答器设计

基于Verilog语言的二路抢答器设计实验报告

电子科学与工程学院121180052李璇

一、实验目的

1、掌握数字系统中触发器、计数器的设计要素。

2、掌握触发器、计数器的VerilogHDL代码编写。

3、进一步掌握ISE软件的用法,学习代码下载的方法。

二、实验步骤

1、设计限时和复位电路。

2、编写限时/复位电路的VerilogHDL代码并综合、仿真。

3、实现限时抢答器并下载到开发板上进行验证。

三、实验原理

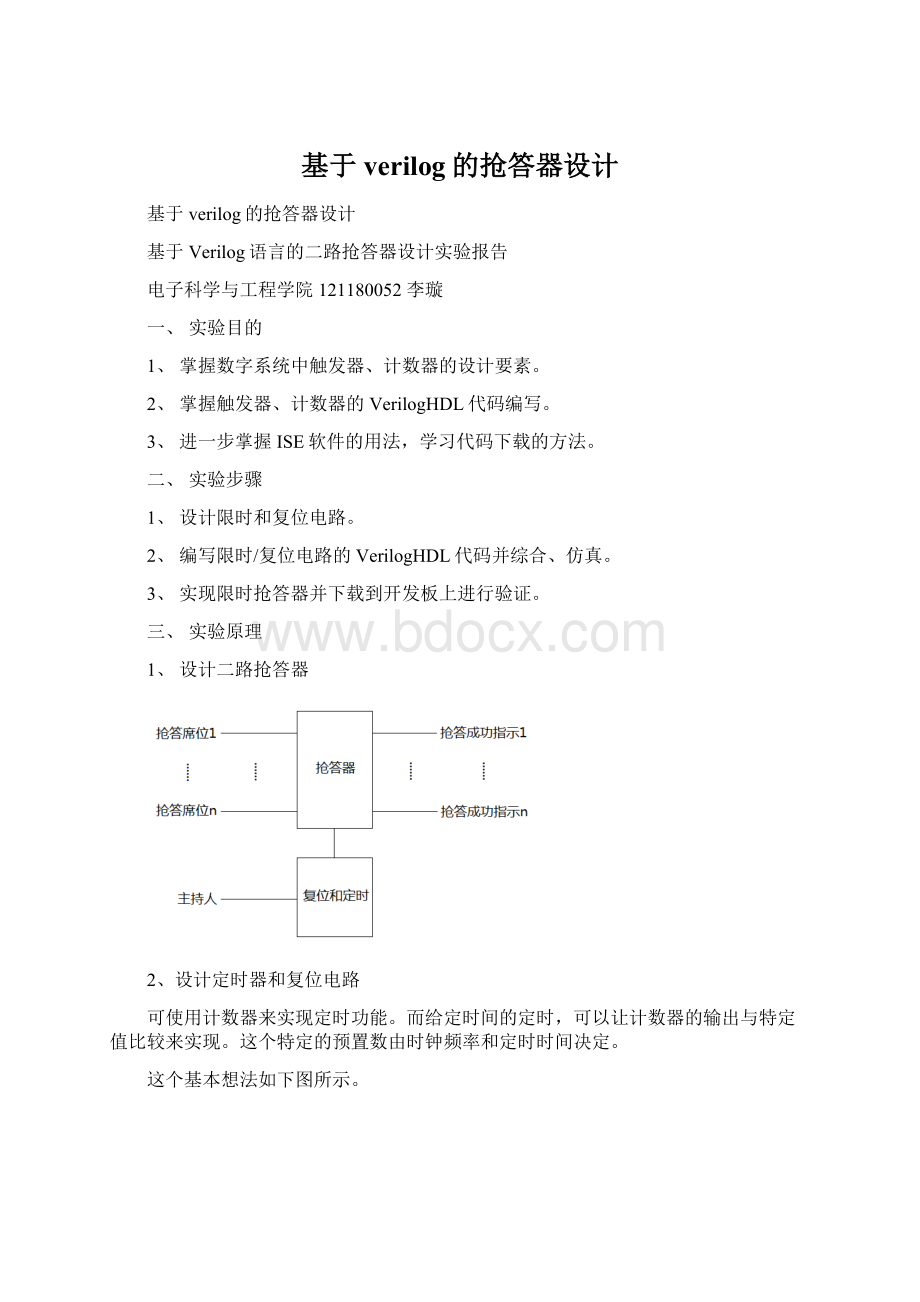

1、设计二路抢答器

2、设计定时器和复位电路

可使用计数器来实现定时功能。

而给定时间的定时,可以让计数器的输出与特定值比较来实现。

这个特定的预置数由时钟频率和定时时间决定。

这个基本想法如下图所示。

图中,“时间到”信号接到计数器的清零端,以便下次计数从0开始。

这里,还需要一个计时开始的功能按键,用来启动计数器的计时。

那么,计数器就需要一个使能端,受控于“计时开始”按键。

我们知道,EN信号是一个持续信号(允许时保持电平),而“时间到”信号是一个持续时间很短的脉冲,因此还需要一个触发器来产生计数器的EN信号。

复位信号由“时间到”信号和复位按键相或来得到。

完整的限时和复位电路如下图所示。

四、实验代码

//主程序部分

Moduleresponder(

inputclk,

inputset,

inputreset,

inputwirein_a,

inputwirein_b,

outputwireq_a,

outputwireq_b,

outputen

);

wireclr;

wire[27:

0]cnt;

wireclk_10;

wiretimeout;

reg[27:

0]n=28'h1ffffff;

assignclr=reset||timeout;

trigtrigger(

.set(set),

.clk(clk_10),

.clr(clr),

.en(en)

);

countcounter(

.clk(clk_10),

.clr(clr),

.en(en),

.cnt(cnt)

);

compcomparator(

.cnt(cnt),

.n(n),

.timeout(timeout)

);

fpga_2main(

.in_a(in_a),

.in_b(in_b),

.clk(clk_10),

.reset(clr),

.q_a(q_a),

.q_b(q_b),

.en(en)

);

endmodule

//触发器trigger部分

moduletrig(

inputset,

inputclk,

inputclr,

outputregen

);

always@(posedgeclk)

beginif(clr)en=0;

else

beginif(set)en=1;

elseen=en;

end

end

endmodule

//计数器counter部分

modulecount(

inputclk,

inputclr,

inputen,

outputreg[27:

0]cnt

);

always@(posedgeclk)

begin

if(clr)

cnt=0;

elseif(en)

cnt=cnt+1;

end

endmodule

//比较器comparator部分

modulecomp(

inputwire[27:

0]cnt,

inputwire[27:

0]n,

outputregtimeout

);

always@(*)

if(cnt==n)

timeout=1;

else

timeout=0;

endmodule

//抢答器部分

modulefpga_2(

inputwirein_a,

inputwirein_b,

inputwireclk,

inputwirereset,

inputen,

outputregq_a,

outputregq_b

);

always@(posedgeclk)

begin

if((q_b==1)||(reset))

q_a=0;

elseif(in_a&&en)

q_a=1;

end

always@(posedgeclk)

begin

if((q_a==1)||(reset))

q_b=0;

elseif(in_b&&en)

q_b=1;

end

endmodule

五、仿真测试

1、测试代码

//Addstimulushere

set=1;

reset=0;

in_a=1;

#1000in_a=0;

#100in_b=1;

#1000reset=1;

#100in_b=0;

#100reset=0;

in_b=1;

#1000in_b=0;

#100in_a=1;

#1000reset=1;

#100in_a=0;

#100reset=0;

end

always#10clk=~clk;

2、仿真结果

六、验证限时电路和复位电路

1在工程中加入DCM

my_clkmy_dcm(

.CLK_IN1(clk),

.CLK_OUT1(clk_10),

.RESET(1'b0),

.LOCKED()

);

2、为模块中的输入输出信号添加管脚约束(管脚定义),在工程中添加UCF文件。

七、实验总结反思

1、通过本次实验,掌握了数字系统中触发器、计数器的设计要素。

掌握了触发器、计数器的VerilogHDL代码编写。

熟悉并掌握了ISE软件的用法,学习了代码下载的方法。

2、编程调试是繁琐复杂的过程,需要极大的耐心。

通过犯错、调试、改错、调试过程的反复,了解了VerilogHDL代码编写过程中容易犯的错误,并避免以后犯类似的错误。

3、VerilogHDL与c语言有相似又有不同,对硬件模块功能的反映比较直观。

起初在对实验原理没有完全掌握的情况下就尝试编程,显然是事倍功半的。

因此在以后的VerilogHDL代码编写过程中应注意先把硬件模块的功能及整个实验思路了解清楚,这样才能有效率地完成代码编写。

4、实验后与同学交流心得,也发现了一些更简洁的代码编写方法,提高VerilogHDL代码编写能力还需不断学习交流。

本次实验所编代码虽然不够简洁,但模块清晰直观,功能明了。