组合逻辑电路设计案例.docx

《组合逻辑电路设计案例.docx》由会员分享,可在线阅读,更多相关《组合逻辑电路设计案例.docx(20页珍藏版)》请在冰豆网上搜索。

组合逻辑电路设计案例

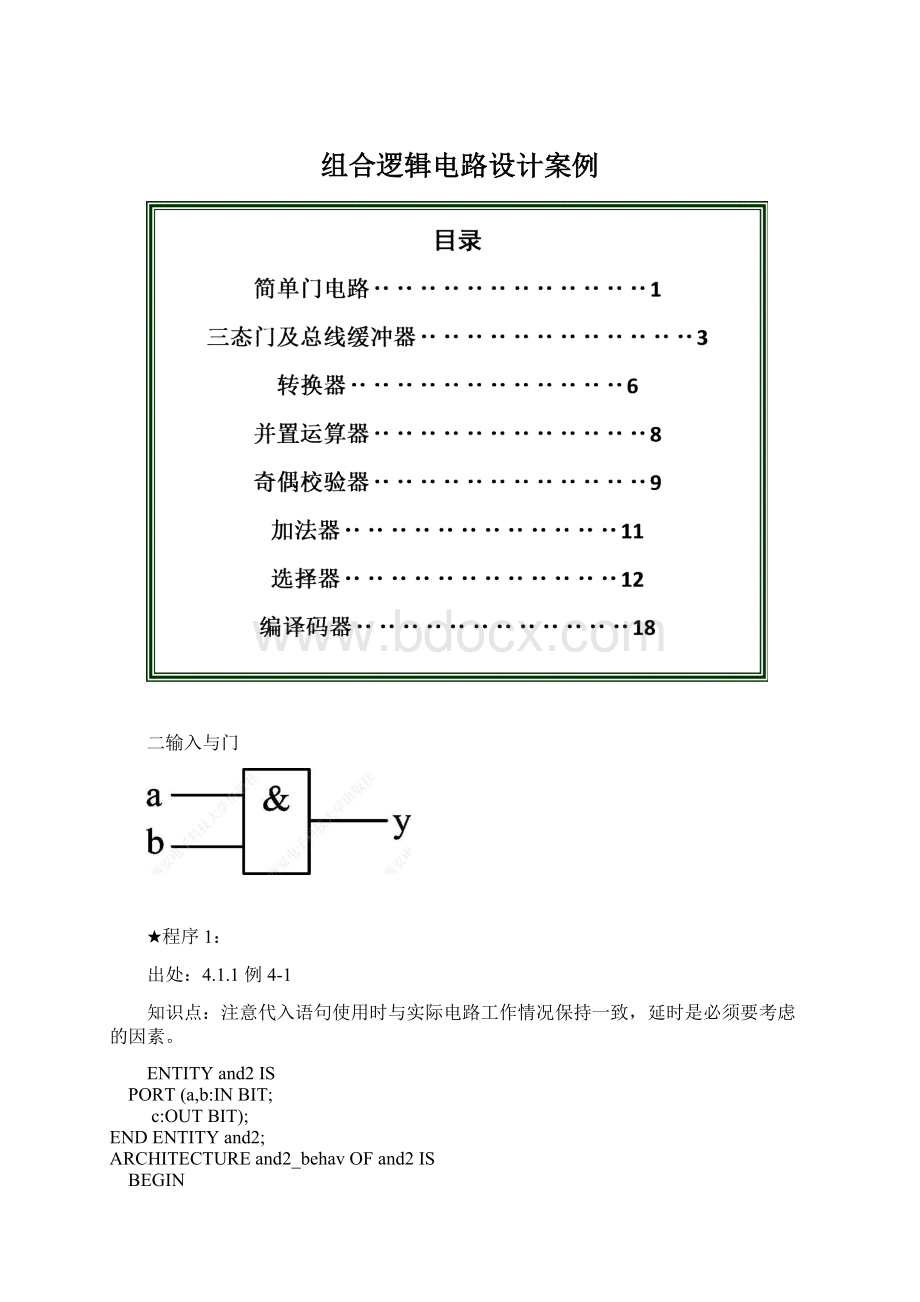

二输入与门

★程序1:

出处:

4.1.1例4-1

知识点:

注意代入语句使用时与实际电路工作情况保持一致,延时是必须要考虑的因素。

ENTITYand2IS

PORT(a,b:

INBIT;

c:

OUTBIT);

ENDENTITYand2;

ARCHITECTUREand2_behavOFand2IS

BEGIN

c<=aANDbAFTER5ns;

ENDARCHITECTUREand2_behav;

★程序2:

ENTITYand2IS

GENERIC(rise,fall:

TIME);

PORT(a,b:

INBIT;

c:

OUTBIT)

ENDENTITYand2;

ARCHITECTUREbehavOFand2IS

SIGNALinternal:

BIT;

BEGIN

internal<=aANDb;

出处:

4.1.4例4-4

知识点:

GENERIC语句常用于不同层次之间点的信息传递,该例中使用GENERIC语句分别对信号的上升时间和下降时间进行了定义。

c<=internalAFTER(rise)WHENinternal='1'ELSE

internalAFTER(fall);

ENDARCHITECTUREbehav;

★程序3:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYnand2IS

PORT(a,b:

INSTD_LOGIC;

y:

OUTSTD_LOGIC);

ENDENTITYnand2;

ARCHITECTUREnand2_2OFnand2IS

BEGIN

t1:

PROCESS(a,b)IS

出处:

7.1.1例7-2

知识点:

采用RTL方式描述构造体,使用CASE语句实现器件的逻辑功能。

VARIABLEcomb:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

comb:

=a&b;

CASEcombIS

WHEN"00"=>y<='1';

WHEN"01"=>y<='1';

WHEN"10"=>y<='1';

WHEN"11"=>y<='0';

WHENOTHERS=>y<='X';

ENDCASE;

ENDPROCESSt1;

ENDARCHITECTUREnand2_2;

三态门电路

★程序1:

出处:

7.1.4例7-15

知识点:

利用IF语句的多选择分支功能描述三态门,注意输入、输出间的控制关系。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYtri_gateIS

PORT(din,en:

INSTD_LOGIC;

dout:

OUTSTD_LOGIC);

ENDENTITYtri_gate;

ARCHITECTUREzasOFtri_gateIS

BEGIN

tri_gate1:

PROCESS(din,en)IS

BEGIN

IF(en='1')THEN

dout<=din;

ELSE

dout<='Z';

ENDIF;

ENDPROCESS;

ENDARCHITECTUREzas;

★程序2:

出处:

7.1.4例7-16

知识点:

使用卫式BLOCK结构描述,注意条件的设立。

ARCHITECTUREblkOFtri_gateIS

BEGIN

tri_gate2:

BLOCK(en='1')

BEGIN

dout<=GUARDEDdin;

ENDBLOCK;

ENDARCHITECTUREblk;

八位单向总线缓冲器

★程序1:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYtri_buf8IS

PORT(din:

INSTD_LOGIC_VECTOR(7DOWNTO0);

dout:

OUTSTD_LOGIC_VECTOR(7DOWNTO0);

en:

INSTD_LOGIC);

ENDENTITYtri_buf8;

ARCHITECTUREzasOFtri_buf8IS

BEGIN

出处:

7.1.4例7-15

知识点:

采用进程结构,使用IF语句描述器件逻辑功能。

tri_buff:

PROCESS(en,din)IS

BEGIN

IF(en='1')THEN

dout<=din;

ELSE

dout<="ZZZZZZZZ";

ENDIF

ENDPROCESS;

ENDARCHITECTUREzas;

双向总线缓冲器

★程序1:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYtri_bigateIS

PORT(a,b:

INOUTSTD_LOGIC_VECTOR(7DOWNTO0);

en:

INSTD_LOGIC;

dr:

INSTD_LOGIC);

ENDENTITYtri_bigate;

ARCHITECTURErtlOFtri_bigate

出处:

7.1.4例7-23

知识点:

使用两个进程语句分别对两个方向上的数据传输进行描述。

SIGNALaout,bout:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

PROCESS(a,dr,en)IS

BEGIN

IF((en='0')AND(dr='1'))THEN

bout<=a;

ELSE

bout<="ZZZZZZZZ";

ENDIF;

b<=bout;

ENDPROCESS;

PROCESS(b,dr,en)IS

BEGIN

IF((en='0')AND(dr='0'))THEN

aout<=b;

ELSE

aout<="ZZZZZZZZ";

ENDIF;

a<=aout;

ENDPROCESS;

ENDARCHITECTURErtl;

位矢量/整数转换器

★程序1:

出处:

2.2.3例2-7

知识点:

构造体采用子程序语句结构的过程语句(PROCEDURE),掌握语句的书写格式即使用方法。

PROCEDUREvector_to_int

(z:

INSTD_LOGIC_VECTOR;

x_f1ag:

OUTBOOLEAN;

q:

INOUTINTEGER)IS

BEGIN

q:

=0;

x_f1ag:

=FALSE;

FORiINz'RANGELOOP

q:

=q*2;

IF(z(i)=1)THEN

q:

=q+1;

ELSIF(z(i)/=0)THEN

x_f1ag:

=TRUE;

ENDIF

ENDLOOP;

ENDPROCEDUREvector_to_int;

标准逻辑矢量/整数转换器

★程序1:

出处:

3.2.4例3-1

知识点:

程序中使用了转换函数,掌握VHDL语言中常用的转换函数的使用方法和所在的包集合。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYadd5IS

PORT(num:

INSTD_LOGIC_VECTOR(2DOWNTO0);

…

);

ENDENTITYadd5;

ARCHITECTURErtlOFadd5IS

SIGNALin_num:

INTEGERRANGE0TO5;

…

BEGIN

in_num<=CONV_INTEGER(num);

…

ENDARCHITECTURErtl;

并置运算器

★程序1:

出处:

3.3.4

知识点:

注意位并置符的使用方法和使用时的注意事项。

…

tmp_b<=bAND(en&en&en&en);

y<=a&tmp_b;

…

八位奇偶校验电路

★程序1:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYparity_checkIS

PORT(a:

INSTD_LOGIC_VECTOR(7DOWNTO0);

y:

OUTSTD_LOGIC);

ENDENTITYparity_check;

ARCHITECTURErtlOFparity_checkIS

BEGIN

PROCESS(a)IS

出处:

5.1.7例5-13

知识点:

注意LOOP语句的书写格式及使用。

VARIABLEtmp:

STD_LOGIC;

BEGIN

tmp:

='0';

FORiIN0TO7LOOP

tmp:

=tmpXORa(i);

ENDLOOP;

y<=tmp;

ENDPROCESS;

ENDARCHITECTURErtl;

★程序2:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYparity_checkIS

PORT(a:

INSTD_LOGIC_VECTOR(7DOWNTO0);

y:

OUTSTD_LOGIC);

ENDENTITYparity_check;

ARCHITECTUREbehavOFparity_checkIS

BEGIN

PROCESS(a)IS

VARIABLEtmp:

STD_LOGIC;

BEGIN

tmp:

='0';

i:

=0;

WHILE(i<8)LOOP

tmp:

=tmpXORa(i);

i:

=i+1;

ENDLOOP;

y<=tmp;

ENDPROCESS;

ENDARCHITECTUREbehav;

出处:

5.1.7例5-14

知识点:

使用带WHILE条件的LOOP语句描述八位奇偶校验电路的逻辑功能。

加法器

★程序1:

出处:

7.1.3例7-15

知识点:

采用COMPONENT语句和PORTMAP语句调用已定义原件半加器half_adder描述全加器。

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYfull_adderIS

PORT(a,b,cin:

INSTD_LOGIC;

s,co:

OUTSTD_LOGIC);

ENDENTITYfull_adder;

ARCHITECTUREfull1OFfull_adderIS

COMPONENThalf_adderIS

PORT(a, b:

INSTD_LOGIC;

s,co:

OUTSTD_LOGIC);

ENDCOMPONENT;

SIGNALu0_co,u0_s,u1_co:

STD_LOGIC;

BEGIN

u0:

half_adderPORTMAP(a,b,u0_s,u0_co);

u1:

half_adderPORTMAP(u0_s,cin,s,u1_co);

co<=u0_coORu1_co;

ENDARCHITECTUREfull1;

半加器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYhalf_adderIS

PORT(a,b:

INSTD_LOGIC;

s,co:

OUTSTD_LOGIC);

ENDENTITYhalf_adder;

ARCHITECTUREhalf1OFhalf_adderIS

SIGNALc,d:

STD_LOGIC;

BEGIN

c<=aORb;

d<=aNANDb;

co<=NOTd;

s<=cANDd;

ENDARCHITECTUREhalf1;

二选一选择器

★程序1:

出处:

1.2

知识点:

理解硬件描述语言能够比电原理图更有效的表示硬件电路的特性。

ENTITYmuxIS

GENERIC(m:

TIME:

=1ns);

PORT(d0, d1:

INBIT;

sel:

INBIT;

q:

OUTBIT);

ENDENTITYmux;

ARCHITECTUREconnectOFmuxIS

BEGIN

出处:

2.1

知识点:

作为一个完整的VHDL程序出现,掌握程序框架的结构;实体与构造体的书写格式;各项参数的含义。

PROCESS(d0,d1,sel)IS

VARIBLEtemp1,temp2,temp3:

BIT;

BEGIN

temp1:

=d0ANDsel;

temp2:

=d1AND(NOTsel);

temp3:

=temp1ORtemp2;

q<=temp3AFTERm;

ENDPROCESS

ENDARCHITECTUREconnect;

★程序2(与程序1的描述方式一致,但对原件逻辑功能的描述更简单):

出处:

2.1.2例2-3

知识点:

构造体内部语句采用并行处理方式,即介于BEGIN与END之间的语句将会被同时执行。

ENTITYmuxIS

PORT(d0, d1:

INBIT;

sel:

INBIT;

q:

OUTBIT);

ENDENTITYmux;

ARCHITECTUREdataflowOFmuxIS

BEGIN

q<=(d0ANDsel)OR(NOTselANDd1);

ENDARCHITECTUREdataflow;

★程序3:

ENTITYmuxIS

PORT(d0,d1,sel:

INBIT;

q:

OUTBIT);

ENDENTITYmux;

ARCHITECTUREconnectOFmuxIS

SIGNALtmp1,tmp2,tmp3:

BIT;

BEGIN

cale:

BLOCK

出处:

2.2.1例2-4

知识点:

构造体采用BLOCK结构,掌握块语句结构的书写格式及使用方法。

BEGIN

tmp1<=d0ANDsel;

tmp2<=d1AND(NOTsel);

tmp3<=tmp1ORtmp2;

q<=tmp3;

ENDBLOCKcale;

ENDARCHITECTUREconnect;

★程序4:

出处:

2.2.2例2-6

知识点:

构造体采用进程语句结构,掌握进程(PROCESS)语句结构的书写格式及使用方法。

ENTITYmuxIS

PORT(d0, d1, sel:

INBIT;

q:

OUTBIT);

ENDENTITYmux;

ARCHITECTUREconnectOFmuxIS

BEGIN

cale:

PROCESS(d0, d1, sel)IS

VARIABLEtmp1, tmp2, tmp3:

BIT;

BEGIN

tmp1:

=d0ANDsel;

tmp2:

=d1AND(NOTsel);

tmp3:

=tmp1ORtmp2;

q<=tmp3;

ENDPROCESScale;

ENDARCHITECTUREconnect;

★程序5:

ENTITYmux2IS

PORT(d0, d1, sel:

INBIT;

q:

OUTBIT);

ENDENTITYmux2;

ARCHITECTUREstructOFmux2IS

COMPONENTand2IS

PORT(a, b:

INBIT;

c:

OUTBIT);

ENDCOMPONENT;

出处:

4.3.1例4-16

知识点:

二选一电路采用结构化的方式描述构造体,使用了COMPONENT语句和PORTMAP语句,属于最底层的描述方式,与实际电路最贴近。

COMPONENTor2IS

PORT(a, b:

INBIT;

c:

OUTBIT);

ENDCOMPONENT;

COMPONENTinvIS

PORT(a:

INBIT;

c:

OUTBIT);

ENDCOMPONENT;

SIGNALaa,ab,nsel:

BIT;

BEGIN

u1:

invPORTMAP(sel,nsel);

u2:

and2PORTMAP(nsel,d1,ab);

u3:

and2PORTMAP(d0,sel,aa);

u4:

or2PORTMAP(aa,ab,q);

ENDARCHITECTUREstruct;

★程序6:

出处:

5.1.5例5-7

知识点:

利用IF语句的二选择控制功能对二选一电路的逻辑控制进行描述。

ARCHITECTURErtlOFmux2IS

BEGIN

PROCESS(a,b,sel)IS

BEGIN

IF(sel='1')THEN

c<=a;

ELSE

c<=b;

ENDIF;

ENDPROCESS;

ENDARCHITECTURErtl;

四选一选择器

★程序1:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYmux4IS

PORT(i0,i1,i2,i3,a,b:

INSTD_LOGIC;

q:

OUTSTD_LOGIC);

ENDENTITYmux4;

ARCHITECTUREbehavOFmux4IS

SIGNALsel:

INTEGER;

出处:

5.2.4例5-18

知识点:

注意选择信号代入语句的使用。

条件并行执行,不具有优先级。

出处:

4.1.1例4-2

知识点:

注意条件代入语句的使用。

BEGIN

WITHselSELECT

q<=i0AFTER10nsWHEN0,

i1AFTER10nsWHEN1,

i2AFTER10nsWHEN2,

i3AFTER10nsWHEN3,

'X'AFTER10nsWHENOTHERS;

sel<=0WHENa='0'ANDb='0'ELSE

1WHENa='1'ANDb='0'ELSE

2WHENa='0'ANDb='1'ELSE

3WHENa='1'ANDb='1'ELSE

4;

ENDARCHITECTUREbehav;

★程序2:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGEND.ALL;

ENTITYmux4IS

PORT(input:

INSTD_LOGIC_VECTOR(3DOWNTO0);

sel:

INSTD_LOGIC_VECTOR(1DOWNTO0);

y:

OUTSTD_LOGIC);

出处:

4.2.1例4-6

知识点:

采用RTL描述方式描述四选一电路,注意构造体的逻辑功能描述的方法,与上例进行比较。

ENDENTITYmux4;

ARCHITECTURErtlOFmux4IS

BEGIN

y<=input(0)WHENsel="00"ELSE

input

(1)WHENsel="01"ELSE

input

(2)WHENsel="10"ELSE

input(3);

ENDARCHITECTURErtl;

★程序3:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux4IS

PORT(input:

INSTD_LOGIC_VECTOR(3DOWNTO0);

sel:

INSTD_LOGIC_VECTOR(1DOWNTO0);

y:

OUTSTD_LOGIC);

ENDENTITYmux4;

ARCHITECTURErtlOFmux4IS

BEGIN

出处:

5.1.5例5-8

知识点:

利用IF语句的多选择控制功能对四选一电路的逻辑功能进行描述;选择条件顺序执行,具有优先级。

注意语句自身为顺序语句。

PROCESS(input,sel)IS

BEGIN

IF(sel="00")THEN

y<=input(0);

ELSIF(sel="01")THEN

y<=input

(1);

ELSIF(sel="10")THEN

y<=input

(2);

ELSE

y<=input(3);

ENDIF;

ENDPROCESS;

ENDARCHITECTURErtl;

★程序4:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux4IS

PORT(a,b,i0,i1,i2,i3:

INSTD_LOGIC;

q:

OUTSTD_LOGIC);

ENDENTITYmux4;

ARCHITECTUREmux4_behaveOFmux4IS

SIGNALsel:

INTEGERRANGE0TO3;

BEG