计算机组成原理第五章答案.docx

《计算机组成原理第五章答案.docx》由会员分享,可在线阅读,更多相关《计算机组成原理第五章答案.docx(17页珍藏版)》请在冰豆网上搜索。

计算机组成原理第五章答案

第5章习题参考答案

1.请在括号内填入适当答案。

在CPU中:

(1)保存当前正在执行的指令的寄存器是(IR);

(2)保存当前正在执行的指令地址的寄存器是(AR)

(3)算术逻辑运算结果通常放在(DR)和(通用寄存器)。

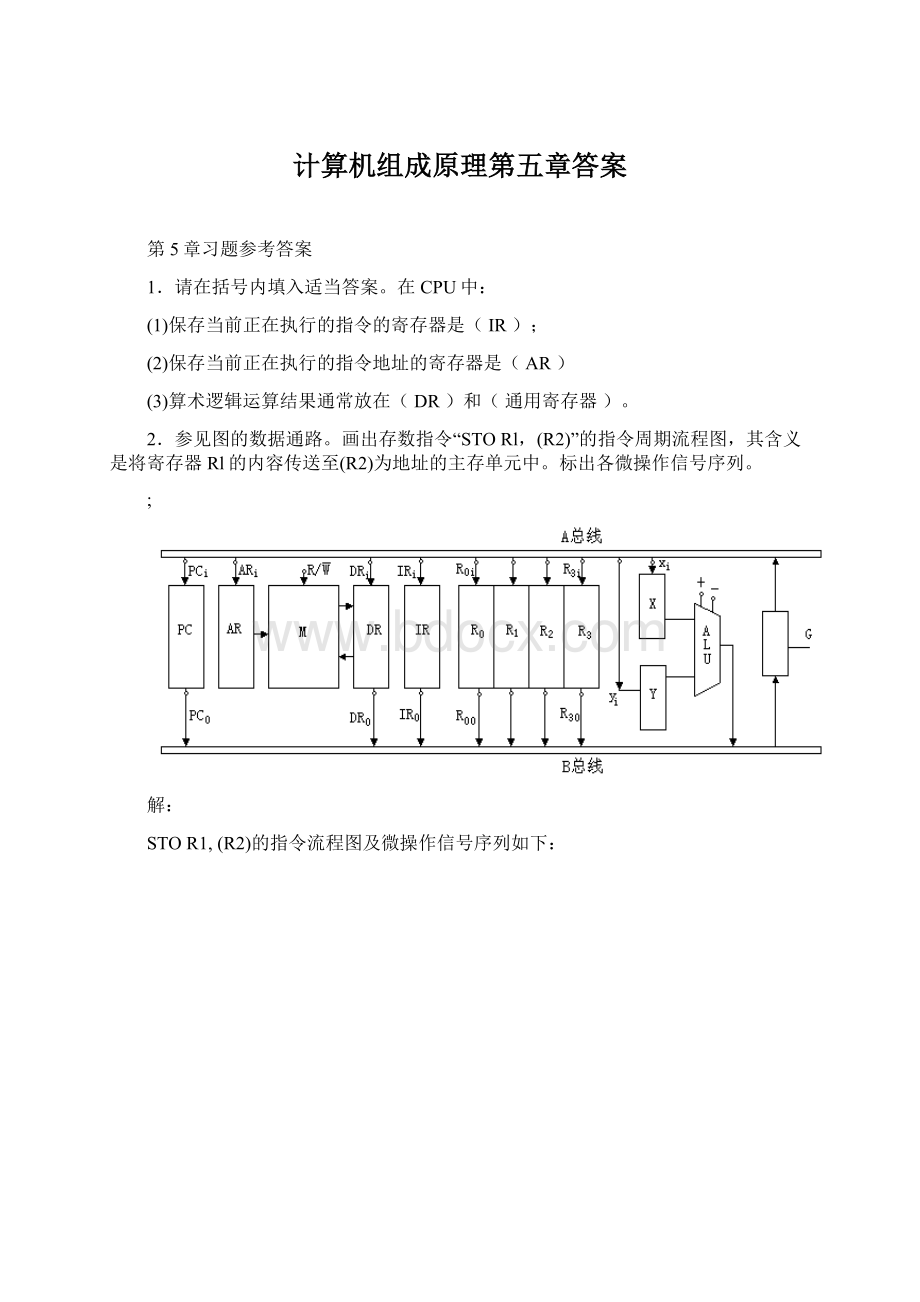

2.参见图的数据通路。

画出存数指令“STORl,(R2)”的指令周期流程图,其含义是将寄存器Rl的内容传送至(R2)为地址的主存单元中。

标出各微操作信号序列。

;

解:

STOR1,(R2)的指令流程图及微操作信号序列如下:

3.参见图的数据通路,画出取数指令“LAD(R3),R0”的指令周期流程图,其含义是将(R3)为地址主存单元的内容取至寄存器R2中,标出各微操作控制信号序列。

解:

LADR3,(R0)的指令流程图及为操作信号序列如下:

4.假设主脉冲源频率为10MHz,要求产生5个等间隔的节拍脉冲,试画出时序产生器的逻辑图。

解:

5.如果在一个CPU周期中要产生3个节拍脉冲;Tl=200ns,T2=400ns,T3=200ns,试画出时序产生器逻辑图。

;

解:

取节拍脉冲Tl、T2、T3的宽度为时钟周期或者是时钟周期的倍数即可。

所以取时钟源提供的时钟周期为200ns,即,其频率为5MHz.;由于要输出3个节拍脉冲信号,而T3的宽度为2个时钟周期,也就是一个节拍电位的时间是4个时钟周期,所以除了C4外,还需要3个触发器——Cl、C2、C3;并令

;

;

,由此可画出逻辑电路图如下:

6.假设某机器有80条指令,平均每条指令由4条微指令组成,其中有一条取指微指令是所有指令公用的。

已知微指令长度为32位,请估算控制存储器容量。

解:

80条指令,平均每条指令由4条微指令组成,其中有一条公用微指令,所以总微指令条数为80(4-1)+1=241条微指令,每条微指令32位,所以控存容量为:

24132位

7.某ALU器件是用模式控制码MS3S2S1C来控制执行不同的算术运算和逻辑操作。

下表列出各条指令所要求的模式控制码,其中y为二进制变量,φ为0或l任选。

—

试以指令码(A,B,H,D,E,F,G)为输入变量,写出控制参数M,S3,S2,Sl,C的逻辑表达式。

指令码

M

S3

S2

S1

C

A,B

H,D

E

~

F

G

0

0

0

0

1

0

1

0

【

1

0

1

1

1

1

1

1

0

0

)

1

1

0

1

y

y

解:

由表可列如下逻辑方程

(

M=G

S3=H+D+F

S2=A+B+D+H+E+F+G

S1=A+B+F+G

C=H+D+Ey+Fy

8.某机有8条微指令I1—I8,每条微指令所包含的微命令控制信号如下表所示。

a—j分别对应10种不同性质的微命令信号。

假设一条微指令的控制字段仅限为8位,请安排微指令的控制字段格式。

微指令

、

a

b

c

d

e

f

g

h

i

j

}

I1

|

I2

"

I3

!

I4

【

I5

-

I6

I7

】

I8

%

解:

因为有10种不同性质的微命令信号,如果采用直接表示法则需要10位控制字段,现控制字段仅限于8位,那么,为了压缩控制字段的长度,必须设法把一个微指令周期中的互斥性微命令组合在一个小组中,进行分组译码。

经分析,(e,f,h)和(b,i,j)、或(d,i,j)和(e,f,h)、或(g,b,j)和(i,f,h)均是不可能同时出现的互斥信号,所以可将其通过2:

4译码后输出三个微命令信号(00表示该组所有的微命令均无效),而其余四个微命令信号用直接表示方式。

因此可用下面的格式安排控制字段。

efh

bij

acdg

XX

&

XX

或:

efh

dij

abcg

XX

#

XX

或:

fhi

bgj

acde

XX

.

XX

9.微地址转移逻辑表达式如下:

μA8=P1·IR6·T4

μA7=P1·IR5·T4

μA6=P2·C·T4

其中μA8—μA6为微地址寄存器相应位,P1和P2为判别标志,C为进位标志,IR5和IR6为指令寄存器的相应位,T4为时钟周期信号。

说明上述逻辑表达式的含义,画出微地址转移逻辑图。

解:

<

μA5=P3·IR5·T4

μA4=P3·IR4·T4

μA3=P1·IR3·T4

μA2=P1·IR2·T4

μA1=P1·IR1·T4

μA0=P1·IR0·T4+P2·C·T4

用触发器强置端(低有效)修改,前5个表达式用“与非”门实现,最后1个用“与或非”门实现

μA2、μA1、μA0触发器的微地址转移逻辑图如下:

(其他略)

#

10.某计算机有如下部件,ALU,移位器,主存M,主存数据寄存器MDR,主存地址寄存器MAR,指令寄存器IR,通用寄存器R0R3,暂存器C和D。

(1)请将各逻辑部件组成一个数据通路,并标明数据流动方向。

(2)画出“ADDR1,R2”指令的指令周期流程图。

解:

(1)设该系统为单总线结构,暂存器C和D用于ALU的输入端数据暂存,移位器作为ALU输出端的缓冲器,可对ALU的运算结果进行附加操作,则数据通路可设计如下:

(2)根据上面的数据通路,可画出“ADDR1,R2”(设R1为目的寄存器)的指令周期流程图如下:

~

11.已知某机采用微程序控制方式,控存容量为512*48位。

微程序可在整个控存中实现转移,控制微程序转移的条件共4个,微指令采用水平型格式,后继微指令地址采用断定方式。

请问;

(1)微指令的三个字段分别应为多少位

(2)画出对应这种微指令格式的微程序控制器逻辑框图。

解:

(1)因为容量为512*48位,所以下址字段需用9位,控制微程序转移的条件有4个,所以判别测试字段需4位或(3位译码),因此操作控制字段的位数48-9-4=35位(或48-9-3=36位)

)

(2)微程序控制器逻辑框图参见教材图

12.今有4级流水线,分别完成取指、指令译码并取数、运算、送结果四步操作。

今假设完成各步操作的时间依次为100ns,100ns,80ns,50ns。

请问;

(1)流水线的操作周期应设计为多少

(2)若相邻两条指令发生数据相关,而且在硬件上不采取措施,那么第2条指令要推迟多少时间进行

(3)如果在硬件设计上加以改进,至少需推迟多少时间

/

答:

(1)流水操作周期为max(100,100,80,50)=100ns

(2)若相邻两条指令发生数据相关,而且在硬件上不采取措施,那么在第1条指令“送结果”步骤完成后,第2条指令的“取数”步骤才能开始,也就是说,第2条指令要推迟两个操作周期,即200ns才能进行。

(3)如果在硬件设计上加以改进,采用定向传送的技术,则只要第1条指令完成“运算”的步骤,第2条指令就可以“取数”了,因此至少需推迟100ns。

13.指令流水线有取指(IF)、译码(ID)、执行(EX)、访存(MEM)、写回寄存器堆(WB)五个过程段,共有20条指令连续输入此流水线。

(1)画出流水处理的时空图,假设时钟周期为100ns。

(2)求流水线的实际吞吐率(单位时间里执行完毕的指令数)。

(3)求流水线的加速比。

}

解:

(1)流水处理的空图如下,其中每个流水操作周期为100ns:

空间S

'

I1

I2

I15

I16

I17

I18

I19

I20

`

&

WB

I1

^

I2

I15

I16

I17

I18

I19

I20

MEM

!

I1

I2

I3

I16

I17

I18

~

I19

I20

EX

I1

I2

I3

【

I4

I17

I18

I19

I20

ID

@

I1

I2

I3

I4

I5

I18

I19

I20

~

IF

I1

I2

I3

I4

I5

·

I6

I19

I20

?

1

2

3

4

5

6

19

20

21

|

22

23

24

时间T

(2)流水线的实际吞吐量:

执行20条指令共用5+119=24个流水周期,共2400ns,所以实际吞吐率为:

(3)流水线的加速比为:

设流水线操作周期为τ,

则n指令串行经过k个过程段的时间为n*k*τ;

)

而n条指令经过可并行的k段流水线时所需的时间为(k+n-1)*τ;

故20条指令经过5个过程段的加速比为:

14.用时空图法证明流水计算机比非流水计算机具有更高的吞吐率。

解:

设流水计算机的指令流水线分为4个过程段:

IF、ID、EX、WB,则流水计算机的时空图如下:

空间S

—

I1

I2

I3

I4

I5

;

WB

*

I1

I2

I3

I4

I5

EX

`

I1

I2

I3

I4

I5

I6

ID

;

I1

I2

I3

I4

I5

I6

I7

IF

·

I1

I2

I3

I4

I5

I6

I7

I8

\

1

2

3

4

5

6

7

8

时间T

!

非流水计算机的时空图:

空间S

I1

`

I2

…

WB

I1

I2

/

EX

I1

I2

*

ID

I1

I2

|

IF

I1

I2

^

1

2

3

4

5

6

7

8

?

时间T

由图中可以看出,同样的8个操作周期内,流水计算机执行完了5条指令,而非流水计算机只执行完了2条指令;由此,可看出流水计算机比非流水计算机具有更高的吞吐率。

15.用定量描述法证明流水计算机比非流水计算机具有更高的吞吐率。

证明:

设流水计算机具有k级流水线,每个操作周期的时间为,执行n条指令的时间为:

;

吞吐率为:

)

而非流水计算机,执行n条指令的时间为:

;

吞吐率为:

当n=1时,

;

当n>1时,

,即:

流水计算机具有更高的吞吐率。

16.判断以下三组指令中各存在哪种类型的数据相关

(1)I1LADR1,A;M(A)→R1,M(A)是存储器单元

I2ADDR2,Rl;(R2)+(R1)→R2

(2)I1ADDR3,R4;(R3)+(R4)→R3

~

I2MULR4,R5;(R4)(R5)→R4

(3)I1LADR6,B;M(B)→R6,M(B)是存储器单元

I2MULR6,R7;(R6)(R7)→R6

解:

(1)I1的运算结果应该先写入R1,然后再在I2中读取R1的内容作为操作数,所以是发生RAW(“写后读”)相关

(2)WAR

(3)RAW和WAW两种相关

\

17.参考图所示的超标量流水线结构模型,现有如下6条指令序列:

I1LADR1,B;M(B)→R1,M(B)是存储器单元

I2SUBR2,Rl;(R2)-(R1)→R2

I3MULR3,R4;(R3)*(R4)→R3

I4ADDR4,R5;(R4)+(R5)→R4

I5LADR6,A;M(A)→R6,M(A)是存储器单元

I6ADDR6,R7;(R6)+(R7)→R6

请画出:

(1)按序发射按序完成各段推进情况图。

(2)按序发射按序完成的流水线时空图。

|

解:

(1)按序发射按序完成各段推进情况图如下(仍设F、D段要求成对输入;F、D、W段只需1个周期;加需要2个周期;乘需要3个周期;存/取数需要1个周期;执行部件内部有定向传送,结果生成即可使用):

取指段

I1

I2

I3

I4

I5

I6

译码段

I1

I2

I2

I3

I4

I5

I6

I6

执行段

I1

I2

I2I4

I3

I5

I4

I3

I6

I3

I6

取/存

加法器

乘法器

写回段

I1

I2

I3

I4

I5

I6

(2)按序发射按序完成的流水时空图如下:

1

2

3

4

5

6

7

8

9

10

11

时钟

I1

F

D

E

W

I2

F

D

E

E

W

I3

F

D

E

E

E

W

I4

F

D

E

E

W

I5

F

D

E

W

I6

F

D

E

E

W

超标量流水线的时空图

?

]