常用数字电路单元的结构.docx

《常用数字电路单元的结构.docx》由会员分享,可在线阅读,更多相关《常用数字电路单元的结构.docx(18页珍藏版)》请在冰豆网上搜索。

常用数字电路单元的结构

第3章常用数字单元电路结构

3.1引言

本章介绍CMOS数字电路中常用单元电路的结构。

本章暂不考虑电路性能问题,因此可将MOS管看成受电压控制的开关。

3.2互补静态CMOS逻辑

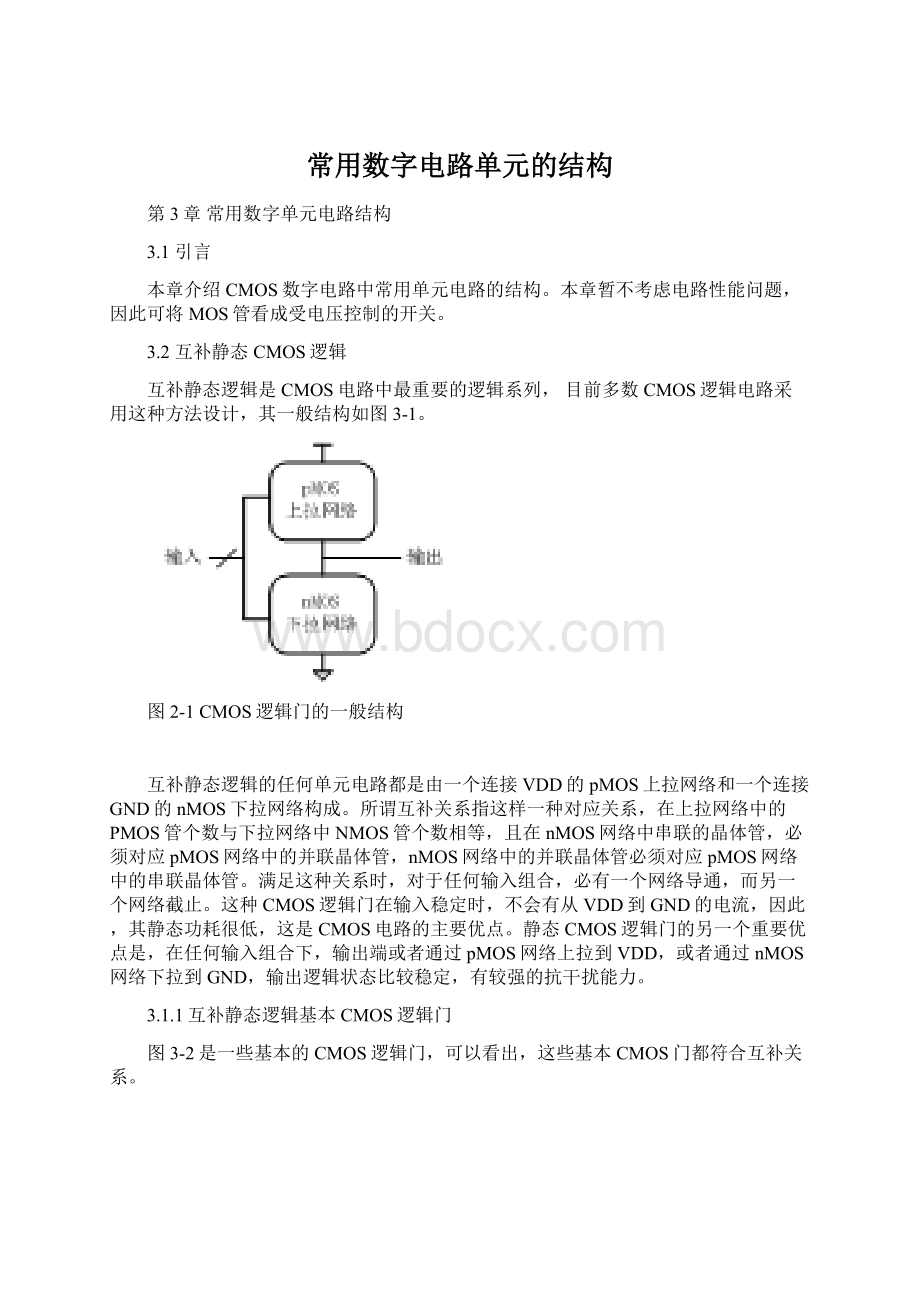

互补静态逻辑是CMOS电路中最重要的逻辑系列,目前多数CMOS逻辑电路采用这种方法设计,其一般结构如图3-1。

图2-1CMOS逻辑门的一般结构

互补静态逻辑的任何单元电路都是由一个连接VDD的pMOS上拉网络和一个连接GND的nMOS下拉网络构成。

所谓互补关系指这样一种对应关系,在上拉网络中的PMOS管个数与下拉网络中NMOS管个数相等,且在nMOS网络中串联的晶体管,必须对应pMOS网络中的并联晶体管,nMOS网络中的并联晶体管必须对应pMOS网络中的串联晶体管。

满足这种关系时,对于任何输入组合,必有一个网络导通,而另一个网络截止。

这种CMOS逻辑门在输入稳定时,不会有从VDD到GND的电流,因此,其静态功耗很低,这是CMOS电路的主要优点。

静态CMOS逻辑门的另一个重要优点是,在任何输入组合下,输出端或者通过pMOS网络上拉到VDD,或者通过nMOS网络下拉到GND,输出逻辑状态比较稳定,有较强的抗干扰能力。

3.1.1互补静态逻辑基本CMOS逻辑门

图3-2是一些基本的CMOS逻辑门,可以看出,这些基本CMOS门都符合互补关系。

图3-2基本CMOS逻辑门

互补静态CMOS逻辑门的pMOS网络和nMOS网络的导通逻辑恰好相反,如果用FN表示nMOS网络的导通逻辑,FP表示pMOS网络的导通逻辑,则必须有

(3-1)

例如,在与非门中,

整个门的逻辑关系与pMOS网络的导通逻辑相同,但观察nMOS网络的导通条件更容易些。

这种关系也可以推广到更复杂的电路。

CMOS逻辑门总是含有反相关系,nMOS下拉网络总是在部分或全部输入为“1”时导通,从而使输出为“0”。

对于任何互补CMOS逻辑门,判断逻辑关系的方法是:

根据nMOS网络的导通逻辑,再加上“非”逻辑,就可以得到整个门的逻辑关系。

在互补静态CMOS逻辑门中,只有反相器、与非门和或非门是最基本的逻辑门,而与门和或门要利用上述基本逻辑门实现,也就是说,一个与门的晶体管数相当于相同输入的与非门的晶体管数加2。

在数字CMOS工艺中,PMOS管的衬底总是接VDD的,NMOS管的衬底总是接GND的,在原理图中可以省略。

图3-3串联晶体管的延迟问题

(3-2)

逻辑门的输入端个数,也称为扇入(fanin)或扇入系数。

静态CMOS逻辑门的扇入不能太大,较大的扇入会导致电路内部存在多个晶体管串联的支路。

由于扩散区电容的影响,串联支路的延迟与晶体管个数N存在平方关系,当N较大时,延迟时间迅速增加。

在实际设计中,很少使用超过4个输入端的逻辑门。

此问题将在后续章节还要进一步讨论。

3.1.3复合逻辑门

除基本逻辑门外,具有“与或非(AOI)”形式的电路也是符合互补关系的静态CMOS逻辑电路,这种“门”称为复合逻辑门或AOI逻辑门。

图3-4复合逻辑门

AOI逻辑门的逻辑关系可以根据下拉网络的导通条件判断。

在图2-4(a)中,nMOS下拉网络的导通条件为C&(A|B),因此整个门的逻辑关系为

(3-3)

图2-3(b)中,nMOS下拉网络导通条件为D&(A|B|C),所以门的逻辑关系为

(3-4)

可见,从nMOS下拉网络得到门的逻辑关系是很容易的。

反之,如果给出类似(3-3)的逻辑方程,设计AOI型逻辑门的方法是先按“非”运算符号下的逻辑关系画出nMOS网络,再按互补关系画出对应的pMOS网络。

从以上电路可以看出,互补静态CMOS逻辑的一般形式是AOI逻辑关系,简单的逻辑门可以理解为AOI逻辑门的特例。

图3-5用基本逻辑门实现式2-1需要的晶体管数量

采用AOI逻辑门进行晶体管级设计有较高的晶体管使用效率。

例如,如果使用基本逻辑门实现式2-3的逻辑关系,电路结构将如图3-5,共需要10个晶体管,比图3-4(a)多出4个晶体管。

在全定制设计中,掌握AOI复合逻辑门的设计方法是很重要的。

AOI逻辑门也存在扇入系数的约束,设计AOI逻辑门时,也应避免出现过长的串联支路。

串联晶体管的数量一般以4个为限,复杂的逻辑关系需要采用多级电路实现。

虽然使用AOI逻辑一般比用基本逻辑门设计的电路晶体管数量少,但也不能保证是晶体管最少的设计。

在静态CMOS逻辑中,还存在其它的逻辑系列,其中基于传输门的设计较常用,这种设计方法对许多逻辑关系有最少的晶体管数量。

3.1.4传输门和三态门

单独使用NMOS管或PMOS管作为传输管时,存在“阈值电压损失”问题,用来设计逻辑电路性能较差。

使用传输门设计逻辑电路是较常用的方法。

CMOS传输门的电路结构如图3-6(a),也属于静态逻辑电路,但为了与互补静态逻辑相区分,一般将基于传输门设计的电路称为“传输门逻辑”或“使用传输门的CMOS逻辑”。

图3-6(a)传输门(b)三态门

如果图3-6中的A为输入,B为输出,将控制信号G理解为使能信号,则传输门就是一种三态门。

同图3-6(b)相比,传输门实现的3态门的晶体管数较少,但性能则较差。

这种三态门是无(电平质量)恢复能力(nonrestoring)的电路,当输入A质量下降时,例如高电平电压下降,其输出Y的质量会进一步下降,经过多级相同结构的电路后,可能导致逻辑错误。

当传输门逻辑级联时,传输延迟的增加与串联晶体管问题相似,也会按平方关系增长。

图3-6(b)是一种三态反相器,与基本逻辑门不同,其结构不符合互补关系。

三态门一般用于数据总线,但类似的结构,有时也可用来实现某些特殊的逻辑关系。

3.1.5D锁存器

图3-7是数字电路课程中介绍的D锁存器,逻辑功能是:

当时钟CLK为高电平时,输出(Q)随输入变化,而CLK为低的时候,最后的值被交叉反馈的门(也称为LATCH)保存,输出与输入无关。

由于CLK=1时,中间的逻辑门就像透明一样,因此也称为“透明锁存器”。

图3-7数字电路中的D锁存器

实际集成电路中很少见到结构如图3-7这样的锁存器,因为用了太多的晶体管,共有18个。

图3-8基于传输门的D锁存器

图3-8是比较常见的锁存器结构,其特点是晶体管数量少。

图中有8个晶体管,如果算上产生/CLK的反相器,是10个晶体管,但同时使用多个锁存器时,CLK和/CLK可以集中处理。

这种结构的缺点是传输门不具有电平恢复能力,另外,如果CLK与/CLK有交叠,即瞬间同时为高或同时为低,两个传输门会同时导通,当输入信号D与下面的反相器逻辑相反时,会有较大的瞬时电流。

另一种较常见的结构基于图3-9所示的三态反相器,简称三态门。

图3三态反相器

但EN=0,/EN=1时,上下两个管子都截止,输出即没有连接到VDD,也没有连接到GND,这种状态称为“高阻态”,是除“0”和“1”以外的第3种状态,因此这种门称为“三态门”。

当但EN=1,/EN=0时,上下两个管子都导通,电路的逻辑功能恢复为反相器功能,故称为“三态反相器”。

与传输门相比,“三态反相器”在使能状态下,输出端与VDD或GND是连通的,即使输入电平不好(高电平不够高或低电平不够低),输出电平可以恢复,这是三态门优于传输门之处。

图3-9基于三态门的D锁存器

图3-9是基于三态反相器构成的D锁存器,其原理与图基本相同,如果CLK与/CLK较叠,也会出现两个门的输出端之间的电流。

对于锁存器来说,关键的时序要求(CLK与D变化的先后关系)是在从“透明状态”到“锁存状态”转换,即CLK从1到0变化时,输入数据D必须保持稳定,否则可能锁住错误的数据。

一般来说,当锁存器从锁存状态到透明状态转换时,时序要求不高,因为这时即使输入D还没有稳定,在其后的状态中,锁存器是透明的,数据还是能够正确传输到输出。

3.1.6触发器

集成电路中使用的触发器几乎都是D触发器,其逻辑关系为Qn+1=D。

触发器的特点在于输出Q只能在时钟沿上变化,而当时钟保持在稳定的低电平和高电平时,输出都保持不变。

触发器分为上沿触发和下沿触发两种,图3-10是一个典型的上沿触发的触发器,它可以理解为两个锁存器串联。

图3-10D触发器

在图5中,当CLK=0时,锁存器1是导通的,/QM=/D。

但这时,第2级锁存器处于锁存状态,/QM不能传输到Q。

当CLK有0变为1时,锁存器2“打开”,同时锁存器1“关闭”,CLK上跳前的/QM传递到Q,而输入信号D被锁存器1断开,以后锁存器2是导通的,由于锁存器1处于保持状态,/QM不变,Q也就保持不变。

触发器有两个关键时序参数,一是“建立时间”。

当时钟上跳时,数据D必须已经传递到/QM,否则锁存器1可能锁住了错误数据。

当时钟上跳后,由于传输门有延迟,输入数据D还要暂时保持不变,待最左边的传输门彻底断开后,D再变化就没有关系了。

时钟上跳后,需要D保持不变的时间称为“保持时间”,是另一个关键参数。

一个超大规模集成电路可能有几万个触发器,只要有一个输入信号与时钟之间不满足时序关系就可能出错,因此,时序问题是数字集成电路实现时最关键的问题。

关于时序问题,后续章节及另一门课程还要讨论。

图3-11基于三态门的D触发器

图3-11是混合信号集成电路中经常出现的D触发器结构,其优点还是电平恢复问题。

将最左边的和中间的三态门用传输门替代的结构也比叫常见。

图3-12一种标准单元库中的D触发器

图3-12是一种标准单元库中的触发器,它有一个异步复位端,RB=0时,触发器将强制为0(Q=0),与CLK无关。

注意,它的输出Q和QB都经过反相器缓冲的,这是为了避免过大的负载电容“拖住”第2级锁存器,使其锁存错误的数据。

另外,为从CK获得CKB,它使用了两个反相器,这是为减小在CK端的输入电容,减轻外部时钟信号的负担。

这种设计思想值得学习,设计一个电路不能只考虑电路本身,还要注意对外部的影响。

3.1.7不交叠信号生成电路

图3-13不交叠电路

有时希望产生一对互补的信号,如图3-13中EN和/EN,但不希望它们出现同时为1或同时为0的情况,这种电路称为不交叠信号生成电路。

由于延迟的存在,用普通的反相器对一个信号取反是不能保证不交叠的,必须使用特殊电路结构。

图3-13是一个最简单的不交叠信号生成电路,两个输出Q和/Q是不能同时为1的。

在图3-13中,由于或非门的逻辑关系是“有1就出0”,因此当一个或非门输出1时,在这个1没有变为0之前,另一个是无法变为1的,因此任何状态变化必须从“00”的状态过渡,例如想从“01”变为“10”,中间必须经过“00”,这就避免了“11”状态的出现。

图3-14不交叠电路

为提高可靠性,可以在或非门后接“偶数个反相器”,增加过渡时间。

在图3-14中,假设原来A=0,则门4输出1,门5输出0,门6输出1,门7输出(/Q)0,门1输出1,门2输出0,门3输出(Q)1。

如果现在A由0变为1,门4变为0,门1输出0,由于Q=1,门5输出暂时不能变化,必须等待Q的变化。

因此,接下来,电路状态变化必须经过如下次序:

门2输出1(一个延迟),门3输出0(两个延迟),现在是Q和/Q都为0,接下来门5输出1,然后门6输出0,然后门7输出1。

可见“00”状态约有3个门的延迟时间。

3.1.8施密特触发器

施密特触发器实际上不是触发器,而是一种特殊的“门”,因为它没有保存数据的作用。

与普通门电路相比,施密特触发器有两个阈值电压,而门电路只有一个。

注意这里说的阈值电压是指逻辑门的阈值电压,而不是晶体管的。

施密特触发器在输出电平转换时,有正反馈作用,通常用来对信号进行整形。

图3-15施密特触发器

图3-15是一个典型的施密特触发器。

假设当前状态为A=0,则Y为1。

图3-15

在A=0,Y=1时,N1和N2都是截止的,由于Y的电压为VDD,N3本来可以导通,但没有电流通路(在N2中会有一个相当于反相二极管的漏电流)。

这时N1与N2中间的电压约为VDD-VTHN。

当A点电压升高时到VTHN时,N2可以导通,但N1还不能导通(但VX会下降),因此VA上行时阈值被抬高了。

当VA升高到VTHN+VX时,N2开始导通,导致VY下降,VX下降,加速了N2的导通,出现正反馈。

当A=1时,P1和P2是截止的,Y=0,VY=VTHP。

当VA下降到VDD-VTHP时,P1先导通,P2暂时还不能导通,因此VA下行时,转换阈值被降低了。

施密特触发器的两个阈值电压与P1和P3及N1和N3的尺寸有关,调整N1和N3的宽长比可以调整上行阈值,调整P1和P3的宽长比可以调整下行阈值。

3.1.9窄脉冲生成电路

图3-17窄脉冲生成

静态看,图3-17所示的电路似乎没有作用,Y永远为1。

但由于逻辑门存在延迟,当输入从“0”跳变到“1”时,输出端会产生一个窄的低电平脉冲信号。

这种电路经常用来为触发器复位。

3.2单元电路结构设计

数字单元的结构设计是个晶体管级设计问题,目的是用最少的晶体管实现功能可靠的电路。

晶体管级逻辑优化方法与采用标准逻辑门的逻辑优化有所不同,不是以获得最简逻辑表达式为目的。

目前,还没有总结出通用的晶体管级逻辑优化方法,以下仅以几个典型的设计问题来说明晶体管级逻辑设计的特殊性。

例1.多路选择器设计

多路选择器(Multillexer,MUX)是一种非常重要的单元电路,简单2选1多路选择器的真值表如图3-18。

图3-182选1MUX的逻辑关系

最简的与-或表达式为

(3-5)

最简的与非-与非表达式为

(3-6)

最简与或非表达式

(3-7)

首先考虑使用式3-6进行设计,该表达式对应一个反相器和3个与非门,电路如图3-19。

图3-19基于与非门的MUX2

这种实现方法共需要16个晶体管。

使用式3-7的与或非表达式设计AOI逻辑电路如图3-20,需要14个晶体管。

图3-20AOI逻辑MUX2

图3-20晶体管数量较多的原因是使用了在输入端较多的反相器,这是表达式中反变量过多造成的。

将式3-5修改为

(3-8)

可以减少反变量数量。

根据式3-8,可得到图3-21。

图3-21基于“与或”表达式的MUX2

这种设计方法设计使用了12个晶体管,输出端经反相器驱动,便于调整驱动能力是较好的实现方法。

图3-22是在三态门基础上得到的电路结构,同样使用12个晶体管,结构与图3-21相似,但内部连线少了一条,版图可能更小。

图3-22基于3态门的MUX2

图3-23是基于传输门的设计,晶体管数最少,但属于norestoring电路。

图3-23传输门逻辑的MUX2

例2.全加器设计

全加器的设计也是很典型的例子,图2-13是逻辑符号和真值表。

图2-13全加器的逻辑符号、真值表、卡诺图

全加器的逻辑方程为

(2-)

(2-)

使用门级设计的最好结果是将S表示为

(2-1X)

图2-14一种基于基本逻辑门的设计

尽管进行了逻辑方程化简并借用了CO的中间结果,但图2-14仍然使用了50个晶体管。

而图2-15是目前最流行的设计方法,只用了28个晶体管,而且无论从输入端负载或输出驱动能力的角度看,性能都不低于图2-14。

图2-1528T全加器

注意,28T全加器具有一种特殊的结构,它的P管和N管连接方式是对称的,从电路的各个输出节点,包括中间节点看,nMOS网络和pMOS网络的导通条件也是互为反函数的关系。

2.4晶体管级逻辑设计方法的总结

从以上例子可以看出,晶体管级逻辑设计与基于逻辑门的设计不同,需要依靠对具体的逻辑方程式进行仔细的观察,找出结构特点,才能设计出优化的电路。

不过,从这两个例子中也看出一些规律:

(1)对较复杂的逻辑关系应该考虑先实现其反变量。

理由:

最后的输出要经过一个单独的反相器,便于调整驱动能力,内部晶体管的尺寸也比较小(后续章节讨论)。

(2)中间逻辑整理为AOI表达式,在整体的“非”号下的与-或表达式中,不在单个变量上的“非”要去掉。

理由:

只有单个变量的“与”和“或”关系与晶体管连接可直接对应。

(3)逻辑优化时,尽量减少nMOS网络导通逻辑FN中的反变量个数。

理由:

nMOS网络的反变量需要在输入端加反相器实现。

(4)满足

(2)和(3)的前提下,以与-或表达式中变量出现次数最少为化简准则。

理由:

变量出现一次需要两个晶体管(N、P网络各一个)。

例如,实现全加器进位CO时,首先考虑

,因为

恰好是AOI表达式。

直接用晶体管实现时,FN为

在N网络需要6个晶体管,如果改写为

则

只需要5个晶体管。

然后根据式()整理FP,

=

=

这样就可以设计出28T全加器的CO部分。

28T全加器借用

实现S是一个关键的“妙手”,其它按上述原则还是可以设计出来的。