电子电路EDA技术课程实践试验考试报告书.docx

《电子电路EDA技术课程实践试验考试报告书.docx》由会员分享,可在线阅读,更多相关《电子电路EDA技术课程实践试验考试报告书.docx(11页珍藏版)》请在冰豆网上搜索。

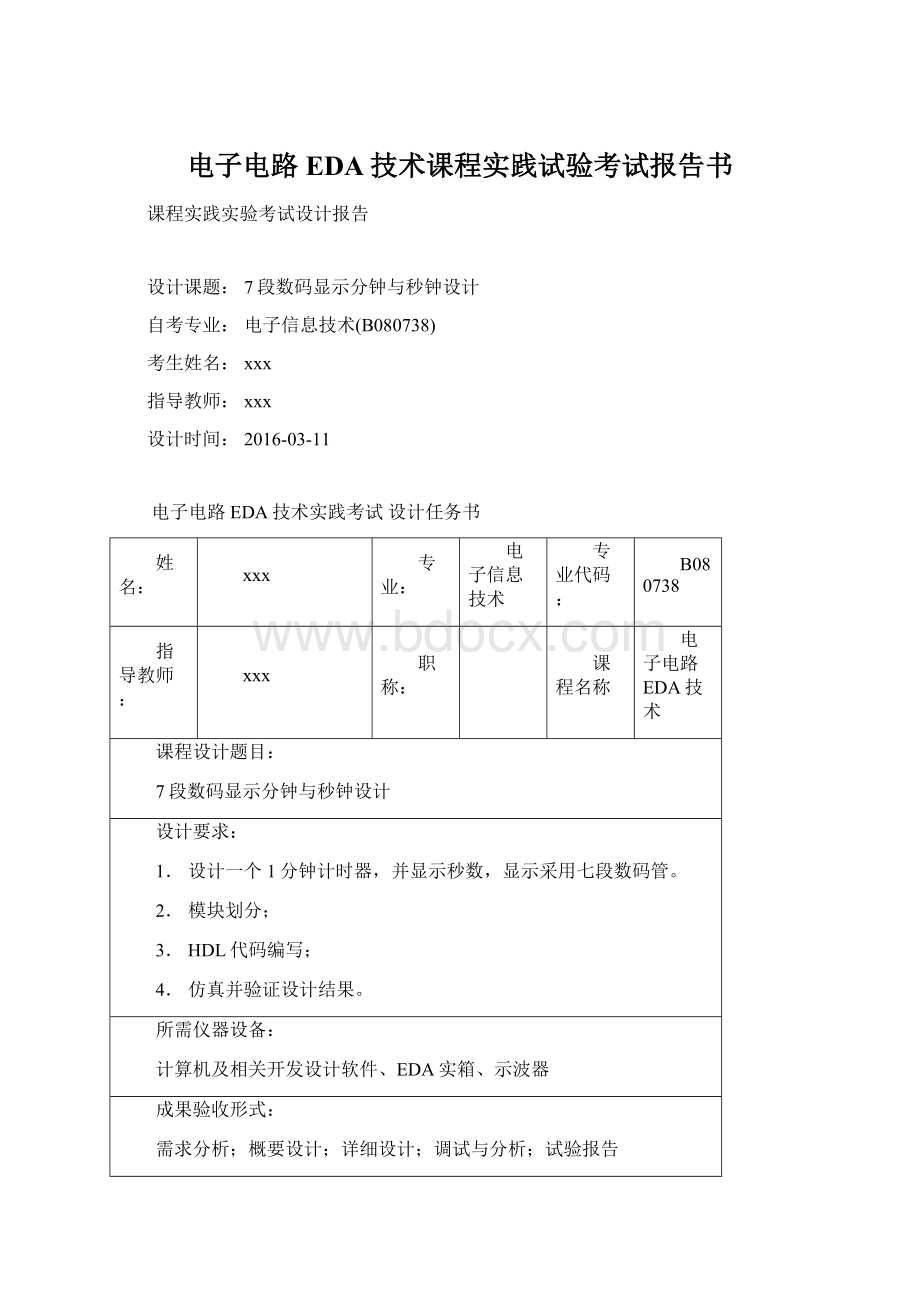

电子电路EDA技术课程实践试验考试报告书

课程实践实验考试设计报告

设计课题:

7段数码显示分钟与秒钟设计

自考专业:

电子信息技术(B080738)

考生姓名:

xxx

指导教师:

xxx

设计时间:

2016-03-11

电子电路EDA技术实践考试设计任务书

姓名:

xxx

专业:

电子信息技术

专业代码:

B080738

指导教师:

xxx

职称:

课程名称

电子电路EDA技术

课程设计题目:

7段数码显示分钟与秒钟设计

设计要求:

1.设计一个1分钟计时器,并显示秒数,显示采用七段数码管。

2.模块划分;

3.HDL代码编写;

4.仿真并验证设计结果。

所需仪器设备:

计算机及相关开发设计软件、EDA实箱、示波器

成果验收形式:

需求分析;概要设计;详细设计;调试与分析;试验报告

参考文献:

1.《基于FPGA的现代数字系统设计》西安电子科技大学出版社2011年版

2.华清远见嵌入式培训中心编<>

时间

安排

2016-3-11

一、总体设计分析

1.1原理分析

分计数器和秒计数器为60进制计数器,采用10进制计数器与6进制计数器组合而成,便于数码管显示设计。

若采用静态扫描显示方式,则4个数码管段选线是独立的,则需要I/O端口较多,占有资源大,且此功耗大。

因此,采用动态扫描显示方式输出。

1.2模块划分

该设计主要由分频器、计数器、动态扫描显示模块、共阴7段数码管译码器组成。

其中分频器设计中,采用有PLL锁相环分频后的200Hz的时钟源,经200分频后为1HZ的秒计数时钟;另外200Hz作为数码管动态扫描等其他所用时钟源;采用太快得时钟动态扫描,数码管显示会有些昏暗;频率太慢人眼睛会看到闪烁。

2个60进制计数器分别作为分计数器和秒计数器。

一个60进制计数器由一个6进制计数器和一个10进制计数器组成,便于四个数码管的显示。

另外,使用一个接口作为数码管复位按键接口;由于是共共阴7段数码管,因此,FPGA输出接口与数码管间需接数码管驱动电路,增强FPGA输出信号的驱动能力。

图1总体设计框图

1.3输入输出端口分配

FPGA分配的与外围电路的接口管脚信号,其中各引脚的功能如下:

引脚

符号

功能说明

1

Rst_n

数码管复位按键接口

2

disp_select

外接数码管阴极动态扫描接口(四根信号)

3

disp_data

译码器输出端,接数码管的阳极(a~g7根信号口,中间需驱动器,四个数码管并联)

二、各模块详细设计与仿真

2.1分频器设计

VerilogHDL代码如下:

(200HZ的动态扫描时钟进行200分频为1HZ计时时钟信号)

moduleClk_Div200(Clk_in,Rst_n,Clk_out);

inputClk_in,Rst_n;

outputregClk_out;

reg[7:

0]Cnt;

always@(posedgeClk_in)begin

if(!

Rst_n)

Cnt<=0;

elseif(Cnt==8'd199)

Cnt<=0;

elseCnt<=Cnt+1'b1;

end

always@(posedgeClk_in)begin

if(!

Rst_n)

Clk_out<=0;

elseif(Cnt==8'd199)

Clk_out<=~Clk_out;

end

endmodule

功能仿真结果如下图:

2.2分钟与秒钟计数设计

采用与十进制计数器与六进制计数器组合而成,一个60进制的计数器。

VerilogHDL代码如下:

moduletime_counter//分钟秒钟计数

(Rst_n,Clk_out,time_bit_high,time_bit_low,EO);

inputClk_out,Rst_n;

outputEO;

output[3:

0]time_bit_high,time_bit_low;

reg[3:

0]time_bit_high,time_bit_low;

regEO;

reglow_to_high;

wireClk_out;

always@(posedgeClk_out)begin//低位计数,到9清零,高位计数使能开启

if(!

Rst_n)begin

time_bit_low<=4'b0;

low_to_high<=1'b0;

end

elseif(time_bit_low<4'b1001)begin

time_bit_low<=time_bit_low+4'b1;

low_to_high<=1'b0;

end

elseif(time_bit_low==4'b1001)begin

low_to_high<=1'b1;

time_bit_low<=4'b0;

end

end

always@(low_to_high)begin

if(!

Rst_n)begin

time_bit_high<=4'b0;

EO<=1'b0;

end

elseif(time_bit_high<4'b0101&&low_to_high==1'b1)begin//高位计数,到5清零,高位计数使能开启

time_bit_high=time_bit_high+4'b1;

EO<=1'b0;

end

elseif(time_bit_high==4'b0101&&low_to_high==1'b1)begin

time_bit_high<=1'b0;

EO<=1'b1;

end

end

endmodule功能仿真结果如下图:

(输入Rst_n复位信号,分秒计数清零。

秒钟计数,低温到9清零后产生高位计数信号low_to_high,高位计数到5后。

对于秒钟计数产生分钟低位开始计数的使能信号EO)

2.3动态扫描模块设计

采用与200Hz的时钟不断刷新显示,利用人眼睛视觉延时特性,动态显示计数结果。

四位共阴数码管动态扫描。

VerilogHDL代码如下:

moduledynamic_scanning//四位共阴数码管动态扫描

(Rst_n,Clk_in,disp_select,

minute_bit_high,minute_bit_low,second_bit_high,second_bit_low);

inputRst_n,Clk_in;

input[3:

0]minute_bit_high,minute_bit_low,second_bit_high,second_bit_low;

output[3:

0]disp_select;

reg[3:

0]disp_select;

wire[3:

0]minute_bit_high,minute_bit_low,second_bit_high,second_bit_low;

reg[1:

0]Cnt;

always@(posedgeClk_in)begin

if(!

Rst_n)

Cnt<=0;

elseif(Cnt==2'b11)

Cnt<=0;

elseCnt<=Cnt+1'b1;

end

always@(posedgeClk_in)begin

case(Cnt)

2'b00:

disp_select<=second_bit_low;

2'b01:

disp_select<=second_bit_high;

2'b10:

disp_select<=minute_bit_low;

2'b11:

disp_select<=minute_bit_high;

default:

disp_select<=4'b1111;

endcase

end

endmodule

2.4数码管译码器设计

对计数器输出的数据,进行译码,生成在七段共阴数码管上能显示0~9的二进制信号。

VerilogHDL代码如下:

moduledisp_decode4_7

(Rst_n,Clk_in,

minute_bit_high,minute_bit_low,second_bit_high,second_bit_low,

select_data,disp_data);

inputRst_n,Clk_in;

input[3:

0]minute_bit_high,minute_bit_low,second_bit_high,second_bit_low;

input[3:

0]select_data;

output[7:

0]disp_data;

wire[3:

0]minute_bit_high,minute_bit_low,second_bit_high,second_bit_low;

reg[7:

0]disp_data;

reg[3:

0]data;

always@(posedgeClk_in)begin

if(Rst_n==1'b1)begin

case(select_data)

4'b1110:

data=second_bit_low;

4'b1101:

data=second_bit_high;

4'b1011:

data=minute_bit_low;

4'b0111:

data=minute_bit_high;

default:

data=4'b1111;

endcase

end

case(data)

4'b0000:

disp_data<=7'b1111110;

4'b0001:

disp_data<=7'b0110000;

4'b0010:

disp_data<=7'b1101101;

4'b0011:

disp_data<=7'b1111001;

4'b0100:

disp_data<=7'b0110011;

4'b0101:

disp_data<=7'b1011011;

4'b0110:

disp_data<=7'b1011111;

4'b0111:

disp_data<=7'b1110000;

4'b1000:

disp_data<=7'b1111111;

4'b1001:

disp_data<=7'b1111011;

default:

disp_data<=7'b0;

endcase

end

endmodule

2.5顶层模块设计

对以上各个功能模块例化,设计顶层文件,完成最终VerilogHDL设计。

VerilogHDL代码如下:

moduledisp_minute_second_top(Rst_n,Clk_in,disp_select,disp_data);

inputClk_in,Rst_n;

output[3:

0]disp_select;

output[6:

0]disp_data;

wireClk_out,EO;

wire[3:

0]disp_select;

wire[3:

0]minute_bit_high,minute_bit_low,second_bit_high,second_bit_low;

wire[3:

0]select_data;

Clk_Div200U_Clk_Div200(

.Rst_n(Rst_n),

.Clk_in(Clk_in),

.Clk_out(Clk_out));

time_counterU_second_counter(

.Rst_n(Rst_n),

.Clk_out(Clk_out),

.time_bit_high(second_bit_high),

.time_bit_low(second_bit_low),

.EO(EO));

time_counterU_minute_counter(

.Rst_n(Rst_n),

.Clk_out(Clk_out),

.time_bit_high(minute_bit_high),

.time_bit_low(minute_bit_low),

.EO());

dynamic_scanningU_dynamic_scanning(

.Rst_n(Rst_n),

.Clk_in(Clk_in),

.disp_select(disp_select),

.minute_bit_high(minute_bit_high),

.minute_bit_low(minute_bit_low),

.second_bit_high(second_bit_high),

.second_bit_low(second_bit_low));

disp_decode4_7U_disp_decode4_7(

.Rst_n(Rst_n),

.Clk_in(Clk_in),

.minute_bit_high(minute_bit_high),

.minute_bit_low(minute_bit_low),

.second_bit_high(second_bit_high),

.second_bit_low(second_bit_low),

.select_data(disp_select),

.disp_data(disp_data));

Endmodule

三、综合仿真测试

对工程设计文件综合,RTL视图如下:

然后进行时序分析与时序仿真。

数码管复位信号为低时,计时器复位清零。

四、分析与总结

1.自顶向下的设计方法利用功能分割手段将设计由上到下进行层次话和模块化,及分层次、分模块进行设计和仿真。

功能分割时,将系统功能分解为功能块,功能块再分解为逻辑块,逻辑块再分解为更少的逻辑块和电路。

如此分割,逐步的将系统细化,将功能逐步的具体化,模块化。

高层次设计进行功能和接口描述,说明模块的功能和接口,模块功能的更详细描述在下一设计层次说明,最底层的设计才涉及具体寄存器和逻辑门电路等实现方式的描述

2.采用动态扫描显示方式输出:

4个LED显示,将所有的段选线并联接至一共阴7段数码管译码器输出端,阳极接位选控制线,实现各位分时选通。

共用一个译码器,这样节约FPGA的硬件资源。

每一位显示时间间隔不内能超过20ms,否则会闪烁。

3.在学习的过程中,通过结合书本理论知识及课后实验练习,熟悉了EDA开发软件的使用及VerilogHDL语言,一分钟计时器可以说是书本上课后实验的演变,在熟练教材原理知识和实验的基础上进行此实验相对来说更容易一些。

遇到的问题主要就是,在进行原理图设计时,定时器原件块和多路选择器原件块输出、输入接错了,导致波形仿真失败,还有对VerilogHDL语言逻辑不太熟练,通过实验,自己学会了原理图设计法、文本输入设计法,同时也感受到了自顶而下和自下而上设计思路的优势。

4.感谢指导老师耐心的指导,希望有更多机会接受老师的现场指导.

五、附件

电子电路EDA技术实践考试课程设计成绩评定表

专业:

电子信息技术代码:

B080738学号:

06990820xxx姓名:

xxx

课题名称

7段数码显示分钟与秒钟设计

设计任务与要求

1.设计一个1分钟计时器,并显示秒数,显示采用七段数码管。

2.模块划分;

3.HDL代码编写;

4.仿真并验证设计结果。

指导教师评语

建议成绩:

指导教师:

课程小组评定

评定成绩:

课程负责人:

年月日