主动器件的特性与应用上.docx

《主动器件的特性与应用上.docx》由会员分享,可在线阅读,更多相关《主动器件的特性与应用上.docx(29页珍藏版)》请在冰豆网上搜索。

主动器件的特性与应用上

主动器件的特性与应用(上)

宇量

内容标题导览:

│切换大负载的电路│切换直流电源的电路│全波整流平顺电路│波动滤波电路│

二极管、晶体管、FET等主动电子器件已经成为各种电子电路不可或缺的器件,因此本文整合常用半导体器件深入探讨应用电路特性。

切换大负载的电路

.可以控制大负载电流ON/OFF的电路

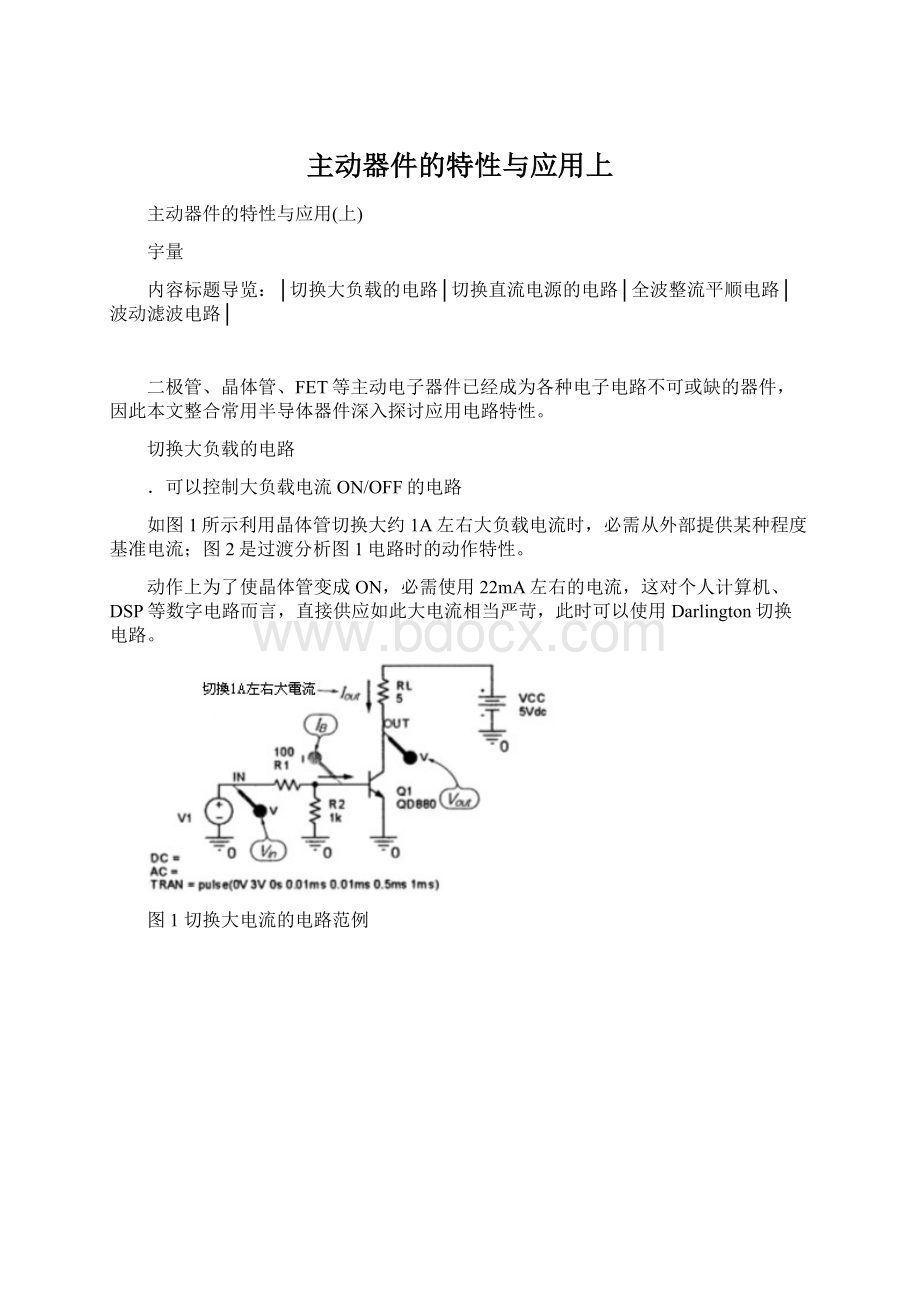

如图1所示利用晶体管切换大约1A左右大负载电流时,必需从外部提供某种程度基准电流;图2是过渡分析图1电路时的动作特性。

动作上为了使晶体管变成ON,必需使用22mA左右的电流,这对个人计算机、DSP等数字电路而言,直接供应如此大电流相当严苛,此时可以使用Darlington切换电路。

图1切换大电流的电路范例

图2图1的基准电流与输出入电压的波形

.巨大电流增幅率的Darlington电路

图3的电路与图1一样都是驱动负载的Darlington切换电路,由图可知它是在驱动负载的晶体管前面插入晶体管,的Emitter再连接于的Base。

本电路为了纪念原创者Dr.SidneyDarlington,因此称为Darlington电路。

图3Darlington电路范例

图4后段晶体管Q2的Collector电流1C2可用下式表示:

1C2

hFE1xhFE2x1B1------------------

(1)

如果Q1与Q2都是同等级晶体管时hFE=hFE1xhFE2,其结果变成非常大,这也是本电路可以用很小的基准电流控制大Collector电流主要原因,此时必需注意Q1的基准(Base)一直到Q2Emitter为止的电压会变成1/VBE2(大约是1.2V左右),而且随着晶体管种类与基准电流值的不同,有可能变成1.6V。

图4Darlington电路的流动电流

图5是Q1的基准电流1B1动作波形,VIN=3V时亦即Q1与Q2ON时,1B1=650µA,此时即使与图1一样驱动负载,从外部提供的基准电流会变得非常小。

图5DarlingtonSwitch的基准电流波形

图6是Q2Collector电位VOUT的动作波形,VIN=3V时VOUT

0V,因此它可以用很小的基准电流精确使大电流作ON/OFF切换。

图6图3电路的输出入电压波形

实际上图6的Q2变成ON时,VOUT却不会成为0V(大约是0.1V左右),造成该现象主要原因是晶体管ON时,Collector与Emitter之间有残留阻抗成份,加上此处有Collector电流流动使得电压降低(该电压又称为Collector-Emitter饱和压称VCE(sat))。

不过不像几乎呈一定值,它会随着晶体管种类与Collector电流改变,此时需注意值,因为它是造成晶体管发热主要原因。

晶体管ON时晶体管内的电力损失Pc如下:

Pc=VCE(sat)x1c----------------------

(2)

由于Pc变成热能后会从晶体管散逸,因此切换电流极大时必需注意发晶体管热问题。

图7的晶体管是在相同封装内将2晶体管作Darlington连接;图8是2个晶体管连接至Darlington晶体管,依此制造成仿真分析用切换(Switching)电路,图中的Q2残留电压非常大,因此必需注意晶体管ON时Collector与Emitter之间产生的电压引发的发热问题。

图7Darlington晶体管的结构

图8Darlington晶体管的动作原理

图9是图8电路的VOUT动作波形,由图可知Q2变成ON时会产生大约0.77V左右的残留电压,此时若改用Darlington晶体管的话,残留电压最低只有0.6V,主要原因是Q2的Collector若不比Emitter高一个VBE(

0.6V),Q1的Base-Collector之间的二极管就会变成ON,如此一来Q1就无法发挥晶体管特性正常动作。

基于上述该电位关系因此必需设法使本电路取得平衡,此外VCE(sat)外观上看似变大,不过切换大电流时还是需要注意晶体管的发热问题。

图9图7Darlington晶体管发生残留电压

切换直流电源的电路

.使用晶体管的电路

如图10所示本负载切换电路可以从逻辑电路以控制信号切换提供负载电源,由于切换正电源时高电位电源端设有切换器件,因此本电路又称为HighSideSwitch。

动作上电路中的控制信号VOUT一旦变成"H",就会依照Q2→Q1顺序ON提供电源电压VCC至负载端。

图10可以使连接VCC与负载RL的电源线ON/OFF的LoadSwitch电路

图11是图10电路的动作波形,由图可知VOUT变成OV/4.77V,它可以用0V/3V的逻辑信号,ON/OFF提供负载端的电源。

Q1ON时VOUT无达到5V,主要原因是Q1的VCE(sat)发生0.23V的电压损失,如果改用低VCE(sat)的晶体管就可以降低电压损失,除此之外Q1还会产生VCE(sat)1L的电压损失。

图11图10的控制电压与电压波形

.使用MOSFET的电路

图12是MOSFETIC构成的负载切换(LoadSwitch)电路,由于MOSFETIC的Gate不需流通电流,所以R1~R3的阻抗值可以设得非常高。

图13是图12电路的动作波形,它与图10的电路一样,可以用0V/3V的逻辑信号在电源与负载之间作5V的切换。

MOSFETICON时Drain与Source之间的残留电压VDS(on)只有0.06V非常小,主要原因是MOSFETICON时,Drain与Source之间的阻抗成份RDS(on),会因为Drain流动产生电压下降所致。

Q1如式

(2)所示会产生VDS(on)1D的电力损失,此时若欲降低VDS(on)只需改用低RDS(on)器件即可。

图12使用MOSFET的LoadSwitch电路

图13图12电路的控制电压与输出电压波形

全波整流平顺电路

.附中间Tap变压器+2个二极管的整流电路

图14全波整流交流-直流转换电路是由变压器中间Tap构成,基本上它是组合中间Tap变压器与2个二极管,再以半波整流电路的2倍频率提供电容器充电电流,亦即所谓的全波整流电路。

图15的测试电路是为了进行仿真分析,刻意将变压器附中间Tap2次端卷线更换成2个万能电压源VSRC。

图14附中间Tap变压器+2个二极体的全波整流平顺电路

图15以电压源代用晶体管可作仿真分析的电路

图16是将V1,V2分别设定成5Vpeak,50V的正弦波,接着以过渡分析模拟0~40ms范围时图15电路各部位的动作波形,由图可知Vinput1比Voutput高0.8V时D1变成ON,Vinput2比Voutput高0.8V时D2变成ON,D1与D2交互ON/OFF,如此就可以在输出信号1周期内使电容2次充电,Voutput的波动(Ripple)频率是半波整流电路的2倍,以本分析模拟为例它的输入频率是50Hz,因此波动电压的波动频率相当于:

50Hz×2=100Hz。

图16图15电路的电压、电流波形

图17是图15电路的各二极管电流动作波形,如图所示D1的电流ID1波形与D2的电流ID2波形交互出现峰值(Peak),因此D1与D2交互ON,图中ID1与ID2的峰值部份几乎都是为了使电容充电的电流,D1与D2OFF期间,C1的放电电流则提供给负载端。

图18是综合以上动作特性获得的结果,如图所示本电路会依照(a)~(d)顺序反复动作。

图17图15电路中各二极管的电流波形

图18图15电路的电流流动方式

全波整流交流-直流转换电路若与半波整流构成的电路比较时,由于电容放电时间变短(电容充电频率变成2倍所致),因此即使使用相同容量的电容,Voutput的波动电压会变小。

如下式所示使用全波整流电路时Voutput波动电压ΔV只有半波整流电路的1/2,因此上述图16的波动电压,大约是半波整流电路的1/2左右。

IRL

ΔV=――――――-----------------------(3)

2finCF

IRL:

负载电流(A)。

fin:

输入信号的频率(Hz)。

CF:

平顺电容的容量(F)。

‧无中间Tap变压器+4个二极管的整流电路

图19的交流-直流转换电路,是由二极管作架桥连接的全波整流电路与平顺电路组合构成,虽然图14也是全波整流电路,不过变压器的绕线相当复杂,成本上图19的电路比较有利,所以目前二极管架桥连接构成的全波整流电路经常被应用在各种电子产品。

仿真分析图19电路时必需注意V1电压振幅的读取方法,如果V1的一端有接地的话,直接使用可以显示GND电位的电压Marker量测即可,不过观察类似图19这种从GND漂出的电位时,就需改用可以显示两点之间差电压的差电压Marker,此处只量测图19的Vinput±。

图19附中间Tap变压器与4个晶体管构成低成本全波整流平顺电路

图20是利用过渡分析法仿真分析图19电路0~40ms范围时,获得的各部位的动作波形,由于图19的充电电流通过2个串联二极管,所以Voutput比Vinput±低2VF1.6V,加上本电路属于全波整流电路,因此Voutput的波动是输入信号2倍频率,至于Voutput的波动电压可以利用式(3)计算。

图19如果与图16、图比较,它的波动电压值几乎完全相同。

图20图19电路各部位的动作波形

图21是图19电路内的4个二极管的电流动作波形,图中ID1,ID4为D1,D4的电流,ID2,ID3为D2,D3的电流,由图可知ID1,ID4与ID2,ID3即使是相同的时序(Timing)也会逐渐变大,所以D1,D4与D2,D3可以同时ON/OFF,所有二极管OFF期间,电容器的放电电流提供给负载端。

图21图19电路的4个二极管内流动的电流波形

图22是综合以上动作特性获得的结果,如图所示本电路会依照(a)~(d)顺序反复动作,由于(a)与(c)的期间流至电容器的充电电流通过2个串联二极管,所以电容器两端的电压,亦即输出电压比电压输入电压低2个VF。

图22图19全波整流电路的电流流动方式

波动滤波电路

图23是输出正电压的波动滤波(RippleFilter)电路,由于设计上本电路是以电源电路应用为前提,因此输入单元内设有全波整流电路。

本电路是将LowPassFilter连接至称为EmitterFollower晶体管电路的Base上,图中的R2为防止振荡的电阻,C3电容器可以降低高频领域输出阻抗(Impedance)。

图23正电压波动滤波电路

接着按照图24的窗口将图23的电路设定成过渡分析模式进行仿真分析;图25是分析后各部位的电压波形,由图25可知虽然Vin已经乘上整流电路的波动值408mVp-p,不过Vout却已去除波动只剩下直流成份。

图24图23的过渡分析设定

图25图23电路各部位的电压波形

图23电路的Q1Base内设置由R1,C2构成遮断频率极低的LowPassFilter是本电路的主要特征,该LowPassFilter除了可以去除Vin的波动成份之外,还可以提供变压器Base直流成份。

如果仔细观察图25变压器的Base电位VB(Q1),可以发现波动已经被去除,造成VB(Q1)直流电位比VBE更低的原因,是因为Q1Base电流IB通过R1,导致R1IB的电压下降所致。

由于NPN晶体管的Emitter始终Trace比Base低的电位VBE,所以Vout设定成比Base低的电位VBE,至于Base的电位VB(Q1)已经去除波动只剩直流成份,所以Vout也变成直流成份,此外Vout与VB(Q1)的站立非常缓和,主要原因是C2必需通过R1才能充电所致。

图26是图25的波形时间轴与电压轴放大图,图中的Vout残留5.5mVp-p的波动,Vin的波动只有408mVp-p,依此推算确认图23的电路已经去除37.4dB[

20log(408mVp-p/5.5mVp-p],此处为了更进一步降低残留波动,因此刻意将R1,C2的LowPassFilter时定数R1,C2加大。

图26图25的Vout波形放大图

图27将是图23的C2设成220µF,LowPassFilter的时定数设成2.2倍时Vout的动作波形,分析时间延长到2s,不过实际上只显示1.96~2.0s之间的动作特性,若与图26比较,图27的波动只有1/2.2倍。

图27确认图23的C2二倍后的波动电压波形

虽然波动滤波电路可以抑制波动,却无法使输入定电压化,因此输出电压会随着提供至负载端的电流与输入电压变动。

图28是以200Ω负载阻抗降低提供给负载端电流时的动作波形,如图所示Vout从5.09V提高到5.4V,由此可知负载电流或是Q1的基准电流变小,可以有效减缓的电压下降。

图29是图23电路的输入电压V1振幅9Vpeak时是动作波形。

图25的V1为8Vpeak,由图29可知Vout高1V左右,波动滤波电路的输出电压也随着输入电压变化,Vout的上升大约是0.87V(=5.96V-5.09V),亦即的上升低于1V,主要原因是随着Vout的上升给负载端的供给电流变大所造成,R1的电压下降相对变大,输出电压则稍为降低。

图28提高图23负载阻抗RL的仿真分析

图29提高图23输入电压V1的仿真分析

主动器件的特性与应用(下)

宇量

内容标题导览:

│低噪讯定电压电源│定电流电路│Limiter电路│结语│

低噪讯定电压电源

接着要介绍由晶体管与定电压二极管组合构成的简易式定电压电源,虽然简易式定电压电源的输出电压精度或变动率等特性都不如三端子比较器(Regulator),不过电路结构单纯而且输出噪讯很低,所以广泛应用在要求低噪讯特性的模拟电路简易电源。

图30是正电压简易定电压电源电路,它是把定电压二极管连接到波动滤波电路。

图中与定电压二极管并联连接的C2,可以吸收定电压二极管产生的噪讯(Noise);图31是图30定电压电路各部位的电压动作波形,过渡分析的设定与上述图24相同,由图31可知Q1的基准电位VB(Q1)变成5.5V直流一定值,它是定电压二极管D2的两端产生的电压。

输出电压Vout设定成比VB(Q1)更低的VBE,本电路成为4.97V直流一定值。

图30正电压的简易定电压电源电路

图31图30的定电压电路各部位电压波形

图32是图30整流电路的输入电压V1变成9Vpeak时,各部位的电压动作波形,由图显示随着V1变高,电路的输入电压Vin(=整流电路的输出)也会提高,不过Vout=4.8V与V1=8Vpeak时,输入电压几乎没有任何变化。

Vin一旦变高施加于R1两端的电压(Vin-VB(Q1))也随着提高,D2内的电流则变大,然而定电压二极管两端产生的电压,几乎与流动电流无关成为一定值,因此基准电位VB(Q1)与Vout几乎没有任何变化。

图33图30输出电压的波动波形

图34是负极设置Marker观察ID2获得的动作波形,图中的ID2是R1内流动的电流IR1扣除Q1基准电流的结果,R1两端的电压变成Vin-VB(Q1),由于Vin的波动呈直接加入状,因此IR1出现波动,ID2也跟着出现类似图34的波动波形。

虽然理想定电压二极管两端的电压与流动电流无关成为一定值,然而实际上器件两端的电压却与流动电流成比例作mV等级变化,所以VB(Q1)(D2的两端电压)会产生与Vin波动成比例作mV等级的电压变化,最后该电压变化直接出现在Vout,此时LowPassFilter插入Q1的Base,由于它的动作特性与波动滤波电路一样,所以可以有效抑制Vout的波动。

图35是将C2设定成330µF同时加大R1与C2,依此构成LowPassFilter的时定数。

图34Zener二极管的电流波形

图35低波动的定电压电路

图36是C2=330µF时Vout的波动成份,如图所示残留波动降至4.8mVP-P,证实加大C2可以同时获得定电压与低波动特性,此处必需注意的是加大C2后C2的充电时间相对变长(图37)。

图36提高图30C2时的输出电压波动电压波形

图37提高C2时的起动特性模拟分析

定电流电路

.吸入型定电流电路

定电流电路与连接负载的阻抗无关,它可以输出一定的电流,因此广泛应用在LED点灯电路与OP增幅IC等领域。

图38是由晶体管构成可以输出吸入方向电流的定电流电路,电路结构属于无输入端子Emitter共通增幅电路。

本电路的输出端子Q1为Collector,负载则连接至比Q1的Emitter更高电位,亦即电源与输出端子之间。

图38吸入型定电流电路

图39是决定输出电流的方法,由图可知晶体管的基准电位VB由VCC,R1,R2决定,它会变成直流一定值,Emitter的电位流VE则设定成流VB-VBE,因此VE也成成一定值,Emitter的电流IE可用下式表示:

由式(4)可知IE同样也会变成直流一定值,如果忽略基准电流的话,Collector电流等同于Emitter电流,由于输出电流Iout=IE,因此Iout与RL值或是VLOAD值无关成为直流一定值。

图39Collector电流Iout变成一定的动作机制Iout(=IE)由VE,RE决定,

RE为阻抗值不会变化,因此VE与VBE,VB都是属于定电源的差分

图40是将连接负载的电源VLOAD,利用DC分析2~10V范围内变化时各部位的电压与电流动作波形(RL=100Ω),由图可知输出电流与VLOAD值无关,Iout成为0.95mA(≒0.96V/1kΩ)一定值,输出电流完全不受连接负载的影响。

图41是利用DC分析使负载阻抗在10Ω~1kΩ范围内变化时的各部位的输出电流特性,如图显示即使负载值改变,Iout几乎是一定值完全不受连接负载的影响。

图40改变图38的负载电压时各部位的电压与电流

图41改变图38的负载电压时各部位的输出电流特性

.吐出型定电流电路

图42是由晶体管构成可以输出吐出方向电流的定电流电路,由于电流的流动方向与吸入型相反所以使用PNP型晶体管,负载连接于比晶体管的Emitter更低电位,亦即电源与输出端子之间。

图42电流Source型定电流电路

图43是利用DC分析VLOAD在2~10V范围内变化时各输出电流的动作特性,由图可知输出电流完全不受连接负载的影响,可以几乎输出一定值的电流,输出电流为2.1mA它是与VLOAD值无关,Iout成为0.94mA一定值,证实图42的电路可以达成预期的定电流特性。

图43改变图42的负载电压时各部位的电压、电流特性

.JFET型定电流电路

上述由晶体管构成的定电流电路,Base偏压(Bias)时必需使用电源或是电阻,如果是JFET型定电流电路就可以省略这些器件,电路变得非常简洁。

图44是N通道(Channel)JFET构成的电流SinkType定电流电路,本电路只需将JFET的Gate连接至Source,再将负载连接至比Source电位更高的电源即可。

由于电路的输出电路取决于JFET特性,如果对Drain-Source之间施加某种程度大电压的话,JFET的Drain电流ID就可用Drain-Source之间电压决定。

如上所述由于本电路的Gate连接至Source,由于VGS=0V因此此ID是由传达特性Curve上VGS=0V的PointIDSS决定,必需注意的是同等级的JFET它的IDSS分布非常大,所以图44定电流电路的输出电流精度比晶体管型定电流电路差。

图44使用JFET的电流Sink型定电流电路

图45是利用DC分析VLOAD在2~10V范围内变化时,输出电流Iout的动作特性,由图可知它与连接负载的电源电压值无关,可以输出一定值的电流。

输出电流为2.1mA它是根据经过模拟分析的JFET特性设定。

图46是利用DC分析负载阻抗RL在10~1kΩ范围内变化时,输出电流Iout的动作特性,由图可知它Iout同样与RL无关可以输出一定值的电流。

图45改变图44的负载电压时时的输出电流特性

图46改变图44的负载阻抗时的输出电流特性

如图47所示若将串联电阻RS插入Source,可以使输出电流从朝IDSS朝低方向调整;图48是利用DC分析VLOAD变化时的输出电流Iout动作特性,由图可知若插入RS可以将Iout设定成1.06mA,至于RS值则可用JFET传达特性坐标决定,具体步骤首先读取坐标上欲设定Drain电流ID时的Gate-Source之间电压值VGS接着根据设定RS:

图47的电路希望设定成Iout

1mA,根据图49的JFET传达特性坐标决定RS为390Ω(=0.4V/1mA),由于JFET的传达特性本身分布非常大,因此从定电流电路流入电阻的的输出电流分布也很大。

图47可以调整输出电流的JFET定电流电路

图48改变图47的负载阻抗时的输出电流特性

图49根据JFET传达特性坐标求取插入的Source电阻RS值

电流Source型定电流电路

晶体管构成的定电流电路必需固定基准电位,所以电流Sink型与电流Source型定电流电路通常都会使用NPN与PNP型。

由于图44与图47的电路只要针对Source固定Gate电位即可,不需要针对GND、电源固定,所以可以利用N通道JFET制作电流Source型定电流电路。

图50是典型N通道JFET构成的电流Source型定电流电路,图中的Drain连接电源,Source设有串联电阻RS,连接Gate的点当作输出端子;图51是改变VLOAD时的IoutDC分析结果,由图可知本电路具备定电流电路动作特性。

图50使用JFET的电流Source型定电流电路

图51改变负载阻电压时的输出电流特性

Limiter电路

图52的电路可以保护OP增幅IC内部的输入端子;图53Limiter电路可以限制超过±0.6V范围的振幅信号,输出端子与GND之间2个二极管逆向并联连接是本电路主要特征;图54是利用DC法分析0~2ms范围内变化时的动作波形,输入电压Vinput超过+0.6V时D2变成ON,输出电压Voutput固定成≒+0.6V,输入电压Vinput低于-0.6V时D1变成ON,输出电压Voutput固定成≒-0.6V,其结果使得+0.6V范围的输入信号直接输出,超过该范围的信号则被去除。

图52OP增幅IC输入单元使用的Limiter电路

图53±0.6VLimiter电路

图54图53电路的动作波形

图55的电路可以保护数字IC内部的输入端子,如图56所示本Limiter电路只让某范围的信号通过窗口,如果输入电压Vinput超过+0.6V时D1变成ON,输出电压Voutput固定VP+0.6V;输入电压Vinput低于VN-0.6V是D2变成ON,