3篇2章习题解答docx.docx

《3篇2章习题解答docx.docx》由会员分享,可在线阅读,更多相关《3篇2章习题解答docx.docx(12页珍藏版)》请在冰豆网上搜索。

3篇2章习题解答docx

第三篇第2章习题

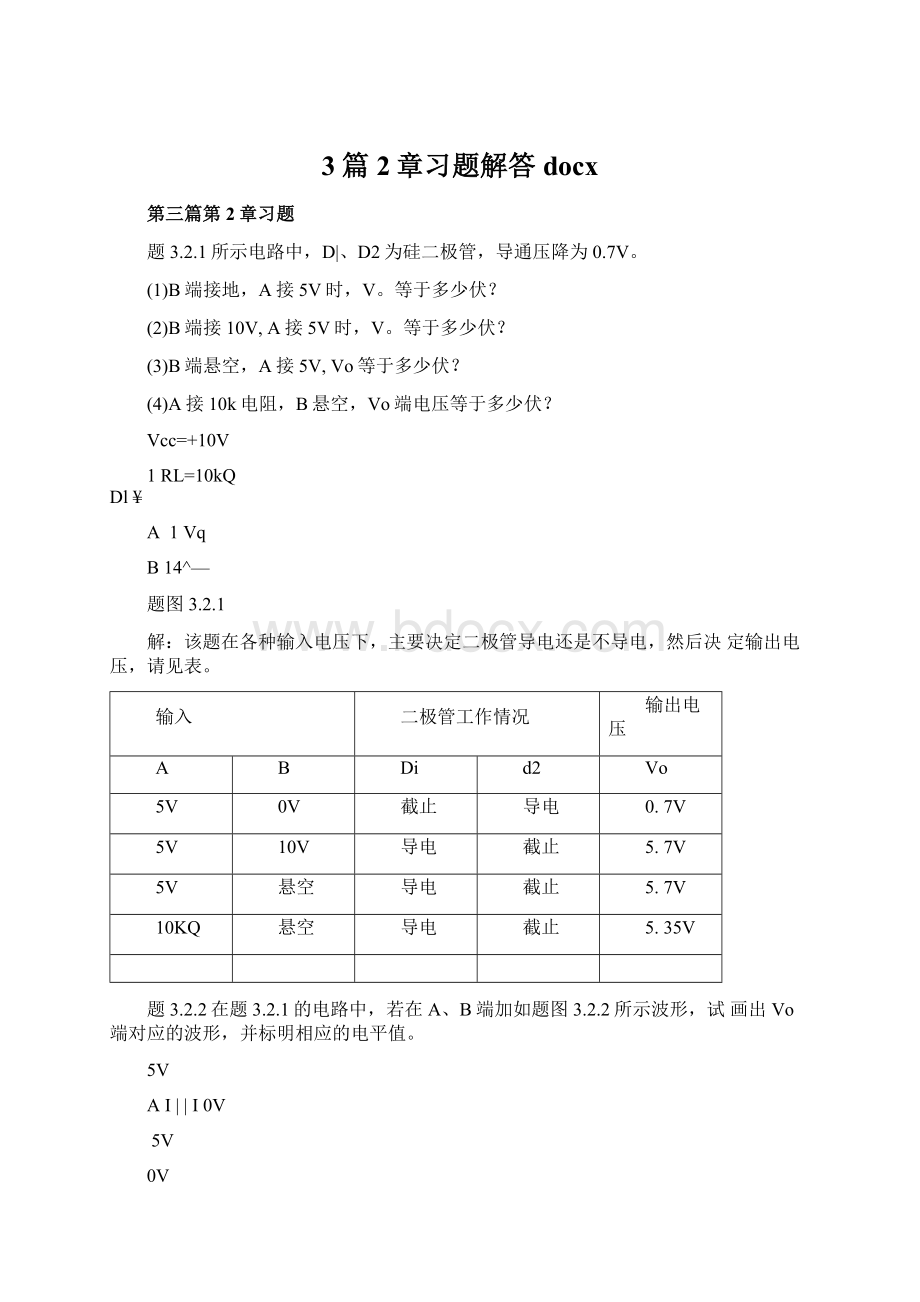

题3.2.1所示电路中,D|、D2为硅二极管,导通压降为0.7V。

(1)B端接地,A接5V时,V。

等于多少伏?

(2)B端接10V,A接5V时,V。

等于多少伏?

(3)B端悬空,A接5V,Vo等于多少伏?

(4)A接10k电阻,B悬空,Vo端电压等于多少伏?

Vcc=+10V

1RL=10kQ

Dl¥

A1Vq

B14^—

题图3.2.1

解:

该题在各种输入电压下,主要决定二极管导电还是不导电,然后决定输出电压,请见表。

输入

二极管工作情况

输出电压

A

B

Di

d2

Vo

5V

0V

截止

导电

0.7V

5V

10V

导电

截止

5.7V

5V

悬空

导电

截止

5.7V

10KQ

悬空

导电

截止

5.35V

题3.2.2在题3.2.1的电路中,若在A、B端加如题图3.2.2所示波形,试画出Vo端对应的波形,并标明相应的电平值。

5V

AI||I0V

5V

0V

题图3.2.2

解:

根据电路图,电路是一个“与”逻辑功能,当加上二极管导电后的压降,则输出高电平为5.7V,输出低电平时为0.7V电压。

所以波形图如图所示:

5V

ov

ov

a「\r

!

L——5V,

—_|I\*I~h

1I5.7V'1

nj

题3.2.3试写出题图3.2.3所示逻辑电路的输出函数Yi及丫2表达式,并画出相应的逻辑图形符号。

解:

这是一个射极耦合逻辑门电路(ECL),Ti和T2的集电极和A、B间是或非逻辑关系,T3集电极和A、B间构成或逻辑关系,而T4和T5是射极输出,所以:

Yi输出是或逻辑关系,丫2是或非逻辑关系。

Y,=A+B,

y2=a+b,其逻辑符号为:

题3.2.4已知TTL反相器的电压参数为Vof芦0.8V,V°h=3V,Vth=1.4V,Von=1.8V,Vn=03V,Vcc=5V,试计算其高电平输入信号噪声容限Vnh和低电平输入信号噪声容限VNLo

解:

低电平输入信号噪声容限:

咋澹1%—4=0.8-0.3=0.5V

高电平输入噪声容限:

Vnh"暗-VIH=V0H-VOn=3.0-1.8=1.27

题3.2.5TTL门电路如题图3.2.5所示,已知门电路参数Iih/Iil=25uA/—1.5mA,Ioh/Iol=-500uA/12mA。

(1)求门电路的扇出系数No;

(2)若电路中的扇入系数N为4,则扇出系数No又应为多少?

T1?

解:

(1)低电平输出扇出系数:

Nol=—|v==4

IIL1.5x2

高电平输出扇出系数:

Noh=Fv=划、=10

IIH25x2

扇出系数为N0=4(个门)

(2)如果门的扇入为4,贝U低电平和高电平扇出分别为2和5个同类门。

扇出系数为N0=2(个门)

题3.2.6TTL门电路如题图3.2.6所示。

已知门的参数

Voh/V°l=3.6V/0.1V,VIHminA^ILmax=2.8V/0.4V,IIH/IiL=20uA/-10mAo为了实现图示的逻辑关系,试确定电阻R取值范围。

题图3.2.6

解:

这是一个门与门之间的驱动问题,前一级门的输出高电平必须大于后级输入高电平最小值,前级的输出低电平必须低于后级门的输入低电平

36V-28V

最大值,因此:

R<=20Q:

40/76?

而前级门的输出电流应该满足后级门的灌拉电流要求。

题3.2.7TTL门电路如题图3.2.7所示,已知门的参数

Voh/VOl=3.6V/0.1V,VIHmin/VILmax=2.8V/0.4V,IIH/IIL=40uA/-10mA,

Ioh/Iol=-500uA/12inAo为了实现图示逻辑关系,试确定电阻R取值范围。

题图3.2.7

解:

因为电路是直接连接到下一级,所以前级的输出电平符合后级的要求,只要考虑前级的输出电流保证能驱动后级即行。

当拉电流负载时,电阻R上只允许流过电流

2Q

。

=500—2x40〃=420必,所以电阻应小于:

R<—=6.67/TQ;而

灌电流负载时可以不考虑。

题3.2.8与非门组成如题图3.2.8所示电路。

输入为方波。

(1)若不考虑门的平均传输时间,试画出输出V。

的波形。

(2)若门的平均传输时间为tpd,且相等,试画出输出V,o和V。

的波

形。

题图3.2.8

解:

(1)不计平均传输延迟时间时的波形:

(2)当考虑门的传输延时的波形:

RJLTLTLT

UrUTLTLTL

题3.2.9试对题图3.2.9所示两种TTL门电路,画出它们在所示A、B、C等输入信号作用下的输出波形。

题图3.2.9

解:

第一个图是一个与门电路,第二个电路是一个三态输出的异或非门电路,电路中用箭头表示输入电平极性,低电平输入,低电平输出。

=A+B=AB

L2=A©5,C=0

L2=高阻态,C=1

B-rnI*:

jLT-LT

l】口口L

bIiru__LT

'II

c

!

|iii

"局阻态---E-局阻态-

题3.2.10题图3.2.10是两个用74系列门电路驱动发光二极管的电路,要求Vi=Vih或Vi=Vil时发光二极管D导通并发光。

已知发光二极管的导通电流为10mA,试问应选用(a)、(b)中的哪一个电路?

请说明理由。

(a)(b)

题图3.2.10

解:

从原理上讲,二种驱动电路都可以,但是从门电路的拉电流和灌电流能力讲,因拉电流能力弱,门电路提供不出10mA电流,灌电流能力强,所以应该是(a)电流驱动。

题3.2.11在题图3.2.11所示由两反相器输出端相接构成的逻辑电器中,若它们的输入A、B是相互交替地为逻辑1、0,并驱动管子为为饱和导电,则晶体管T]、T2的集电极电流将是:

A.0;B.Vcc/Rc;C.2Vcc/Rc;D.Vcc/2Rc。

解:

其交替输入高低电平下,Ti和T2将轮流饱和导电,所以集电极电流近似为:

C.2VCC/Rc

题3.2.12写出题图3.2.12所示门电路的输出表达式Y,并画出相应的逻辑符号。

题图3.2.12

解:

电路为4只管子并联使用,所以,该电路实现的是一个4变量的或

非逻辑功能。

即:

Y=FiF2=A+BC+D=A+B+C+D

题3.2.13写出题图3.2.13所示逻辑门电路的输出表达式F,并画出相应的逻辑符号。

题图3.2.13

解:

电路是二个TTL与非门的并联,其中的A、B、C实现与扩展,所以电路是一个与-或非功能电路。

输出逻辑关系为:

F=ABC+~DE=ABC+DE

题3.2.14已知TTL缓冲器7404(集电极开路门(OC门))的参数如下:

Voh=3.0V(max),Vffl=2.0V;VOL=0.4V,VIL=O.8V;I°h=—250)iA,

I[H=40piA;40mA,Iil=1•6mA.

若将7个这样的OC门输出相连后,再去驱动7个标准的TTL门(74系列),试决定OC门的电源电压Vcc,及外接集电极电阻Rc。

解:

这是OC门驱动TTL门电路的问题。

7个OC门连接后的输出电流能力如下:

IoHmax=7X(_0.25)=_1.75mA,IoLmax=7X40=280mA;

则OC门输出高电平时,

题3.2.15题图3.2.15所示电路为一信息传输的总线系统,任何时刻它

只能允许有一个门驱动总线,试计算该系统最大可能连接的驱动门数目N。

设三态门输出高阻时的漏电流为40心,正常工作时I°h=—5.2mA,1田=40心。

题图3.2.15

题3.2.16现有5个集电极开路的TTL门构成的“线与”输出系统,并带有同类门6个作负载,如题图3.2.16所示。

已知V°h=2.4V,Vol=0.4V,Ioh=250)jA,IOL=16mA,IIH=40p.A,IIL=—1.6mA,VCC=5V.试选择合适的电阻Rc值.

题3.2.17对题图3.2.17所示标准TTL与非门,若B端分别接电压0V、0.2V、3.6V及5V,试问A输入端上电压表的读数各为多少?

将结果填入表中。

题图3.2.17

解:

当B端连接+5V和+3.6V的时候,电压表量到的电压近似为1.4V;当B连到+0。

2V和0V时,测到的分别是+0。

2V和0V电压。

题3.2.18题图3.2.18所示为两种门电路的电压传输特性,是在相同电

源电压下(+5V)测得的,由此可看出实线为什么门电路;而虚线则又为什

解:

实线是CMOS门电路,虚线是TTL集成逻辑运门电路。

题3.2.19试写出题图3.2.19所示CMOS逻辑电路的输出(P,F)表达式,输入变量为A、B、C,并画出相应的逻辑符号。

题图3.2.19

解:

因CMOS门电路中的NMOS和PMOS是成对出现的特点,所以下列几点的逻辑关系分别是:

D=A+B,P=AB+D,

F=PC=0C=1

F=高阻态C=1C=0

题3.2.20试写出题图3.2.20所示CMOS逻辑电路的输出(P、Q)表达式,输入变量为A、B、C、D及E;并画出相应逻辑符号.

题图3.2.20

解:

因为CMOS中的PMOS和NMOS管总是成对出现的,而P和Q经传输门门控制,所以有表达式;

Q=PE=AB+CD.E

题3.2..21对于题图3.2..21所示逻辑电路,当用TTL器件构成时,其输出逻辑关系为匕=云+万C;当用CMOS器件构成时,输出yc=1.

题图3.2..21

题32.22试分析题图3.2..22(a)、(b)所示电路的逻辑功能。

写出Y-Y2的逻辑表达式。

图中的门电路均为CMOS门电路,这种连接方式能否用

于TTL门电路?

题图3.2..22

解:

根据电路有Yi和丫2表达式:

Yx=ABC+DEF=ABCDEF

Y2=A+B+C•D+E+F=A+B+C+D+E+F

这是一种“与”和“或”输入端的扩展电路。

这种连接不适用TTL电路,因为对(a)电路讲,输出高电平会下降一个二极管的压降。

对(b)电路讲使输出低电平升高了一个二极管的压降。

题3.2..23门电路组成的逻辑电路如题图3.2..23所示,请写出Fi、F2的逻辑表达式。

当输入图示信号波形时,画出Fi、F2端的输出波形。

b——

CI

题图3.2..23

解:

写方程时应该注意三态门的控制关系。

F,=ABC+BC=AB+BC

F2=(A©B)C+BC=AC+BC

其Fi和F2的波形为:

题32.24CMOS器件4007的内部电路和引出端如题图3.2..24所示,请用4007电路接成:

(1)3个反相器;

(2)—个3输入端的或非门;(3)一个3输入端的与非门;(4)传输门。

题图3.2..24

解:

接成CMOS反相器、三输入或非门、三输入与非门和传输门分别如图(a)、(b)、(c)和(d)所示:

题32.25试分析题图32.25所示电路,写出各输出函数L。

,L”L2,L3的逻辑表达式。

题图32.25二极管逻辑电路

解:

这是一个二极管的只读存储器电路,由二极