《数字电子技术》康华光习题.docx

《《数字电子技术》康华光习题.docx》由会员分享,可在线阅读,更多相关《《数字电子技术》康华光习题.docx(8页珍藏版)》请在冰豆网上搜索。

《数字电子技术》康华光习题

第八章半导体存储器和可编程逻辑器件

一、填空题

1、一个10位地址码、8位输出的ROM,其存储容量为或。

2、将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM。

该ROM有根地址线,有根数据读出线。

二、综合题

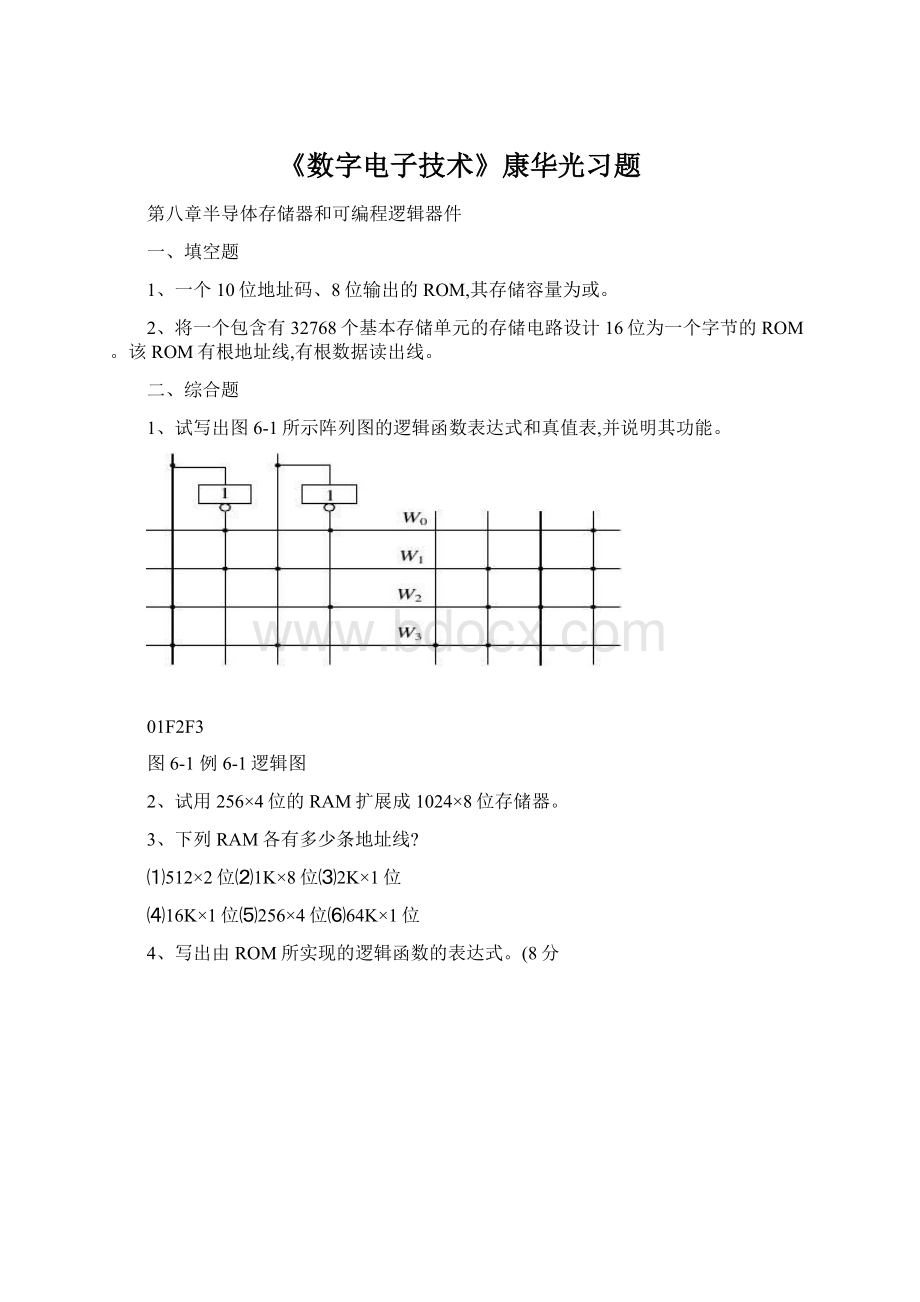

1、试写出图6-1所示阵列图的逻辑函数表达式和真值表,并说明其功能。

01F2F3

图6-1例6-1逻辑图

2、试用256×4位的RAM扩展成1024×8位存储器。

3、下列RAM各有多少条地址线?

⑴512×2位⑵1K×8位⑶2K×1位

⑷16K×1位⑸256×4位⑹64K×1位

4、写出由ROM所实现的逻辑函数的表达式。

(8分

Y1

Y2

5、四片16×4RAM和逻辑门构成的电路如图6-7所示。

试回答:

ABAB4

ABAB0

地

址线

数据线

图6-7多片RAM级联逻辑图

⑴单片RAM的存储容量,扩展后的RAM总容量是多少?

⑵图6-7所示电路的扩展属位扩展,字扩展,还是位、字都有的扩展?

⑶当地址码为00010110时,RAM0~RAM3,哪几片被选中?

6.用ROM设计一个组合逻辑电路,用来产生下列一组逻辑函数。

画出存储矩阵的点阵图。

DCBADCBADCBADCBAY⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=1DCBADCBADCBADCBAY⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=2DCBDBAY⋅⋅+⋅⋅=3DBDBY⋅+⋅=4

7、画出实现下面双输出逻辑函数的PLD表示。

D

CABC

DBADCBADCBADCBAfABC

CBACBACBAf,,,(,,(21+++=++=

三、简答题

1、可编程逻辑器件是如何进行分类的?

2、GAL16V8的OLMC中4个数据选择器各有多少功能?

3、ROM和RAM有什么相同和不同之处?

ROM写入信息有几种方式?

4、为什么用ROM可以实现逻辑函数式?

第八章习题答案

一、填空题

1、213

8K2、1116二、综合题

1、解:

根据与阵列的输出为AB的最小项和阵列图中有实心点·为1,无·为0,可以写出

ABWF==30

BAABBABAWWWF+=++=++=3211BABABAF⊕=+=2

ABBABABABAWWWF=+=++=++=2103

从上述逻辑表达式可以看出,图6-1所示阵列图实现了输

入变量A、B的四种逻辑运算:

与、或、异或和与非。

列出真值表如表6-1所示。

2、解:

当一片RAM不能满足存储容量需要时,需要将若干片RAM组合起来,构成满足存储容量要求的存储器。

RAM的扩展分为位扩展和字扩展两种。

如果一片RAM的字数满足要求,而位数不够时,应采用位扩展。

字数满足要求,就是地址线满足要求。

只要将若干片RAM并接起来,所有芯片的位线加起来作为扩展后的位线,便可以实现位扩展。

实现位扩展的原则是:

①多个单片RAM的I/O端并行输出,作为RAM的输出端—数据线或称位线。

如两片四位RAM的I/O端并行输出,得八位RAM;

②多个单片RAM的CS端接到一起,作为RAM的片选端(多片RAM同时被选中;③多个单片RAM的地址端对应接到一起,作为RAM的地址输入端。

④多个单片RA3M的WR/端接到一起,作为RAM的读/写控制端(RAM的WR/读写控制端只能有一个;

在RAM的数据位的位数足够,而字数达不到要求时,需要进行字扩展。

字数增加,地址线数就得相应增加。

如256×8位RAM的地址线数为8条,而1024×8位RAM的地址线数为10条。

实现字扩展的原则是:

①多个单片RAM的I/O端并接,作为RAM的I/O端(不需位扩展;

②多个单片RAM构成字扩展之后,每次访问只能选中一片,选中哪一片,由字扩展后多出的地址线决定。

多出的地址线经输出低有效的译码器译码,接至各片RAM的CS端;

③多个单片RAM的地址端对应接到一起,作为RAM的低位地址输入端。

④多个单片RAM的WR/端接到一起,作为RAM的读/写控制端(RAM的WR/读写控制端只能有一个;

1024×8位存储器需256×4位的芯片数

8

425681024=⨯⨯==一片的存储容量总存储容量C

两片256×4位的RAM并联实现位扩展,达到8位的要求。

根据2n=字数,求得1024个字的地址线数n=10,256字的存储器只有8条地址线,多余的两条地址线A9A8需要接2-4译码器输入端,译码器的输出端对应接到2片256×4位RAM的CS端,连接方式如图6-3

表6-1真值表

所示。

AA地

址总线数据总线图6-3256×4位RAM扩展成1024×8位存储器

3、解:

⑴512×2位:

512=29,故有9个地址输入端。

⑵1K×8位:

1K=1024=210,故有10个地址输入端。

⑶2K×1位:

2K=2048=211,故有11个地址输入端。

⑷16K×1位:

16K=214,故有14个地址输入端。

⑸256×4位:

256=28,故有8个地址输入端。

⑹64K×1位:

64K=216,故有16个地址输入端。

4、5、解:

⑴单片RAM的容量是16×4=64个存储单元,扩展后的RAM总容量为25×8=256个存储单元。

⑵图6-7所示电路为位、字都有的扩展。

⑶当地址码为00010110时,RAM0~RAM3中的RAM2和RAM3片选端有效,因此被选中。

6、解:

由题中给定的逻辑函数知

1510501WWWWDCBADCBADCBADCBAY+++=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=

138722WWWWDCBADCBADCBADCBAY+++=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=

2

10463WWWWDCBADCBADCBADCBADCBDBAY+++=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅+⋅⋅=

28105713154WWWWWWWWD

CBA

DCBADCBADCBADCBADCBADCBADCBAD

BADBADBADBADBDBY+++++++=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅+⋅⋅+⋅⋅+⋅⋅=+⋅=由此画出实现上述逻辑函数的逻辑图如图6-8所示。

21ABCCBABCAYABCCBACBCBAY++=+++=

ABCD

与门阵列

地址译码器

Y1Y2Y3Y4

图6-8题6-9实现逻辑函数逻辑图

7、解:

根据图中给出的逻辑函数,画出PLD表示如图7-2所示。

21题7-2实现逻辑图

三、

1、解:

⑴根据芯片的集成度和结构复杂度分类分为:

①简单可编程逻辑器件SPLD②复杂可编程逻辑器件CPLD③现场可编程逻辑门阵列FPGA。

⑵按制造技术和编程方式进行分类

①双极熔丝制造技术的可编程ASIC(Lattice的PAL系列②EECMOS制造技术的可编程ASIC(Lattice的GAL和ispLSI/pLSI③SRAM制造技术的可编程ASIC(Xilinx的FPGA,Altera的FPGA④反熔丝制造技术的可编程ASIC(Actel的FPGA。

2、GAL16V8的OLMC中的4个数据选择器分别为:

乘积项数据选择器PTMUX是2选1数据选择器,其主要功能是在AC0,AC1(n的控

《数字电子技术》康华光习题&解答制下,用来决定第一与项是否成为或门的输入.输出多路开关OMUX是2选1数据选择器,OMUX的作用是在AC0和AC1(n的控制下,决定输出是组合电路还是时序电路.三态多路开关TSMUX是4选1数据选择器.它用来从VCC,地电平,OE,第一与项四路信号中选出一路信号作为输出三态缓冲器的三态控制信号.反馈多路开关FMUX是4选1数据选择器.它用来从触发器的Q端,本级输出,邻级输出,地电平这四路信号中选出一路作为反馈信号,反馈到与阵列.3,ROM和RAM都是存储器,可以用来写入二进制信息.不同之处是ROM写入之后不能擦除(只能通过特殊方法擦除;RAM可以随机存取信息.ROM写入信息有以下几种方式:

固定ROM由厂家写入;可编程ROM由用户将熔丝通过大电流写入信息;可擦可编程ROM可以多次写入和擦除信息,但需要经过专门的编程器,实现光和电擦除等.4,ROM的存储矩阵由与阵列和或阵列组成.与阵列的输入为地址码,输出为地址译码器的输出,包含了全部输入变量的最小项.或阵列的输出(数据输出为最小项之和.这样,用具有2n个译码输出和m位数据输出的ROM,可以得到一组最多为m个输出的n个变量的逻辑函数.6