基于FPGA的FIR滤波器设计.docx

《基于FPGA的FIR滤波器设计.docx》由会员分享,可在线阅读,更多相关《基于FPGA的FIR滤波器设计.docx(16页珍藏版)》请在冰豆网上搜索。

基于FPGA的FIR滤波器设计

本报告分两部分:

1由matlab计算FIR数字滤波器的滤波系数;

2用VHDL语言设计逻辑电路,再通过QUARTUSII软件,将各个模块的电路封装成期间,在顶层设计中通过连线,完成整个系统。

所有源程序在本文档同一文件夹下的fir文件中。

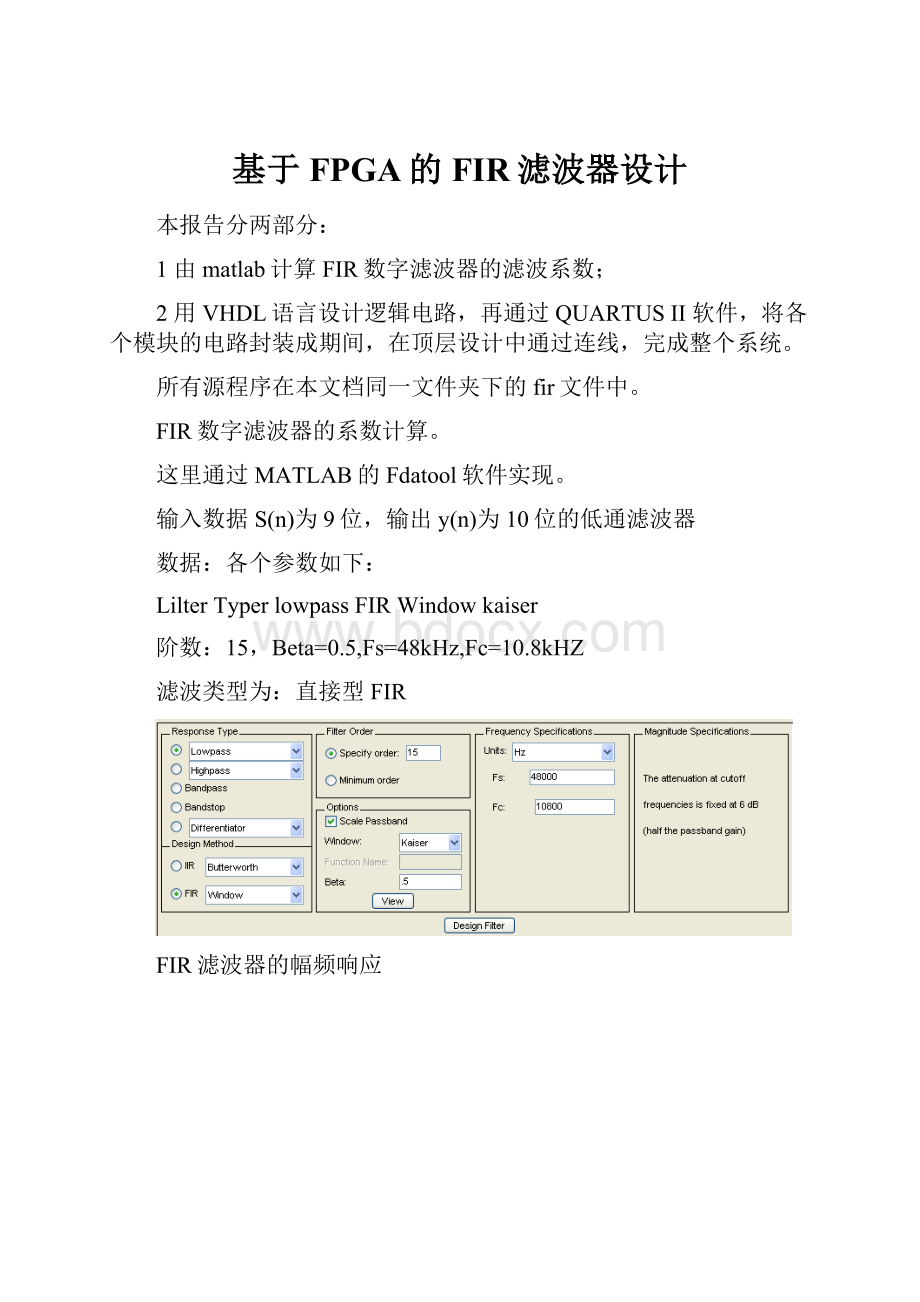

FIR数字滤波器的系数计算。

这里通过MATLAB的Fdatool软件实现。

输入数据S(n)为9位,输出y(n)为10位的低通滤波器

数据:

各个参数如下:

LilterTyperlowpassFIRWindowkaiser

阶数:

15,Beta=0.5,Fs=48kHz,Fc=10.8kHZ

滤波类型为:

直接型FIR

FIR滤波器的幅频响应

相频响应

FIR滤波器的冲击响应

滤波器系数

对系数进行调整,整数化:

Num=

-0.07420.02340.11330.0117-0.1758-1.0977

0.35940.82810.82810.35940.0977-0.1758

0.01170.11330.0234-0.0742

Num*(2^8)

ans=

Columns1through10

-18.99525.990429.00482.9952-45.0048-281.011292.0064211.9936211.993692.0064

Columns11through16

25.0112-45.00482.995229.00485.9904-18.9952

FIR数字滤波器的VHDL实现

根据作业要求,S(n)为9位,y(n)为10位的低通滤波器。

数据:

-19,6,29,3,-45,-25,92,212,212,92,-25,-45,3,29,6,-19

阶数:

15,Beta=0.5,Fs=48kHz,Fc=10.8kHZ

滤波类型为:

直接型FIR

FIR滤波器的原理图设计如下:

设计原理:

一概要

我的原理说明是根据上面原理图的设计顺序逐步进行的。

1寄存器(延时器)。

原理图上标有dff9的器件。

输入9位数据,通过dff9的D触发寄存器,达到延时的作用。

2第一级加法器

数据通过add9910,就是9位数字输入,10位数字输出加法器,完成第一级相加运算,因为本题是16阶FIR数字滤波器,它的滤波系数有对称的关系,所以采用上面的第一级加法器,达到简化运算的效果。

3乘法器

乘法器用来将数据乘以由matlab计算得到的滤波系数,本题的系数分别为:

-19,6,29,3,-45,-25,92,212。

在乘法器设计时暂时没有考虑符号,符号问题由下面的减法器实现。

即:

若系数符号为负,那么在下一级用减法器减去乘法器所得的数据。

所有的乘法器为:

mult19,multmult6,mult29,mult3,mult45,mult25,mult92,mult212。

4第二级加,减法器

第二级加法器主要有add111414,add151415,add161717。

add111414就是说11位数据加14位数据输出14位数据,说有的都是相同的命名规则。

减法器的作用是反映乘法器的负号的,对于负的滤波系数,在此相当于经过减法器相减。

5第三级加,减法器

与上一级大体相同的原理。

6输出

输出通过add141710,将上一级得到的14位和17位数据相加,再拿出相加结果的高十位作为输出。

到此,整个FIR数字滤波器设计完毕,下面详细说明各个部分的具体实现。

二详细说明

我的说明是根据上面的概要逐一展开的。

我的设计是先编写各个功能的vhdl源文件,再生成功能模块,最后在顶层用原理图的设计方法连线,组成整个系统。

1寄存器(延时器)

设计中用D触发器组成寄存器,实现寄存功能。

这里用来寄存一组9位的二进制数据。

实现功能:

在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁。

源文件:

ENTITYdff9IS

PORT(clk:

INSTD_LOGIC;

clear:

INSTD_LOGIC;

Din:

INSTD_LOGIC_VECTOR(8DOWNTO0);

Dout:

OUTSTD_LOGIC_VECTOR(8DOWNTO0));

ENDdff9;

ARCHITECTUREaOFdff9IS

BEGIN

PROCESS(clk,clear)

BEGIN

IFclear='1'THEN

Dout<="000000000";

ELSIFclear='0'THEN

IF(clk'EVENTANDclk='1')THEN

Dout<=Din;

ENDIF;

ENDIF;

ENDPROCESS;

ENDa;

2第一级加法器

实现两个二进制数字的相加运算。

当到达时钟上升沿时,将两数输入,运算,输出结果。

源文件:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_arith.ALL;

ENTITYadd9910is

PORT(clk:

inSTD_LOGIC;

Din1,Din2:

insigned(8downto0);

Dout:

outsigned(9downto0));

ENDadd9910;

ARCHITECTUREaofadd9910is

SIGNALs1:

signed(9downto0);

SIGNALs2:

signed(9downto0);

BEGIN

s1<=(Din1(8)&Din1);

s2<=(Din2(8)&Din2);

PROCESS(Din1,Din2,clk)

BEGIN

ifclk'eventandclk='1'then

Dout<=s1+s2;

endif;

endprocess;

enda;

3乘法器

功能:

将数据乘以由matlab计算得到的滤波系数。

总共有8个乘法器。

源文件(以mult19为例):

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_arith.all;

ENTITYmult19is

PORT

(clk:

INSTD_LOGIC;

Din:

INSIGNED(9DOWNTO0);

Dout:

OUTSIGNED(13DOWNTO0));

ENDmult19;

ARCHITECTUREaOFmult19IS

SIGNALs1:

SIGNED(13DOWNTO0);

SIGNALs2:

SIGNED(10DOWNTO0);

SIGNALs3:

SIGNED(13DOWNTO0);

BEGIN

P1:

process(Din)

BEGIN

s1(13DOWNTO4)<=Din;

s1(3DOWNTO0)<="0000";

s2(10DOWNTO1)<=Din;

s2(0)<='0';

ifDin(9)='0'then

s3<=('0'&s1(13downto1))+("0000"&s2(10DOWNTO1))+("00000"&Din(9DOWNTO1));

else

s3<=('1'&s1(13downto1))+("1111"&s2(10DOWNTO1))+("11111"&Din(9DOWNTO1));

endif;

endprocess;

P2:

PROCESS(clk)

BEGIN

ifclk'eventandclk='1'then

Dout<=s3;

endif;

ENDPROCESS;

ENDa;

4第二级加,减法器

对于乘了滤波系数的数据,进行第二次的加和,由于上面有的滤波系数是负的,所以这里用减法器对上一面的负系数做减法运算。

源程序:

减法器--sub121414

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_arith.ALL;

ENTITYsub121414is

PORT(clk:

inSTD_LOGIC;

Din1:

insigned(13downto0);

Din2:

insigned(11downto0);

Dout:

outsigned(13downto0));

ENDsub121414;

ARCHITECTUREaofsub121414is

SIGNALs1:

signed(13downto0);

BEGIN

s1<=(Din2(11)&Din2(11)&Din2);

PROCESS(Din1,Din2,clk)

BEGIN

ifclk'eventandclk='1'then

Dout<=s1-Din1;

endif;

endprocess;

enda;

加法器--add111414

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_arith.ALL;

ENTITYadd111414is

PORT(clk:

inSTD_LOGIC;

Din1:

insigned(10downto0);

Din2:

insigned(13downto0);

Dout:

outsigned(13downto0));

ENDadd111414;

ARCHITECTUREaofadd111414is

SIGNALs1:

signed(13downto0);

BEGIN

s1<=(Din1(11)&Din1(11)&Din1(11)&Din1);

PROCESS(Din1,Din2,clk)

BEGIN

ifclk'eventandclk='1'then

Dout<=s1+Din2;

endif;

endprocess;

enda;

还有add151415,add161717(略)

5第三级加,减法器

功能同上:

加法器--add141415

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_arith.ALL;

ENTITYadd141415is

PORT(clk:

inSTD_LOGIC;

Din1:

insigned(13downto0);

Din2:

insigned(13downto0);

Dout:

outsigned(14downto0));

ENDadd141415;

ARCHITECTUREaofadd141415is

SIGNALs1:

signed(14downto0);

SIGNALs2:

signed(14downto0);

BEGIN

s1<=(Din1(13)&Din1);

s2<=(Din1(13)&Din1);

PROCESS(Din1,Din2,clk)

BEGIN

ifclk'eventandclk='1'then

Dout<=s1+s2;

endif;

endprocess;

enda;

减法器—sub171517

源代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_arith.ALL;

ENTITYsub171517is

PORT(clk:

inSTD_LOGIC;

Din1:

insigned(14downto0);

Din2:

insigned(16downto0);

Dout:

outsigned(16downto0));

ENDsub171517;

ARCHITECTUREaofsub171517is

SIGNALs1:

signed(16downto0);

BEGIN

s1<=(Din1(14)&Din1(14)&Din1);

PROCESS(Din1,Din2,clk)

BEGIN

ifclk'eventandclk='1'then

Dout<=Din2-s1;

endif;

endprocess;

enda;

6输出级

输出通过一个加法器add151710完成10位数据的输出,通过一个15位与一个17位数据相加得到的数据取高10为作为最终结果。

源程序:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_arith.ALL;

ENTITYadd151710is

PORT(clk:

inSTD_LOGIC;

Din1:

insigned(14downto0);

Din2:

insigned(16downto0);

Dout:

outsigned(9downto0));

ENDadd151710;

ARCHITECTUREaofadd151710is

SIGNALs1:

signed(9downto0);

SIGNALs2:

signed(9downto0);

BEGIN

s1<=(Din1(13)&Din1(13)&Din1(14downto7));

s2<=(Din2(16downto7));

PROCESS(Din1,Din2,clk)

BEGIN

ifclk'eventandclk='1'then

Dout<=s1+s2;

endif;

endprocess;

enda;

三输出数据分析

任意输入一组信号:

Din=[96,0,0,0,48,0,0,0,96,0,0,0,48,0,0,0,96,0,0,0,48,0,0,0,96,0,0,0,48,0,0,0]

由quartusII仿真结果如下:

整理数据如下:

输出

Dout=[212-17-104480712928242428397272392824242839727239282424283972723928]

卷积结果:

h=[-19,6,29,3,-45,-25,92,212,212,92,-25,-45,3,29,6,-19];

y=conv(h,Din)/2^7

=

Columns1through10

-14.25004.500021.75002.2500-40.8750-16.500079.8750160.1250127.875064.1250

Columns11through20

37.500048.000040.875039.750075.0000129.0000129.000075.000039.750040.8750

Columns21through30

40.875039.750075.0000129.0000129.000075.000039.750040.875040.875039.7500

Columns31through40

75.0000129.0000143.250070.500018.000038.625081.750056.2500-4.8750-31.1250

Columns41through47

1.125010.87502.2500-7.1250000