俊杰数电报告汇总.docx

《俊杰数电报告汇总.docx》由会员分享,可在线阅读,更多相关《俊杰数电报告汇总.docx(22页珍藏版)》请在冰豆网上搜索。

俊杰数电报告汇总

设计内容

设计构成一个控制汽车六个尾灯的电路,用六个指示灯模拟六个尾灯(汽车每侧三个灯),并用两个拨动式(乒乓)开关作为转弯信号源;一个兵乓开关用于指示右转弯,一个乒乓开关用于指示左转弯,如果两个乒乓开关都被接通,说明驾驶员是一个外行,紧急闪烁器起作用。

右转弯时三个右边的灯应动作,左边的灯则全灭,右边的灯周期性明亮与暗,一周约需一秒,对于左转弯,左边灯的操作应相类似;当紧急闪烁起作用时,六个尾灯大约以1Hz的频率一致地闪烁着亮与暗。

同时,电路还用一个开关模拟脚踏制动器,制动时,若转弯开关未合上(或错误地将两个开关均合上的情况)所有六个尾灯均连续燃亮,在转弯的情况下,三个转向的尾灯应正常动作,另三个尾灯连续亮。

另一个开关模拟停车,停车时,全部尾灯亮度为正常的一半。

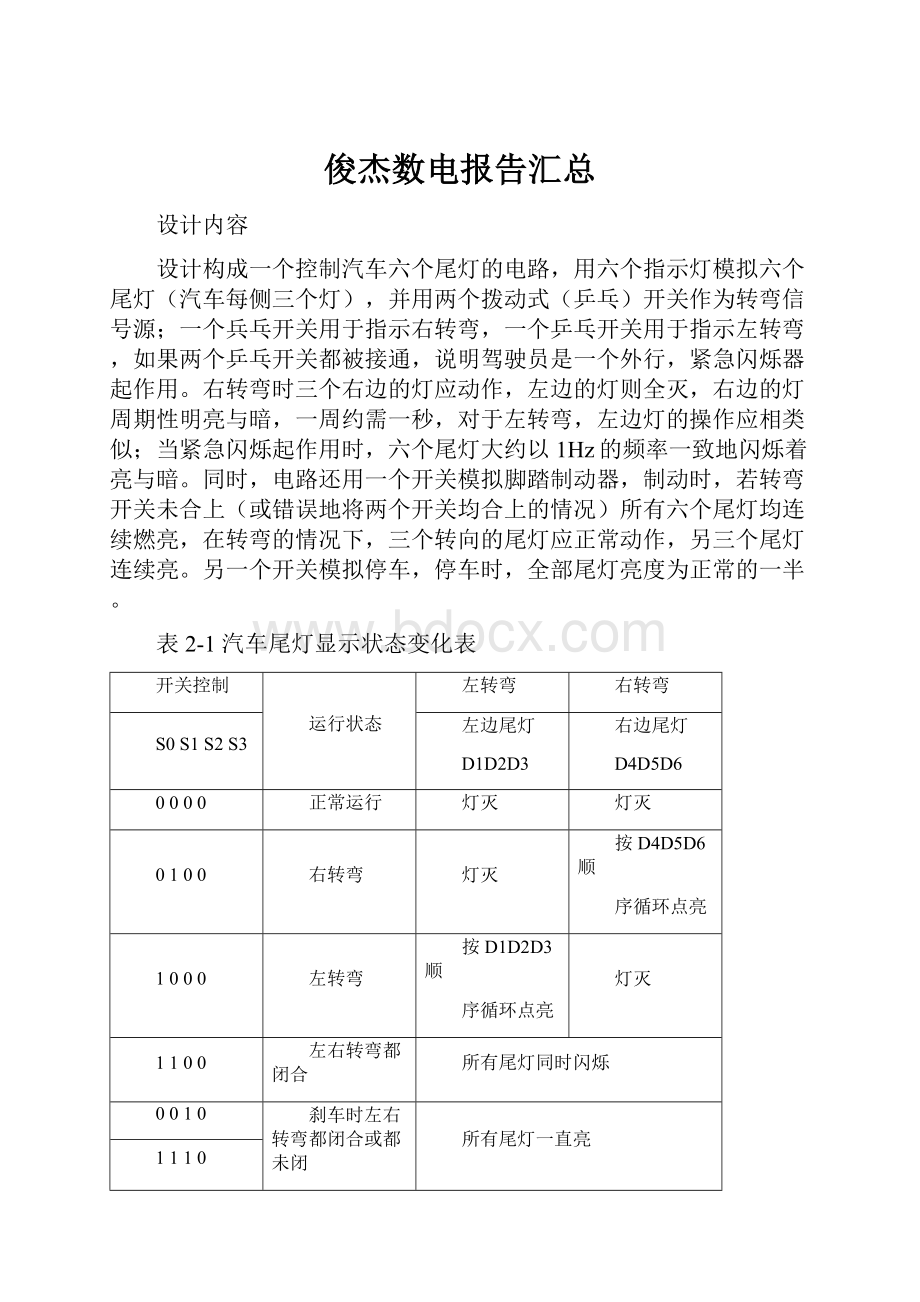

表2-1汽车尾灯显示状态变化表

开关控制

运行状态

左转弯

右转弯

S0S1S2S3

左边尾灯

D1D2D3

右边尾灯

D4D5D6

0000

正常运行

灯灭

灯灭

0100

右转弯

灯灭

按D4D5D6顺

序循环点亮

1000

左转弯

按D1D2D3顺

序循环点亮

灯灭

1100

左右转弯都闭合

所有尾灯同时闪烁

0010

刹车时左右转弯都闭合或都未闭

所有尾灯一直亮

1110

0110

刹车时右转弯

一直亮

按D4D5D6顺

序循环点亮

1010

刹车时左转弯

按D1D2D3顺

序循环点亮

一直亮

xxx1

停车

所有尾灯一直亮且亮度为正常时的一半

其中S0为右转弯开关,S1为左转弯开关,S2为刹车开关,S3为停车开关。

1.2设计目的

1)熟悉一些电工电子常用元器件及其基本性能;

2)掌握相关仪器/工具的使用方法;

3)掌握电子元件的焊接、电气元件的安装、连线等基本技能,建立电气原理图和电子线路图的基本概念,熟悉PROTEUS软件的基本使用。

第1节

第2节:

设计方案

本次设计采用模块化的设计方式,从结构图看电路有5部分组成,每个单元实际上都是独立的电路,而在三进制计数器电路中有很多设计方案主要有两种设计方案可选择,要通过各方面比较选出最合适的方案。

方案一:

由双JK触发器74LS76构成的三进制计数器;

方案二:

由D触发器构成的三进制计数器,采用一片双D触发器74LS74以及74LS00、74LS04共同来实现,电路需要三个芯片。

通过对方案一和方案二的比较,方案一所用器件少,成本低,所以选用方案一。

S1S2S3S4

系统框图

基本理论知识

3.1555定时器

555定时器是一种模拟和数字功能相结合的中规模集成器件。

一般用双极型(TTL)工艺制作的称为555,用互补金属氧化物(CMOS)工艺制作的称为7555,除单定时器外,还有对应的双定时器556/7556。

555定时器的电源电压范围宽,可在4.5V~16V工作,7555可在3~18V工作,输出驱动电流约为200mA,因而其输出可与TTL、CMOS或者模拟电路电平兼容。

555定时器成本低,性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器、单稳态触发器及施密特触发器等脉冲产生与变换电路。

它也常作为定时器广泛应用于仪器仪表、家用电器、电子测量及自动控制等方面。

555定时器的内部电路框图如图2.1所示。

图2.1

它内部包括两个电压比较器,三个等值串联电阻,一个RS触发器,一个放电管T及功率输出级。

它提供两个基准电压VCC/3和2VCC/3

它的各个引脚功能如下:

1脚:

外接电源负端VSS或接地,一般情况下接地。

2脚:

低触发端TR。

3脚:

输出端Vo

4脚:

是直接清零端。

当此端接低电平,则时基电路不工作,此时不论TR、TH处于何电平,时基电路输出为“0”,该端不用时应接高电平。

5脚:

VC为控制电压端。

若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF电容接地,以防引入干扰。

6脚:

高触发端TH。

7脚:

放电端。

该端与放电管集电极相连,用做定时器时电容的放电。

8脚:

外接电源VCC,双极型时基电路VCC的范围是4.5~16V,CMOS型时基电路VCC的范围为3~18V。

一般用5V。

在1脚接地,5脚未外接电压,两个比较器A1、A2基准电压分别为的情况下,555时基电路的功能表如表2-2所示。

表2-2555定时器的功能表

清零端

高触发端TH

低触发端TR

Q

放电管T

功能

0

x

x

0

导通

直接清零

1

0

1

x

保持上一状态

保持上一状态

1

1

0

1

截止

置1

1

0

0

1

截止

置1

1

1

1

0

导通

清零

3.1.2555定时器的功能

(1)构成单稳态触发器

单稳态触发器只有一个稳态状态。

在未加触发信号之前,触发器处于稳定状态,经触发后,触发器由稳定状态翻转为暂稳状态,暂稳状态保持一段时间后,又会自动翻转回原来的稳定状态。

单稳态触发器一般用于延时和脉冲整形电路。

接通电源后,未加负脉冲,而C充电,Vc上升,当Vc=2Vcc/3时,RS电路输出为低电平,放电管T导通,Vc快速放电,使Vc=0。

这样,在加负脉冲前,输出为低电平,即Vo=0,这是电路的稳态。

在t=

时刻

负跳变(

端电平小于Vcc/3),而Vc=0(TH端电平小于2Vcc/3),所以输出Vo翻为高电平,T截止,Vc充电。

按指数规律上升。

t=

时,负脉冲消失。

t=

时Vc上升到2Vcc/3(此时TH端电平大于2Vcc/3,TR端电平大于Vcc/3),Vo又自动翻为低电平。

[3]在

这段时间电路处于暂稳态。

t>

,T导通,C快速放电,电路又恢复到稳态。

由分析可得:

输出正脉冲宽度

=1.1RC

注意:

图2.2(a)电路只能用窄负脉冲触发,即触发脉冲宽度

必须小于

555定时器用于实际中的实例有:

能发出“叮、咚”声门铃的电路和旋光彩灯控制电路。

(2)构成多谐振荡器

多谐振荡器又称为无稳态触发器,它没有稳定的输出状态,只有两个暂稳态。

在电路处于某一暂稳态后,经过一段时间可以自行触发翻转到另一暂稳态。

两个暂稳态自行相互转换而输出一系列矩形波。

多谐振荡器可用作方波发生器。

接通电源后,输出假定是高电平,则T截止,电容C充电。

充电回路是VCC

—R1—R2—C—地,按指数规律上升,当上升到2Vcc/3时(TH、端电平大于Vc),输出翻转为低电平。

Vo是低电平,T导通,C放电,放电回路为C—R2—T—地,按指数规律下降,当下降到Vcc/3时(TH、端电平小于Vc),输出翻转为高电平,放电管T截止,电容再次充电,如此周而复始,产生振荡,经分析可得。

输出高电平时间T=(R1+R2)Cln2

输出低电平时间T=R2Cln2

振荡周期T=(R1+2R2)Cln2

输出方波的占空比为

3.2两输入与非门74LS00

两输入与非门是与门和非门的结合,先进行与运算,再进行非运算。

与运算输入要求有两个,如果输入都用0和1表示的话,那么与运算的结果就是这两个数的乘积。

如1和1(两端都有信号),则输出为1;1和0,则输出为0;0和0,则输出为0。

与非门的结果就是对两个输入信号先进行与运算,再对此与运算结果进行非运算的结果。

如图2.4为两输入与非门逻辑符号表示。

在图2.4中,A、B为输入端,C为输出端。

图2.4与非门逻辑符号

两输入与非门的状态方程为:

。

其真值表如表2-3所示。

表2-3两输入与非门真值表

A

B

C

0

0

1

0

1

1

1

0

1

1

1

0

本次设计中用到的74LS00是常用的两输入与非门集成电路芯片,其引脚图见图2.5。

其中1A-4A,1B-4B为输入端,1Y-4Y为输出端。

3.3异或门74LS86

异或门有2个输入端、1个输出端。

若两个输入的电平相异,则输出为高电平1;若两个输入的电平相同,则输出为低电平0。

图2.6为异或门的逻辑符号表示。

图2.6异或门逻辑符号

异或门的状态方程为

,其真值表如表2-4所示

表2-4异或门真值表

A1

B1

Y1

0

0

0

0

1

1

1

0

1

1

1

0

本次设计中用到的74LS86是常用的异或门集成电路芯片,其引脚图见图2.7。

其中1A-4A,1B-4B为输入端,1Y-4Y为输出端。

3.4与门74LS08

非门有1个输入端、1个输出端。

若

输入的电平为低电平,则输出为高电平;若输入的电平为高电平,则输出为低电平。

图2.8为非门的逻辑符号表示。

与门的状态方程为

,其真值表如表2-5所示

表2-5与门真值表

A

B

C

0

0

0

0

1

0

1

0

0

1

1

1

本次设计中用到的74HC04是常用的非门集成电路芯片,其引脚图见图2.9。

3.5非门74HC04

非门有1个输入端、1个输出端。

若

输入的电平为低电平,则输出为高电平;若输入的电平为高电平,则输出为低电平。

图2.10为非门的逻辑符号表示。

非门的状态方程为

,其真值表如表2-6所示

表2-6非门真值表

A

Y

0

1

1

0

本次设计中用到的74HC04是常用的非门集成电路芯片,其引脚图见图2.11。

其中A1-A6为输入端,Y1-Y6为输出端。

3.6三输入与非门74LS10

三输入与非门和两输入与非门一样,先进行与运算再进行非运算,只不过与运算时有三个输入端。

如图2.12为三输入与非门逻辑符号表示。

在图2.12中,A、B、C为输入端,Y为输出端。

图2.12三输入与非门逻辑符号

三输入与非门的状态方程为:

。

其真值表如表2-7所示。

表2-7三输入与非门真值表

A

B

C

Y

x

x

0

1

x

0

x

1

0

x

x

1

1

1

1

0

本次设计中用到的74LS10是常用的三输入输入与非门集成电路芯片,引脚图见图2.13。

3.7JK触发器74LS76

JK触发器是数字电路触发器中的一种电路单元。

JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。

在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。

由JK触发器可以构成D触发器和T触发器。

图2.14为JK触发器的逻辑符号。

JK触发器的状态方程为:

这里

表示现态,

表示次态。

现态表示时钟脉冲来到之前的触发器的输出状态,次态表示时钟脉冲来到之后的状态。

1、钟控JK触发器的电路如图2.15所示,门G1和G2构成基本RS触发器,门G3和G4构成触发器引导电路。

由图可见:

当CP=0使,

,

,触发器的状态保持不变。

当CP=1时,

,

,触发器接受输入激励,发生状态转移。

根据基本触发器的状态方程

可以得到当CP=1时

上式为钟控JK触发器的状态方程。

2、主从型JK触发器电路图如图2.16所示。

它由两个可控RS触发器串联组成,分别称为主触发器和从触发器。

J和K是信号输入端。

时钟CP控制主触发器和从触发器的翻转。

当CP=0时,主触发器状态不变,从触发器输出状态与主触发器的输出状态相同。

当CP=1时,输入J、K影响主触发器,而从触发器状态不变。

当CP从1变成0时,主触发器的状态传送到从触发器,即主从触发器是在CP下降沿到来时才使触发器翻转的。

下面分四种情况来分析主从型JK触发器的逻辑功能。

(1)J=l,K=l

设时钟脉冲到来之前(CP=0)触发器的初始状态为0。

这时主触发器的R=K,Q=0;S=J,

,时钟脉冲到来后(CP=l),主触发器翻转成1态。

当CP从1下跳为0时,主触发器状态不变,从触发器的R=0,S=1,它也翻转成1态。

反之,设触发器的初始状态为1。

可以同样分析,主、从触发器都翻转成0态。

可见,JK触发器在J=1,K=1的情况下,来一个时钟脉冲就翻转一次,即

具有计数功能。

(2)J=0,K=0

设触发器的初始状态为0,当CP=1时,由于主触发器的R=0,S=0,它的状态保持不变。

当CP下跳时,由于从触发器的R=1,S=0,它的输出为0态,即触发器保持0态不变。

如果初始状态为1,触发器亦保持1态不变。

(3)J=1,K=0

设触发器的初始状态为0。

当CP=l时,由于主触发器的R=0,S=1,它翻转成1态。

当CP下跳时,由于从触发器的R=0,S=1。

也翻转成1态。

如果触发器的初始状态为1,当CP=1时,由于主触发器的R=0,S=0,它保持原态不变;在CP从1下跳为0时,由于从触发器的R=0,S=1,也保持1态。

(4)J=0,K=1

设触发器的初始状态为1态。

当CP=1时,由于主触发器的R=1,S=0,它翻转成0态。

当CP下跳时,从触发器也翻转成0态。

如果触发器的初始状态为0态,当CP=1时,由于主触发器的R=0,S=0,它保持原态不变;在CP从1下跳为0时,由于从触发器的R=1,S=0,也保持0态。

本次设计中使用的JK触发器集成芯片为74LS76,74LS76是带有预置和清零输入的双JK触发器,属于下降沿触发的边沿触发器,其特性方程同样为

。

74LS76触发器的引脚如下图2.17所示,共16个引脚,其功能表和真值表分别见表2-8和表2-9

J

K

Qn+1

功能

0

1

Qn

保持

0

1

0

置0

1

0

1

置1

1

1

计数(翻转)

表2-874LS76功能表

表2-974LS76真值表

J

K

Qn+1

0

0

Qn

0

1

0

1

0

1

1

1

Qn

3.83线~8线译码器74LS138

译码器是一种具有“翻译”功能的逻辑电路,这种电路能将输入二进制代码的各种状态,按照其原意翻译成对应的输出信号。

有一些译码器设有一个和多个使能控制输入端,又成为片选端,用来控制允许译码或禁止译码。

74LS138是一种译码器,由于74LS138有3个输入端、8个输出端,所以,又称为3线~8线译码器。

三个输入端CBA共有8种状态组合(000—111),可译出8个输出信号Y0—Y7。

这种译码器设有三个使能输入端,当E1与E2均为0,且E1为1时,译码器处于工作状态,输出低电平。

当译码器被禁止时,输出高电平。

当一个选通端E1为高电平,另两个选通端E2和E3为低电平时,可将地址端A、B、C的二进制编码在Y0至Y7对应的输出端以低电平译出。

比如:

ABC=110时,则Y6输出端有效,输出低电平信号。

图2.18所示为74LS138的引脚图。

图中A、B、C为译码地址输入端;E1、E2、E3三个端口为选通端;Y0~Y7为译码输出端(低电平有效)。

表2-10为3线~8译码器74LS138的功能表。

表2-1074LS138的功能表

使能端

输入

输出

E3

E2/E1

A

B

C

/Y0

/Y1

/Y2

/Y3

/Y4

/Y5

/Y6

/Y7

X

H

X

X

X

H

H

H

H

H

H

H

H

L

X

X

X

X

H

H

H

H

H

H

H

H

H

L

L

L

L

L

H

H

H

H

H

H

H

H

L

L

L

H

H

L

H

H

H

H

H

H

H

L

L

H

L

H

H

L

H

H

H

H

H

H

L

L

H

H

H

H

H

L

H

H

H

H

H

L

H

L

L

H

H

H

H

L

H

H

H

H

L

H

L

H

H

H

H

H

H

L

H

H

H

L

H

H

L

H

H

H

H

H

H

L

H

H

L

H

H

H

H

H

H

H

H

H

H

L

表中H表示高电平,L表示低电平。

在本次设计中,通过控制3线~8线译码器74LS138的输出端有效(低电平)输出,选择性点亮发光二级管。

第4节各单元电路设计

4.1555时钟脉冲电路设计

由于555定时器构成的多谐振荡器的振荡频率稳定,不易受干扰[12]。

而且本次控制电路的设计中对脉冲精度要求不高,只要能实现可调即可。

故在该单元电路设计中选择采用555定时器构成多谐振荡器作为脉冲产生电路。

按照本次设计要求,需设计1HZ和3HZ两个频率的脉冲,故电路图中使用两块555定时器芯片分别产生脉冲,其中1HZ脉冲连接到显示驱动电路,3HZ脉冲连接到JK触发器脉冲端口。

由555定时器构成的多谐振荡器如图2.19、2.20所示,R1,R2和C1是外接定时元件,电路中将高电平触发端(THR)和低电平触发端(TRI)并接后接到R2和C1的连接处,将放电端(DIS)接R1,R2的连接处。

根据以下公式:

TPH对应充电时间为:

TPH=0.7(R1+R2)C;

TPL对应充电时间为:

TPL=0.7R2C;

振荡周期为:

T=TPH+TPL=0.7(R1+R2)C;

振荡频率为:

f=1/T。

可知:

当选择

,

时的脉冲频率为1HZ;

当选择

,

时的脉冲频率为3HZ。

仿真图如图2.21、2.22所示,产生的脉冲周期与要求基本相同。

4.2三进制循环控制电路设计

要实现三进制计数,其状态图如表2-11所示。

根据JK触发器的状态激励方程

可得出:

J=Q0nK=Q1n

三进制计数器可由两个JK触发器连接实现。

其电路图如图2.23所示。

表2-11三进制计数器的状态表

现态

次态

Q1

Q0

Q1

Q0

0

0

0

1

0

1

1

0

1

0

0

0