计算机电路基础复习题.docx

《计算机电路基础复习题.docx》由会员分享,可在线阅读,更多相关《计算机电路基础复习题.docx(22页珍藏版)》请在冰豆网上搜索。

计算机电路基础复习题

1、对于某一支路电流的参考方向。

A.可以任意设定B.必须与电流实际方向一致

C.要根据其它电流参考方向设定D.只能按顺时针方向设定

2、如图,已知E=5V,R=10Ω,I=1A,则电压U=()V。

A、15B、5C、—5D、10

3、稳压二极管是利用PN结的特性,来实现稳定电压作用的。

A.正向导通B.反向截止C.反向击穿D.温度特性

4、三极管当发射结和集电结都正偏时工作于()状态。

A.放大B.截止C.饱和D.无法确定

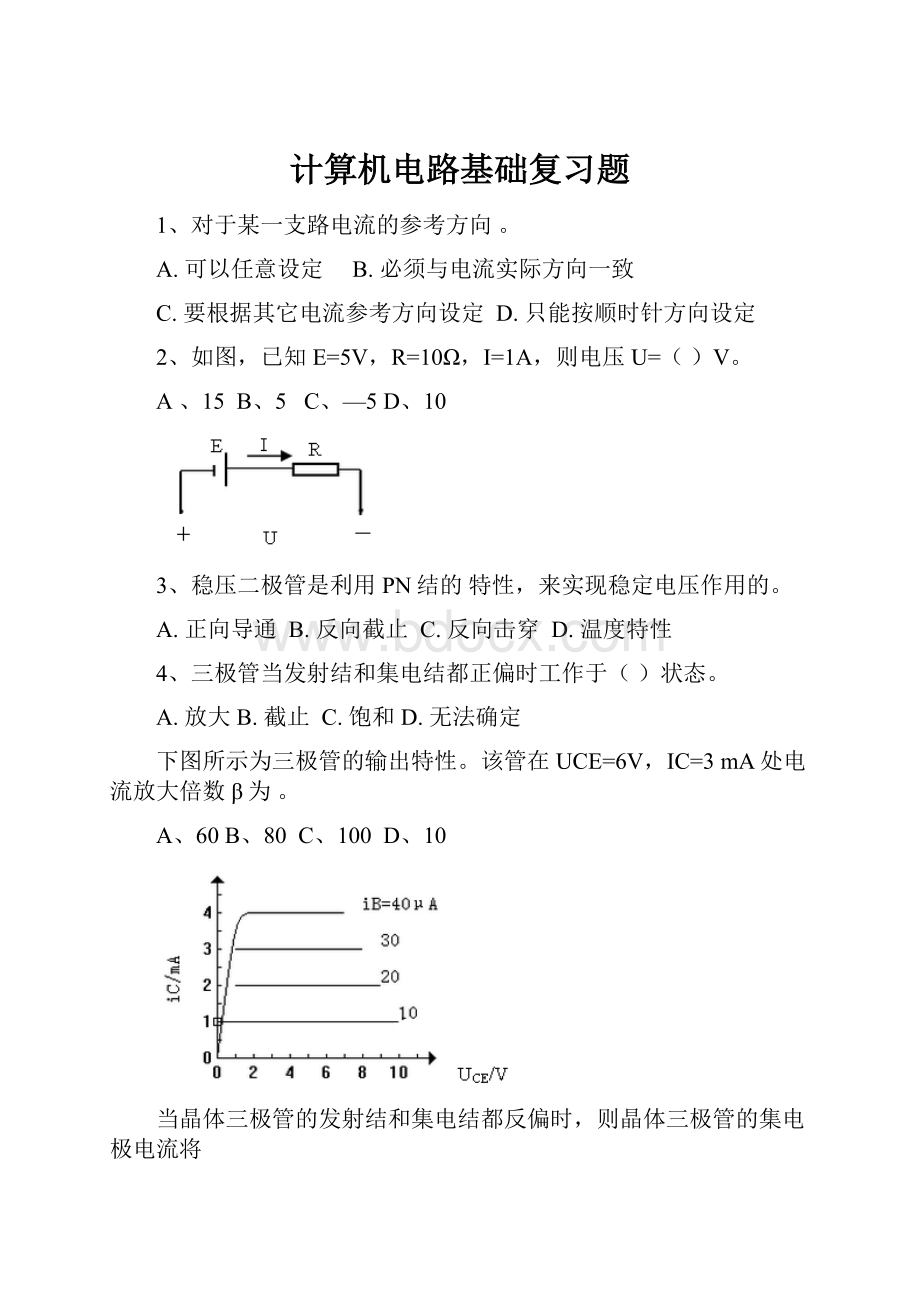

下图所示为三极管的输出特性。

该管在UCE=6V,IC=3mA处电流放大倍数β为。

A、60B、80C、100D、10

当晶体三极管的发射结和集电结都反偏时,则晶体三极管的集电极电流将

A、增大B、减少C、反向D、几乎为零

对放大电路中的三极管进行测量,各极对地电压分别为UB=2.7V,UE=2V,UC=6V,则该管工作在。

A、放大区B、饱和区C、截止区D、无法确定

某单管共射放大电路在处于放大状态时,三个电极A、B、C对地的电位分别是UA=2.3V,UB=3V,UC=0V,则此三极管一定是

A、PNP硅管B、NPN硅管C、PNP锗管D、NPN锗管

电路如图所示,该管工作在。

A、放大区B、饱和区C、截止区D、无法确定

测得三极管IB=30μA时,IC=2.4mA;IB=40μA时,IC=1mA,则该管的交流电流放大系数为。

A、80B、60C、75D、100

用直流电压表测得放大电路中某晶体管电极1、2、3的电位各为V1=2V,V2=6V,V3=2.7V,则。

A、1为e2为b3为cB、1为e3为b2为c

C、2为e1为b3为cD、3为e1为b2为c

晶体管共发射极输出特性常用一族曲线表示,其中每一条曲线对应一个特定的。

A、iCB、uCEC、iBD、iE

16、(2-1,低)某晶体管的发射极电流等于1mA,基极电流等于20μA,则它的集电极电流等于

A、0.98mAB、1.02mAC、0.8mAD、1.2mA

三极管各个极的电位如下,处于放大状态的三极管是。

A、VB=0.7V,VE=0V,VC=0.3V

B、VB=-6.7V,VE=-7.4V,VC=-4V

C、VB=-3V,VE=0V,VC=6V

D、VB=2.7V,VE=2V,VC=2V

某放大器由三级组成,已知每级电压放大倍数为KV,则总放大倍数为。

A、3KVB、(KV)3C、(KV)3/3D、KV

一个三级放大器,各级放大电路的输入阻抗分别为Ri1=1MΩ,Ri2=100KΩ,Ri3=200KΩ,则此多级放大电路的输入阻抗为。

A、1MΩB、100KΩC、200KΩD、1.3KΩ

选用差分放大电路的原因是。

A、克服温漂B、提高输入电阻C、稳定放大倍数D、提高放大倍数

差动放大器抑制零点漂移的效果取决于。

A、两个晶体管的静态工作点B、两个晶体管的对称程度C、各个晶体管的零点漂移D、两个晶体管的放大倍数

38差动放大电路的作用是。

A、放大差模B、放大共模C、抑制共模D、抑制共模,又放大差模

差动放大电路中当UI1=300mV,UI2=-200mV,分解为共模输入信号UIC=dmV,差模输入信号UID=amV。

A、500B、100C、250D、50

多级放大器前级输出电阻,可看成后级的。

A、信号源内阻B、输入电阻C、电压负载D、电流负载

在输入量不变的情况下,若引入的是负反馈,则以下说法正确的是

。

A、输入电阻增大B、输出量增大C、净输入量增大D、净输入量减小

48、(2-3,低)为了实现稳定静态工作点的目的,应采用。

A、交流正反馈B、交流负反馈C、直流正反馈D、直流负反馈

关于理想运算放大器的错误叙述是()。

A.输入阻抗为零,输出阻抗也为零;B.输入信号为零时,输出处于零电位;C.频带宽度从零到无穷大;D.开环电压放大倍数无穷大

在差动电路中,若单端输入的差模输入电压为20V,则其共模输入电压为()。

A.40VB.20VC.10VD.5V

1、理想运放的两个重要结论是( )

A 虚断VI+=VI-,虚短i I+=iI- B 虚断VI+=VI-=0,i I+=iI-=0

C虚断VI+=VI-=0,虚短i I+=iI- D 虚断i I+=iI-=0,虚短VI+=VI-

2、对于运算关系为V0=10VI的运算放大电路是( )

A 反相比例运算电路 B 同相比例运算电路 C 电压跟随器 D 加法运算电路

3、电压跟随器,其输出电压为V0=1,则输入电压为( ) A VI B - VI C 1 D -1

同相输入电路,R1=10K,Rf=100K,输入电压VI为10mv,输出电压V0为()

A-100mvB100mvC10mvD-10mv

5、加法器,R1=Rf=R2=R3=10K,输入电压V1=10mv,V2=20mv,V3=30mv,则输出电压为()

A60mvB100mvC10mvD-60mv

6、反相输入电路,R1=10K,Rf=100K,则放大倍数AVf为()

A10B100C-10D-100

电流并联负反馈可以使输入电阻( )输出电阻( )

A 增大,减小 B 增大,增大

C 减小,减小 D 减小,增大

如图1-2所示的电路中,A点电位为多少?

(A)6V(B)0V(C)3V(D)-6V

试回答在下列几种情况下,应分别采用哪种类型的滤波电路?

1.有用信号频率为10Hz。

()

2.有用信号频率低于1000Hz。

()

3.希望抑制50Hz交流电源的干扰。

()

4.希望抑制2kHz以下的信号。

()

(从a.低通,b.高通,c.带通,d.带阻四种滤波电路名称中选择一种填写在各小题后的括号中)

1.使用差动放大电路的目的是为了提高()。

A输入电阻B电压放大倍数C抑制零点漂移能力D电流放大倍数

2.差动放大器抑制零点漂移的效果取决于()。

A两个晶体管的静态工作点B两个晶体管的对称程度

C各个晶体管的零点漂移D两个晶体管的放大倍数

3.差模输入信号是两个输入信号的(),共模输入信号是两个输入信号的()。

A和B差C比值D平均值

4.电路的差模放大倍数越大表示(),共模抑制比越大表示()。

A有用信号的放大倍数越大B共模信号的放大倍数越大

C抑制共模信号和温漂的能力越强

5.差动放大电路的作用是()。

A放大差模B放大共模C抑制共模D抑制共模,又放大差模

6.差动放大电路由双端输入变为单端输入,差模电压增益是()。

A增加一倍B为双端输入的1/2C不变D不定

7.差动放大电路中当UI1=300mV,UI2=-200mV,分解为共模输入信号UIC=()mV,差模输入信号UID=()mV。

A500B100C250D50

8.在相同条件下,阻容耦合放大电路的零点漂移()。

A比直接耦合电路大B比直接耦合电路小C与直接耦合电路相同

9.差动放大电路由双端输出改为单端输出,共模抑制比KCMRR减小的原因是()。

AAUD不变,AUC增大BAUD减小,AUC不变

CAUD减小,AUC增大DAUD增大,AUC减小

1.直流放大器中的级间耦合通常采用(C)

(A)阻容耦合(B)变压器耦合(C)直接耦合(D)电感抽头耦合

2.差分放大电路的作用是(A)

(A)放大差模信号,抑制共模信号(B)放大共模信号,抑制差模信号(C)放大差模信号和共模信号(D)差模信号和共模信号都不放大

3.集成运放输入级一般采用的电路是(A)

(A)差分放大电路(B)射极输出电路(C)共基极电路(D)电流串联负反馈电路

4.典型差动放大电路的射极电阻Re对()有抑制作用。

(A)差模信号(B)共模信号(C)差模信号与共模信号(D)差模信号与共模信号都没有

5.集成运放有(C)。

(A)一个输入端、一个输出端(B)一个输入端、二个输出端(C)二个输入端、一个输出端(D)二个输入端、二个输出端

6.电路如图所示,这是一个(C)差动放大电路。

(A)双端输入、双端输出(B)双端输入、单端输出(C)单端输入、双端输出(D)单端输入、单端输出

1、十进制数1000对应二进制数为______,对应十六进制数为______。

A:

① 1111101010 ② 1111101000 ③ 1111101100 ④ 1111101110

B:

① 3C8

② 3D8

③ 3E8

④ 3F8

2、十进制小数为0.96875对应的二进制数为______,对应的十六进制数为______。

A:

① 0.11111 ② 0.111101 ③ 0.111111 ④ 0.1111111

B:

① 0.FC ② 0.F8 ③ 0.F2 ④ 0.F1

3、二进制的1000001相当十进制的______,二进制的100.001可以表示为______。

A:

① 62 ② 63 ③ 64 ④ 65

B:

① 23+2–3 ② 22+2–2 ③ 23+2–2 ④ 22+2–3

4、 十进制的100相当于二进制______。

① 1000000

② 1100000

③ 1100100

④ 1101000

5、八进制的100化为十进制为______,十六进制的100化为十进制为______。

A:

① 80 ② 72 ③ 64 ④ 56

B:

① 160 ② 180 ③ 230 ④ 256

6、在答案群所给出的关系式中正确的为______,在给出的等式中不正确的为______。

A:

① 0.1112<0.7510 ② 0.78>0.C16 ③ 0.610>0.AB16 ④ 0.1012<0.A16

B:

① 0.87510=0.E16 ② 0.748=0.937510 ③ 0.1012=0.A16 ④ 0.3116=0.1418

7、十六进制数FFF.CH相当十进制数______。

A:

① 4096.3 ② 4096.25 ③ 4096.75④ 4095.75

8、2005年可以表示为______ 年;而37308年是指______ 年。

A:

① 7C5H ② 6C5H ③ 7D5H ④ 5D5H

B:

① 200010 ② 200210 ③ 200610 ④ 200810

9、二进制数10000.00001可以表示为______;将其转换成八进制数为______;将其转换成十六进制数为______。

A:

① 25+2–5 ② 24+2–4 ③ 25+2–4 ④ 24+2–5

B:

① 20.02 ② 02.01 ③ 01.01 ④ 02.02

C:

① 10.10 ② 01.01 ③ 01.04 ④ 10.08

10、 对于不同数制之间关系的描述,正确的描述为______。

① 任意的二进制有限小数,必定也是十进制有限小数。

② 任意的八进制有限小数,未必也是二进制有限小数。

③ 任意的十六进制有限小数,不一定是十进制有限小数。

④ 任意的十进制有限小数,必然也是八进制有限小数。

11、二进制整数1111111111转换为十进制数为______,二进制小数0.111111转换成十进制数为______。

A:

① 1021 ② 1023 ③ 1024 ④ 1027

B:

① 0.9375 ② 0.96875 ③ 0.984375 ④ 0.9921875

12、 十进制的160.5相当十六进制的______,十六进制的10.8相当十进制的______。

将二进制的0.100111001表示为十六进制为______,将十六进制的100.001表示为二进制为______。

A:

① 100.5 ② 10.5 ③ 10.8 ④ A0.8

B:

① 16.8 ② 10.5 ③ 16.5 ④ 16.4

C:

① 0.139 ② 0.9C1 ③ 0.9C4 ④ 0.9C8

D:

① 28+2–8 ② 28+2–9 ③ 28+2–10 ④ 28+2–12

一、选择题(每题5分,共10题,总分50分)

1、组合逻辑电路产生竞争冒险的可能情况是

A.2个信号同时由0→1

B.2个信号同时由1→0

C.1个信号为0,另1个由0→1

D.1个信号为0→1,另1个由1→0

2、若在编码器中有50个编码对象,则要求输出二进制代码位数为A.5B、6C、10D、50

3、一个16选一的数据选择器,其地址输入(选择控制输入)端有()个。

A.1B.2C.4D.16

4、一个8选一数据选择器的数据输入端有()个

A、8B、2C、3D、4

5、在下列逻辑电路中,不是组合逻辑电路的有()。

A、译码器B、编码器C、全加器D、寄存器

6、101键盘的编码器输出()位二进制代码

A.B.6C.7D.8

7、以下电路中,加以适当辅助门电路,()适于实现单输出组合逻辑电路

A.二进制译码器B、加法器C、数值比较器D、七段显示译码器

8、组合逻辑电路在电路结构上的特点下列不正确的是()

A、在结构上只能由各种门电路组成

B、电路中不包含记忆(存储)元件<

C、有输入到输出的通路

D、有输出到输入的反馈回路

9、n个变量可以构成()个最小项。

A、nB、2C、2^nD、2^n-1

10、标准与或式是由()构成的逻辑表达式。

A、与项相或B、最小项相或C、最大项相与D、或项相与

1.下列表达式中不存在竞争冒险的有。

A.Y=

+ABB.Y=AB+

CC.Y=AB

+ABD.Y=(A+

)A

2.若在编码器中有50个编码对象,则要求输出二进制代码位数为位。

A.5B.6C.10D.50

3.一个16选一的数据选择器,其地址输入(选择控制输入)端有个。

A.1B.2C.4D.16

4.下列各函数等式中无冒险现象的函数式有。

A.

B.

C.

D.

E.

5.函数

,当变量的取值为时,将出现冒险现象。

A.B=C=1B.B=C=0C.A=1,C=0D.A=0,B=0

6.四选一数据选择器的数据输出Y与数据输入Xi和地址码Ai之间的逻辑表达式为Y=。

A.

B.

C.

D.

7.一个8选一数据选择器的数据输入端有个。

A.1B.2C.3D.4E.8

8.在下列逻辑电路中,不是组合逻辑电路的有。

A.译码器B.编码器C.全加器D.寄存器

9.八路数据分配器,其地址输入端有个。

A.1B.2C.3D.4E.8

10.组合逻辑电路消除竞争冒险的方法有。

A.修改逻辑设计B.在输出端接入滤波电容

C.后级加缓冲电路D.屏蔽输入信号的尖峰干扰

11.101键盘的编码器输出位二进制代码。

A.2B.6C.7D.8

12.用三线-八线译码器74LS138实现原码输出的8路数据分配器,应。

A.

=1,

=D,

=0B.

=1,

=D,

=D

C.

=1,

=0,

=DD.

=D,

=0,

=0

13.以下电路中,加以适当辅助门电路,适于实现单输出组合逻辑电路。

A.二进制译码器B.数据选择器C.数值比较器D.七段显示译码器

14.用四选一数据选择器实现函数Y=

,应使。

A.D0=D2=0,D1=D3=1B.D0=D2=1,D1=D3=0

C.D0=D1=0,D2=D3=1D.D0=D1=1,D2=D3=0

15.用三线-八线译码器74LS138和辅助门电路实现逻辑函数Y=

,应。

A.用与非门,Y=

B.用与门,Y=

C.用或门,Y=

D.用或门,Y=

1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N

2.在下列触发器中,没有约束条件的是。

A.主从JKB.主从DC.同步RSD.边沿D

3.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.3

4.存储8位二进制信息要个触发器。

A.2B.3C.4D.8

5.对于T触发器,若原态Qn=0,欲使新态Qn+1=1,应使输入T=。

A.0B.1C.QD.

6.对于T触发器,若原态Qn=1,欲使新态Qn+1=1,应使输入T=。

A.0B.1C.QD.

7.对于D触发器,欲使Qn+1=Qn,应使输入D=。

A.0B.1C.QD.

8.对于JK触发器,若J=K,则可完成触发器的逻辑功能。

A.RSB.DC.TD.Tˊ

9.欲使JK触发器按Qn+1=Qn工作,可使JK触发器的输端。

A.J=K=0B.J=Q,K=

C.J=

K=QD.J=Q,K=0

10.欲使JK触发器按Qn+1=

n工作,可使JK触发器的输端。

A.J=K=1B.J=Q,K=

C.J=

K=QD.J=Q,K=1

11.欲使JK触发器按Qn+1=0工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=1D.J=0,K=1

12.欲使JK触发器按Qn+1=1工作,可使JK触发器的输入端。

A.J=K=1B.J=1,K=0C.J=K=

D.J=K=0

13.欲使D触发器按Qn+1=

n工作,应使输入D=。

A.0B.1C.QD.

14.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从RS触发器C.同步RS触发器

D.主从JK触发器

15.下列触发器中,没有约束条件的是。

A.基本RS触发器B.主从RS触发器C.同步RS触发器

D.边沿D触发器

16.描述触发器的逻辑功能的方法有。

A.状态转换真值表B.特性方程C.状态转换图

D.状态转换卡诺图

17.为实现将JK触发器转换为D触发器,应使。

A.J=D,K=

B.K=D,J=

C.J=K=DD.J=K=

18.边沿式D触发器是一种稳态电路。

A.无B.单C.双D.多

1.同步计数器和异步计数器比较,同步计数器的显著优点是。

A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制。

2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。

A.4B.5C.9D.20

3.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器B.加法器C.数码寄存器D.数据选择器

4.N个触发器可以构成最大计数长度(进制数)为的计数器。

A.NB.2NC.N2D.2N

5.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N

6.五个D触发器构成环形计数器,其计数长度为。

A.5B.10C.25D.32

7.同步时序电路和异步时序电路比较,其差异在于后者。

A.没有触发器B.没有统一的时钟脉冲控制

C.没有稳定状态D.输出只与内部状态有关

8.一位8421BCD码计数器至少需要个触发器。

A.3B.4C.5D.10

9.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用级触发器。

A.2B.3C.4D.8

10.8位移位寄存器,串行输入时经个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.8

11.用二进制异步计数器从0做加法,计到十进制数178,则最少需要个触发器。

A.2B.6C.7D.8E.10

12.某电视机水平-垂直扫描发生器需要一个分频器将31500HZ的脉冲转换为60HZ的脉冲,欲构成此分频器至少需要个触发器。

A.10B.60C.525D.31500

13.某移位寄存器的时钟脉冲频率为100KHZ,欲将存放在该寄存器中的数左移8位,完成该操作需要时间。

A.10μSB.80μSC.100μSD.800ms

14.若用JK触发器来实现特性方程为

,则JK端的方程为。

A.J=AB,K=

B.J=AB,K=

C.J=

,K=ABD.J=

,K=AB

15.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需要片。

A.3B.4C.5D.10

16.若要设计一个脉冲序列为1101001110的序列脉冲发生器,应选用个触发器。

A.2B.3C.4D.10

10.组合逻辑电路中的冒险是由于引起的。

A.电路未达到最简B.电路有多个输出

C.电路中的时延D.逻辑门类型不同

11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?

A.在输出级加正取样脉冲B.在输入级加正取样脉冲

C.在输出级加负取样脉冲D.在输入级加负取样脉冲

12.当二输入与非门输入为变化时,输出可能有竞争冒险。

A.01→10B.00→10C.10→11D.11→01

13.译码器74HC138的使能端

取值为时,处于允许译码状态。

A.011B.100C.101D.010

14.数据分配器和有着相同的基本电路结构形式。

A.加法器B.编码器C.数据选择器D.译码器

15.在二进制译码器中,若输入有4位代码,则输出有个信号。

A.2B.4C.8D.16

16.比较两位二进制数A=A1A0和B=B1B0,当A>B时输出F=1,则F表达式是

。

A.

B.

C.

D.

17.集成4位数值比较器74LS85级联输入IA<B、IA=B、IA>B分别接001,当输入二个相等的4位数据时,输出FA<B、FA=B、FA>B分别为。

A.010B.001C.100D.011

18.实现两个四位二进制数相乘的组合电路,应有个输出函数。

A.8B.9C.10D.11

19.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要个异或门。

A.2B.3C.4D.5

20.在图T3.20中,能实现函数

的电路为。

(a)(b)(c)

图T3.20

A.电路(a