Veriloglab2.docx

《Veriloglab2.docx》由会员分享,可在线阅读,更多相关《Veriloglab2.docx(19页珍藏版)》请在冰豆网上搜索。

Veriloglab2

Verilog硬體描述語言實驗報告

實驗二:

2-digitup/downBCDcounter

系級:

學號:

姓名:

.

一、【實驗目的】:

本實驗主旨在練習BCDcounter設計,並熟悉Verilogbehavioral,dataflow或structuremodeling,探討電路之描述及模擬。

二、【實習儀器及設備】:

PC、SILOS(demo版)。

三、【實驗說明】:

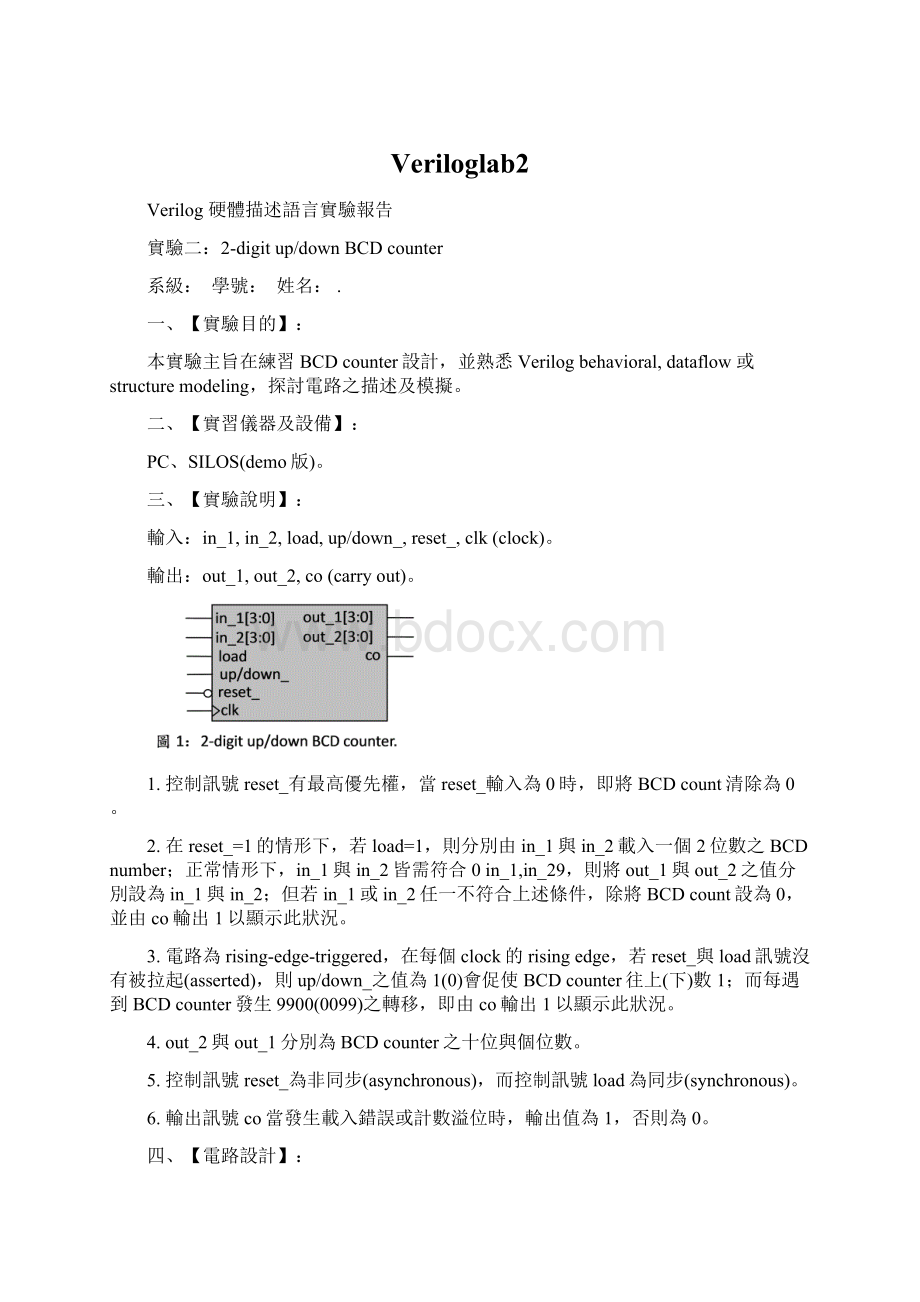

輸入:

in_1,in_2,load,up/down_,reset_,clk(clock)。

輸出:

out_1,out_2,co(carryout)。

1.控制訊號reset_有最高優先權,當reset_輸入為0時,即將BCDcount清除為0。

2.在reset_=1的情形下,若load=1,則分別由in_1與in_2載入一個2位數之BCDnumber;正常情形下,in_1與in_2皆需符合0in_1,in_29,則將out_1與out_2之值分別設為in_1與in_2;但若in_1或in_2任一不符合上述條件,除將BCDcount設為0,並由co輸出1以顯示此狀況。

3.電路為rising-edge-triggered,在每個clock的risingedge,若reset_與load訊號沒有被拉起(asserted),則up/down_之值為1(0)會促使BCDcounter往上(下)數1;而每遇到BCDcounter發生9900(0099)之轉移,即由co輸出1以顯示此狀況。

4.out_2與out_1分別為BCDcounter之十位與個位數。

5.控制訊號reset_為非同步(asynchronous),而控制訊號load為同步(synchronous)。

6.輸出訊號co當發生載入錯誤或計數溢位時,輸出值為1,否則為0。

四、【電路設計】:

設計電路模組實現上述2位數BCDcounter,並以VerilogHDL描述所設計之電路,可自由採用behavior,dataflow或structuremodeling模式。

BCDcounter電路之Verilogcode:

moduleBCD_counter(in_1,in_2,load,up_down_,reset_,clk,

out_1,out_2,co);

...//填入你的設計

endmodule

五、【電路模擬與驗證】:

撰寫testbench(附錄A)測試所設計之BCDcounter,並以Silos軟體之dataanalyzer顯示電路各訊號之變化波形,觀察輸出波形之對應,說明電路是否正確運作。

六、【心得感想】:

七、【參考資料】:

八、【附錄】:

A.BCDcounter電路之Verilogcode:

moduleBCD_counter_tb;

...

BCD_counterm1(in_1,in_2,load,up_down_,reset_,clk,

out_1,out_2,co);

...//完成你的testbench設計

endmodule

一、实验目的

1、掌握基本组合逻辑电路的实现方法,掌握连续赋值语句和条件赋值语句的使用方法;

2、掌握基本时序逻辑电路的实现,掌握always语句的使用方法。

二、实验原理、内容及步骤

1、简单组合逻辑设计

描述组合逻辑电路通常利用assign连续赋值语句的数据流方式。

连续赋值语句将值赋给线网(连续赋值不能为寄存器赋值)。

连续赋值语句只要在右端表达式的操作数上有事件(事件为值的变化)发生时,表达式即被计算,如果结果值有变化,新结果就赋给左边的线网。

连续赋值的目标类型如下:

1)标量线网;2)向量线网;3)向量的常数型位选择;4)向量的常数型部分选择;5)上述类型的任意的拼接运算结果。

组合逻辑设计示例:

可综合的数据比较器。

它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

描述组合逻辑时常使用assign结构。

注意equal=(a==b)?

1:

0,这是一种在组合逻辑实现分支判断时常使用的格式。

模块源代码:

//---------------compare.v-----------------

modulecompare(equal,a,b);

inputa,b;

outputequal;

assignequal=(a==b)?

1:

0;//a等于b时,equal输出为1;a不等于b时,

//equal输出为0。

endmodule

仿真波形(部分):

2、简单时序逻辑设计

在VerilogHDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。

在可综合的VerilogHDL模型,我们通常使用always块和@(posedgeclk)或@(negedgeclk)的结构来表述时序逻辑。

时序逻辑设计示例:

可综合的1/2分频器模型。

//half_clk.v:

modulehalf_clk(reset,clk_in,clk_out);

inputclk_in,reset;

outputclk_out;

regclk_out;

always@(posedgeclk_in)

begin

if(!

reset)clk_out=0;

else

clk_out=~clk_out;

end

endmodule

在always块中,被赋值的信号都必须定义为reg型,这是由时序逻辑电路的特点所决定的。

对于reg型数据,如果未对它进行赋值,仿真工具会认为它是不定态。

为了能正确地观察到仿真结果,在可综合风格的模块中我们通常定义一个复位信号reset,当reset为低电平时,对电路中的寄存器进行复位。

仿真波形:

三、实验设备及实验注意事项

计算机系统(PC机)

系统配置的基本需求:

CPU:

Intel奔腾系列,或AMDAthlon/XP;

操作系统:

WindownsNT/2000/XP;

内存:

256M或以上;

显卡:

支持256色的8位显卡或以上;

硬盘:

20G以上。

复杂时序逻辑电路的设计

一、实验目的

1、掌握条件语句if…else在复杂时序逻辑设计中的应用;

2、掌握阻塞赋值与非阻塞赋值的概念和区别,掌握阻塞赋值的使用情况。

二、实验原理、内容及步骤

1.条件语句在VerilogHDL中的使用

与常用的高级程序语言一样,为了描述较为复杂的时序关系,VerilogHDL提供了条件语句供分支判断时使用。

在可综合风格的VerilogHDL模型中常用的条件语句有if…else和case…endcase两种结构,用法和C程序语言中类似。

两者相较,if…else用于不很复杂的分支关系,实际编写可综合风格的模块、特别是用状态机构成的模块时,更常用的是case…endcase风格的代码。

条件语句示例:

可综合风格的分频器。

它的功能是将10M的时钟分频为500K的时钟。

基本原理与1/2分频器是一样的,但是需要定义一个计数器,以便准确获得1/20分频。

模块源代码:

//---------------fdivision.v-----------------------------

modulefdivision(RESET,F10M,F500K);

inputF10M,RESET;

outputF500K;

regF500K;

reg[7:

0]j;

always@(posedgeF10M)

if(!

RESET)//低电平复位。

begin

F500K<=0;

j<=0;

end

else

begin

if(j==19)//对计数器进行判断,以确定F500K信号是否反转。

begin

j<=0;

F500K<=~F500K;

end

else

j<=j+1;

end

endmodule

仿真波形:

2.设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别

非阻塞赋值语句(<=)右端表达式计算完后并不立即赋值给左端,而是同时启动下一条语句继续执行,而阻塞赋值语句(=)在每个右端表达式计算完成后立即赋值给左端变量。

非阻塞赋值不能用于assign语句中,而只能用于对寄存器型变量进行赋值,只能在intial和always等过程过程块中。

阻塞赋值既能用于assign语句,也能用于intial和always等过程赋值中。

对于时序逻辑的描述和建模,应尽量使用非阻塞赋值方式。

若在同一个always过程块中描述时序和组合逻辑混合电路时也最好使用非阻塞赋值方式。

在always块中,阻塞赋值可以理解为赋值语句是顺序执行的,而非阻塞赋值可以理解为赋值语句是并发执行的。

实际的时序逻辑设计中,一般的情况下非阻塞赋值语句被更多地使用,有时为了在同一周期实现相互关联的操作,也使用了阻塞赋值语句。

可综合设计中阻塞赋值和非阻塞赋值设计要点:

1)非阻塞赋值不能用于assign持续赋值中,一般只出现在initial和always等过程块中,对reg型变量进行赋值;

2)当用always块来描述组合逻辑时,既可以用阻塞赋值,也可以用非阻塞赋值。

但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值;

3)在向函数funtion的返回值赋值时,应使用阻塞赋值;

4)不能在一个以上的always过程块中对同一个变量赋值,这样会引起冲突,在综合时会报错;

5)在一个模块中,严禁对同一个变量既进行阻塞赋值,又进行非阻塞赋值,这样会在综合时报错;

6)对时序逻辑的描述和建模,应尽量使用非阻塞赋值方式,此外,若在同一个always过程块中描述时序和组合逻辑混合电路时,最好使用非阻塞赋值方式。

阻塞赋值与非阻塞赋值示例:

分别采用阻塞赋值语句和非阻塞赋值语句的两个看上去非常相似的两个模块blocking.v和non_blocking.v来阐明两者之间的区别。

模块源代码:

//-------------blocking.v---------------

moduleblocking(clk,a,b,c);

output[3:

0]b,c;

input[3:

0]a;

inputclk;

reg[3:

0]b,c;

always@(posedgeclk)

begin

b=a;

c=b;

$display("Blocking:

a=%d,b=%d,c=%d.",a,b,c);

end

endmodule

//-------------non_blocking.v-------------------

modulenon_blocking(clk,a,b,c);

output[3:

0]b,c;

input[3:

0]a;

inputclk;

reg[3:

0]b,c;

always@(posedgeclk)

begin

b<=a;

c<=b;

$display("Non_Blocking:

a=%d,b=%d,c=%d.",a,b,c);

end

endmodule

仿真波形(部分):

三、实验设备及实验注意事项

计算机系统(PC机)

系统配置的基本需求:

CPU:

Intel奔腾系列,或AMDAthlon/XP;

操作系统:

WindownsNT/2000/XP;

内存:

256M或以上;

显卡:

支持256色的8位显卡或以上;

硬盘:

20G以上。

函数和任务的应用设计

一、实验目的

1