计算机组成与结构课后答案67章习题.docx

《计算机组成与结构课后答案67章习题.docx》由会员分享,可在线阅读,更多相关《计算机组成与结构课后答案67章习题.docx(24页珍藏版)》请在冰豆网上搜索。

计算机组成与结构课后答案67章习题

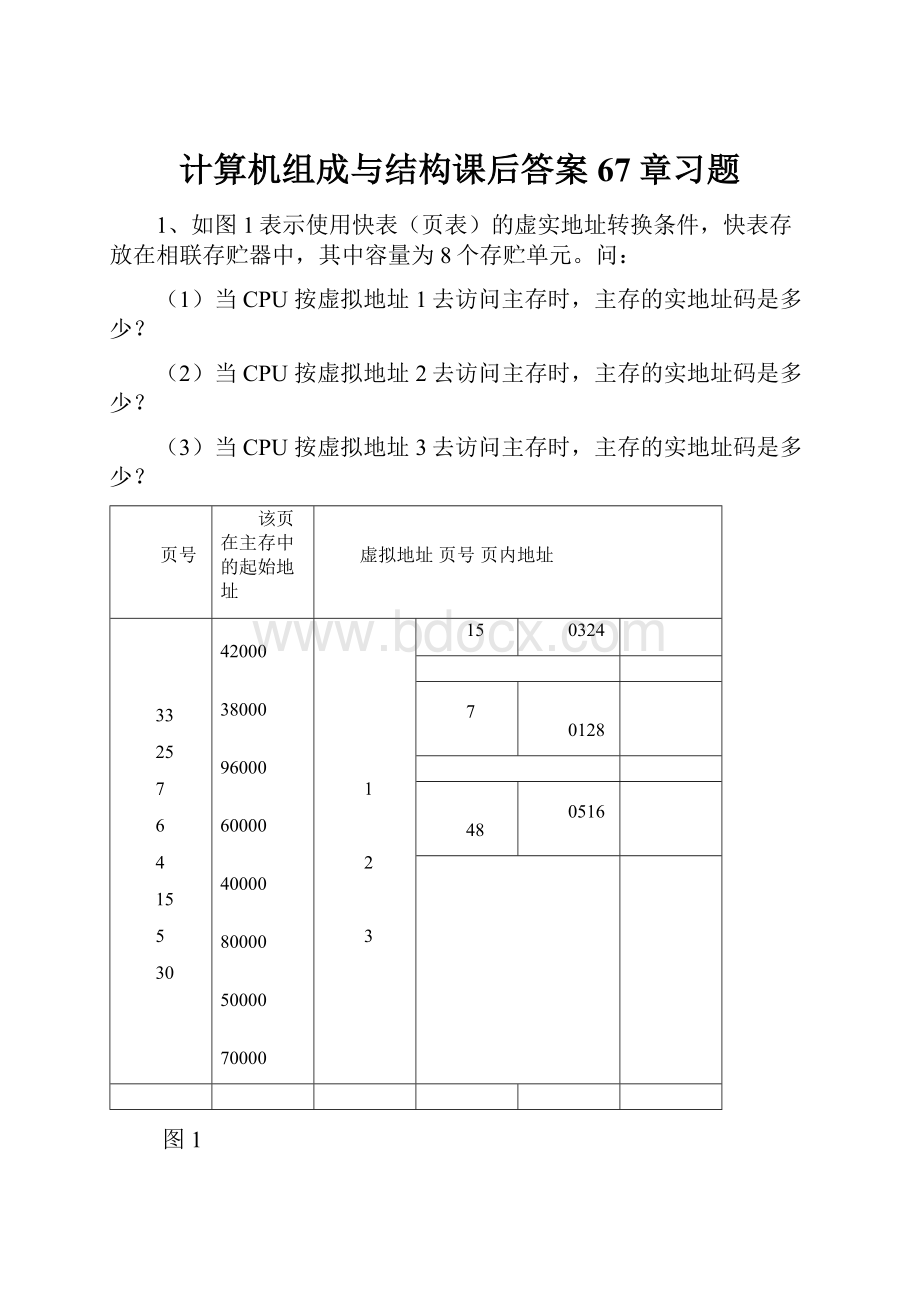

1、如图1表示使用快表(页表)的虚实地址转换条件,快表存放在相联存贮器中,其中容量为8个存贮单元。

问:

(1)当CPU按虚拟地址1去访问主存时,主存的实地址码是多少?

(2)当CPU按虚拟地址2去访问主存时,主存的实地址码是多少?

(3)当CPU按虚拟地址3去访问主存时,主存的实地址码是多少?

页号

该页在主存中的起始地址

虚拟地址页号页内地址

33

25

7

6

4

15

5

30

42000

38000

96000

60000

40000

80000

50000

70000

1

2

3

15

0324

7

0128

48

0516

图1

解:

(1)用虚拟地址为1的页号15作为快表检索项,查得页号为15的页在主存中的起始地址为80000,故将80000与虚拟地址中的页内地址码0324相加,求得主存实地址码为80324。

(2)主存实地址码=96000+0128=96128

(3)虚拟地址3的页号为48,当用48作检索项在快表中检索时,没有检索到页号为48的页面,此时操作系统暂停用户作业程序的执行,转去执行查页表程序。

如该页面在主存中,则将该页号及该页在主存中的起始地址写入主存;如该页面不存在,则操作系统要将该页面从外存调入主存,然后将页号及其在主存中的起始地址写入快表。

2、假设某计算机的运算器框图如图2所示,其中ALU为16位的加法器,SA、SB为16位暂存器,4个通用寄存器由D触发器组成,Q端输出,

其读写控制如下表所示:

读控制写控制

R0

RA0

RA1

选择

W

WA0

WA1

选择

1

1

1

1

0

0

0

1

1

x

0

1

0

1

x

R0

R1

R2

R3

不读出

1

1

1

1

0

0

0

1

1

x

0

1

0

1

x

R0

R1

R2

R3

不写入

要求:

(1)设计微指令格式。

(2)画出ADD,SUB两条指令微程序流程图。

图2

解:

(1)微命令字段共12位,微指令格式如下:

1212111111

R

RA0RA1

w

WA0WA1

LDSA

LDSB

SB->ALU

CLR

~

P字段

下址字段

各字段意义如下:

R—通用寄存器读命令

W—通用寄存器写命令

.RA0RA1—读R0—R3的选择控制。

WA0WA1—写R0—R3的选择控制。

LDSA—打入SA的控制信号。

LDSB—打入SB的控制信号。

SB->ALU—打开非反向三态门的控制信号。

SB->ALU—打开反向三态门的控制信号,并使加法器最低位加1。

CLR-暂存器SB清零信号。

~——一段微程序结束,转入取机器指令的控制信号。

(2)ADD、SUB两条指令的微程序流程图见图B2.3所示。

3、图B3.1所示的处理机逻辑框图中,有两条独立的总线和两个独立的存贮器。

已知指令存贮器IM最大容量为16384字(字长18位),数据存贮器DM最大容量是65536字(字长16位)。

各寄存器均有“打入”(Rin)和“送出”(Rout)控制命令,但图中未标出。

图B3.1

设处理机指令格式为:

171090

OP

X

加法指令可写为“ADDX(R1)”。

其功能是(AC0)+((Ri)+X)→AC1,其中((Ri)+X)部分通过寻址方式指向数据存贮器,现取Ri为R1。

试画出ADD指令从取指令开始到执行结束的操作序列图,写明基本操作步骤和相应的微操作控制信号。

解:

加法指令“ADDX(Ri)”是一条隐含指令,其中一个操作数来自AC0,另一个操作数在数据存贮器中,地址由通用寄存器的内容(Ri)加上指令格式中的X量值决定,可认为这是一种变址寻址。

因此,指令周期的操作流程图如图B3.4,相应的微操作控制信号列在框图外。

图B3.4

以知cache命中率H=0.98,主存比cache慢4倍,以知主存存取周期为200ns,求cache/主存的效率和平均访问时间。

解:

R=Tm/Tc=4;Tc=Tm/4=50ns

E=1/[R+(1-R)H]=1/[4+(1-4)×0.98]=0.94

Ta=Tc/E=Tc×[4-3×0.98]=50×1.06=53ns。

4、某计算机有8条微指令I1—I8,每条微指令所包含的微命令控制信号见下表所示,a—j分别对应10种不同性质的微命令信号。

假设一条微指令的控制字段仅限8位,请安排微指令的控制字段格式。

解:

为了压缩指令字的长度,必须设法把一个微指令周期中的互斥性微命令信号组合在一个小组中,进行分组译码。

经分析,(e,f,h)和(b,i,j)可分别组成两个小组或两个字段,然后进行译码,可得六个微命令信号,剩下的a,c,d,g四个微命令信号可进行直接控制,其整个控制字段组成如下:

01 e01b

直接控制10 f10 i

acdg11 h11 j

4位2位2位

5、CPU执行一段程序时,cache完成存取的次数为3800次,主存完成存取的次数为200次,已知cache存取周期为50ns,主存为250ns,求cache/主存系统的效率和平均访问时间。

解:

命中率H=Ne/(NC+Nm)=3800/(3800+200)=0.95

主存慢于cache的倍率:

r=tm/tc=250ns/50ns=5

访问效率:

e=1/[r+(1–r)H]=1/[5+(1–5)×0.95]=83.3%

平均访问时间:

ta=tc/e=50ns/0.833=60ns

6、运算器结构如图B5.2所示,R1,R2,R3是三个寄存器,A和B是两个三选一的多路开关,通路的选择由AS0,AS1和BS0,BS1端控制,例如BS0BS1=11时,选择R3,BS0BS1=01时,选择R1……,ALU是算术/逻辑单元。

S1S2为它的两个操作控制端。

其功能如下:

S1S2=00时,ALU输出=A

S1S2=01时,ALU输出=A+B

S1S2=10时,ALU输出=A–B

S1S2=11时,ALU输出=A⊕B

请设计控制运算器通路的微指令格式。

图B5.2

解:

采用水平微指令格式,且直接控制方式,顺序控制字段假设4位,其中一位判别测试位:

2位2位2位3位1位3位

←——————————直接控制———————————→←——顺序控制

当P=0时,直接用μAR1——μAR3形成下一个微地址。

当P=1时,对μAR3进行修改后形成下一个微地址。

7、某计算机有如下部件:

ALU,移位器,主存M,主存数据寄存器MDR,主存地址寄存器MAR,指令寄存器IR,通用寄存器R0——R3,暂存器C和D。

(1)请将各逻辑部件组成一个数据通路,并标明数据流向。

(2)

画出“ADDR1,(R2)”指令的指令周期流程图,指令功能是(R1)+((R2))→R1。

ALU

图B6.2

解:

(1)各功能部件联结成如图所示数据通路:

ALU+1

图B6.4

(2)此指令为RS型指令,一个操作数在R1中,另一个操作数在R2为地址的内存单元中,相加结果放在R1中。

送当前指令地址到MAR

取当前指令到IR,

PC+1,为取下条指令做好准备

①取R1操作数→C暂存器。

②R2中的内容是内存地址

从内存取出数→D暂存器

暂存器C和D中的数相加后送R1

图B6.5

8、某程序对页面要求的序列为0,1,3,4,3,2,0,2,1,3,2,设主存容量为3个页面,求FIFO和LRU替换算法时各自的命中率(假设开始时主存为空)。

要求给出过程。

答:

FIFO和LRU替换算法的命中率各占4分

页面请求

0

1

3

4

3

2

0

2

1

3

2

F

I

F

O

③

0

0

0

1

1

3

4

4

2

0

1

②

1

1

3

3

4

2

2

0

1

3

①

3

4

4

2

0

0

1

3

2

命中

×

×

×

×

√

×

×

√

×

×

×

L

R

U

③

0

0

0

1

1

4

3

3

0

2

1

②

1

1

3

4

3

2

0

2

1

3

①

3

4

3

2

0

2

1

3

2

命中

×

×

×

×

√

×

×

√

×

×

√

FIFO替换算法的命中率=2/11=18.2%

LRU替换算法的命中率=3/11=27.3%

9、CPU执行一段程序时,cache完成存取的次数为5000次,主存完成存取的次数为200次。

已知cache存取周期为40ns,主存存取周期为160ns。

求:

(1)Cache命中率H。

(2)Cache/主存系统的访问效率e。

(3)平均访问时间Ta。

解:

命中率H=Nc/(Nc+Nm)=5000/(5000+2000)=5000/5200=0.96

主存慢于cache的倍率R=Tm/Tc=160ns/40ns=4

访问效率:

e= 1/[r+(1-r)H]=1/[4+(1-4)×0.96]

=89.3℅

平均访问时间Ta=Tc/e=40/0.893=45ns

10、已知某系统采用页式虚拟存储器方案,某程序中一条指令的虚地址是:

000001111111100000,该程序的页表起始地址是0011,页面大小是1K,页表中有关单元最后4位是实页号。

求:

某指令地址(虚地址)变换后的主存实地址。

装入位

实页号

1

0001

…

1

0011

…

1

1100

解:

∵虚地址=虚页号+页内地址,

且页面大小=1KB=210

∴虚页号=00000111

∵页表索引地址

=页表起始地址+虚页号

=001100000111=307H

查页表得实页号为1100

∴主存实地址是

11001111100000。

装入位

实页号

1

0001

…

1

0011

…

1

1100

11、图(a)是某SRAM的写入时序,其中R/W是读、写命令控制线,当R/W线为低电平时,存贮器按给定地址把数据线上的数据写入存贮器。

请指出图中时序的错误,并画出正确的写入时序。

解:

写入存储器时时序信号必须同步。

通常,当R/W线加负脉冲时,地址线和数据线的电平必须是稳定的。

当R/W线一达到逻辑0电平时,数据立即被存储。

因此,当R/W线处于低状态时,如果数据线改变数值,那么存储器将存储新的数据⑤。

同样,当R/W线处于低状态时,地址发生了变化,那么同样的数据将存储到新的地址(②或③)。

正确的写入时序图如图(b)所示:

(图占6分,根据情况酌情加减分)

图(b)

12、某机运算器框图如图B7.1所示,其中ALU由通用函数发生器组成,M1—M3为多路开关,采用微程序控制,若用微指令对该运算器要求的所有控制信号进行微指令编码的格式设计,列出各控制字段的编码表。

解:

当24个控制信号全部用微指令产生时,可采用字段译码法进行编码控制,采用的微指令格式如下(其中目地操作数字段与打入信号段可结合并公用,后者加上节拍脉冲控制即可)。

3位3位5位4位3位2位

X

目的操作数源操作数运算操作移动操作直接控制判别下址字段

编码表如下:

目的操作数字段

源操作数字段

运算操作字段

移位门字段

直接控制字段

001a,LDR0

010b,LDR1

011c,LDR2

100d,LDR3

001e

010f

011g

100h

MS0S1S2S3

L,R,S,N

i,j,+1

13、如图B8.1表示用快表(页表)的虚实地址转换条件,快表放在相联存贮

器中,其容量为8个存贮单元,问:

(1)当CPU按虚地址1去访问主存时主存的实地址码是多少?

(2)当CPU按虚地址2去访问主存时主存的实地址码是多少?

(3)当CPU按虚地址3去访问主存时主存的实地址码是多少?

页号

该页在主存中的起始地址

虚拟地址页号页内地址

33

25

7

6

4

15

5

30

42000

38000

96000

60000

40000

80000

50000

70000

1

2

3

15

0324

7

0128

48

0516

图B8.1

13、解:

(1)用虚拟地址为1的页号15作为快表检索项,查得页号为15的页在主存中

的起始地址为80000,故将80000与虚拟地址中的页内地址码0324相加,

求得主存实地址码为80324。

(2)主存实地址码=96000+0128=96128

(3)虚拟地址3的页号为48,当用48作检索项在快表中检索时,没有检索到页号为48的页面,此时操作系统暂停用户作业程序的执行,转去执行查页表程序。

如该页面在主存中,则将该页号及该页在主存中的起始地址写入主存;如该页面不存在,则操作系统要将该页面从外存调入主存,然后将页号及其在主存中的起始地址写入快表。

14、用时空图法证明流水CPU比非流水CPU具有更大的吞吐率。

解:

(1)时空图法:

假设指令周期包含四个子过程:

取指令(IF)、指令译码(ID)、执行运算(EX)、结果写回(WB),每个子过程称为过程段(Si),这样,一个流水线由一系列串连的过程段组成。

在统一时钟信号控制下,数据从一个过程段流向相邻的过程段。

S1S2S3S4

(a)指令周期流程

图C18.3

图C18.2(b)表示非流水CPU的时空图。

由于上一条指令的四个子过程全部执行完毕后才能开始下一条指令,因此每隔4个单位时间才有一个输出结果,即一条指令执行结束。

图C18.2(c)表示流水CPU的时空图。

由于上一条指令与下一条指令的四个过程在时间上可以重叠执行,因此,当流水线满载时,每一个单位时间就可以输出一个结果,即执行一条指令。

比较后发现:

流水CPU在八个单位时间中执行了5条指令,而非流水CPU仅执行2条指令,因此流水CPU具有更强大的数据吞吐能力。

15、CPU结构如图B9.1所示,其中有一个累加寄存器AC,一个状态条件寄存器,各部分之间的连线表示数据通路,箭头表示信息传送方向。

(1)标明图中四个寄存器的名称。

(2)简述指令从主存取到控制器的数据通路。

(3)简述数据在运算器和主存之间进行存/取访问的数据通路。

图B9.1

15、解:

(1)a为数据缓冲寄存器DR,b为指令寄存器IR,c为主存地址寄存器,d为程序计数器PC。

(2)主存M→缓冲寄存器DR→指令寄存器IR→操作控制器。

(3)存储器读:

M→DR→ALU→AC

存储器写:

AC→DR→M

16、已知cache/主存系统效率为85%,平均访问时间为60ns,cache比主存快4倍,求主存储器周期是多少?

cache命中率是多少?

16、解:

因为:

ta=tc/e所以:

tc=ta×e=60×0.85=510ns(cache存取周期)

tm=tc×r=510×4=204ns(主存存取周期)

因为:

e=1/[r+(1–r)H]

所以:

H=2.4/2.55=0.94

17、某计算机的数据通路如图B10.2所示,其中M—主存,MBR—主存数据寄存器,MAR—主存地址寄存器,R0-R3—通用寄存器,IR—指令寄存器,PC—程序计数器(具有自增能力),C、D--暂存器,ALU—算术逻辑单元(此处做加法器看待),移位器—左移、右移、直通传送。

所有双向箭头表示信息可以双向传送。

请按数据通路图画出“ADD(R1),(R2)+”指令的指令周期流程图。

该指令的含义是两个数进行求和操作。

其中源操作地址在寄存器R1中,目的操作数寻址方式为自增型寄存器间接寻址(先取地址后加1)。

图B10.2

17、解:

“ADD(R1),(R2)+”指令是SS型指令,两个操作数均在主存中。

其中源操作数地址在R1中,所以是R1间接寻址。

目的操作数地址在R2中,由R2间接寻址,但R2的内容在取出操作数以后要加1进行修改。

指令周期流程图如图B10.4

18、CPU执行一段程序时,cache完成存取的次数为5000次,主存完成存

取的次数为200次。

已知cache存取周期为40ns,主存存取周期为160ns。

求:

(1)Cache命中率H

(2)Cache/主存系统的访问效率e

(3)平均访问时间Ta。

解:

(1)命中率H=Nc/(Nc+Nm)=5000/(5000+2000)=5000/5200=0.96

(2)主存慢于cache的倍率R=Tm/Tc=160ns/40ns=4

访问效率:

e=1/[r+(1-r)H]=1/[4+(1-4)×0.96]=89.3%

(3)平均访问时间Ta=Tc/e=40/0.893=45ns

19、某程序对页面要求的序列为P2P3P1P5P3P2P6P3P2P5P2P3P7P3P5,设主存容量为4个页面,求FIFO和LRU替换算法时各自的命中率(假设开始时主存为空)。

要求给出过程。

答:

FIFO和LRU替换算法的命中率各占4分

页面请求

2

3

1

5

3

2

6

3

2

5

2

3

7

3

5

F

I

F

O

④

2

2

2

2

2

2

3

3

1

1

1

5

6

6

2

③

3

3

3

3

3

1

1

5

5

5

6

2

2

3

②

1

1

1

1

5

5

6

6

6

2

3

3

7

①

5

5

5

6

6

2

2

2

3

7

7

5

命中

×

×

×

×

√

√

×

√

×

√

√

×

×

√

×

L

R

U

④

2

2

2

2

2

1

5

5

5

6

6

6

5

5

2

③

3

3

3

1

5

3

2

6

3

3

5

2

2

7

②

1

1

5

3

2

6

3

2

5

2

3

7

3

①

5

3

2

6

3

2

5

2

3

7

3

5

命中

×

×

×

×

√

√

×

√

√

√

√

√

×

√

√

FIFO替换算法的命中率=6/15=40%

LRU替换算法的命中率=9/15=60%

19、微程序共有58条微指令,20个微命令(直接控制),6个微程序分支,请画出微程序控制器组成框图,描述各部分功能。

解:

根据题意,微指令格式如下:

微命令字段(20位)

P字段(3位)

下址字段(6位)

由此可画出微程序组成框图如下:

图C15.1

20、图中所示的处理机逻辑框图中,有两条独立的总线和两个独立的存储器。

已知指令存储器IM最大容量为16384字(字长18位),数据存储器DM最大容量是65536字(字长16位)。

各寄存器均有“打入”(Rin)和“送出”(Rout)控制命令,但图中未标注出。

指出下列各寄存器的位数:

程序计数器PC,指令寄存器IR,累加器AC0和AC1,通用寄存器R0—R3,指令存储器地址寄存器IAR,指令存储器数据寄存器IDR,数据存储器地址寄存器DAR,数据存储器数据寄存器DDR。

图C17.1

解:

PC=14位IR=18位

AC0=AC1=16位R0—R3=16位

IAR=14位IDR=18位

DAR=16位DDR=16位

21、主存储器容量为2MB,虚存容量为1GB(1×109B),问:

(1)虚拟地址和物理地址各为多少位?

(2)根据寻址方式计算出来的有效地址是虚拟地址还是物理地址?

(3)如果页面大小为4kB,页表长度是多少?

解:

(1)虚拟地址为30位(2分),物理地址为21位(2分)

(2)虚拟地址(2分)

(3)页表长度为218(4分)