封装测试流程.docx

《封装测试流程.docx》由会员分享,可在线阅读,更多相关《封装测试流程.docx(42页珍藏版)》请在冰豆网上搜索。

封装测试流程

第1章前言

1.1半导体芯片封装的目的

半导体芯片封装主要基于以下四个目的[10,13]:

●防护

●支撑

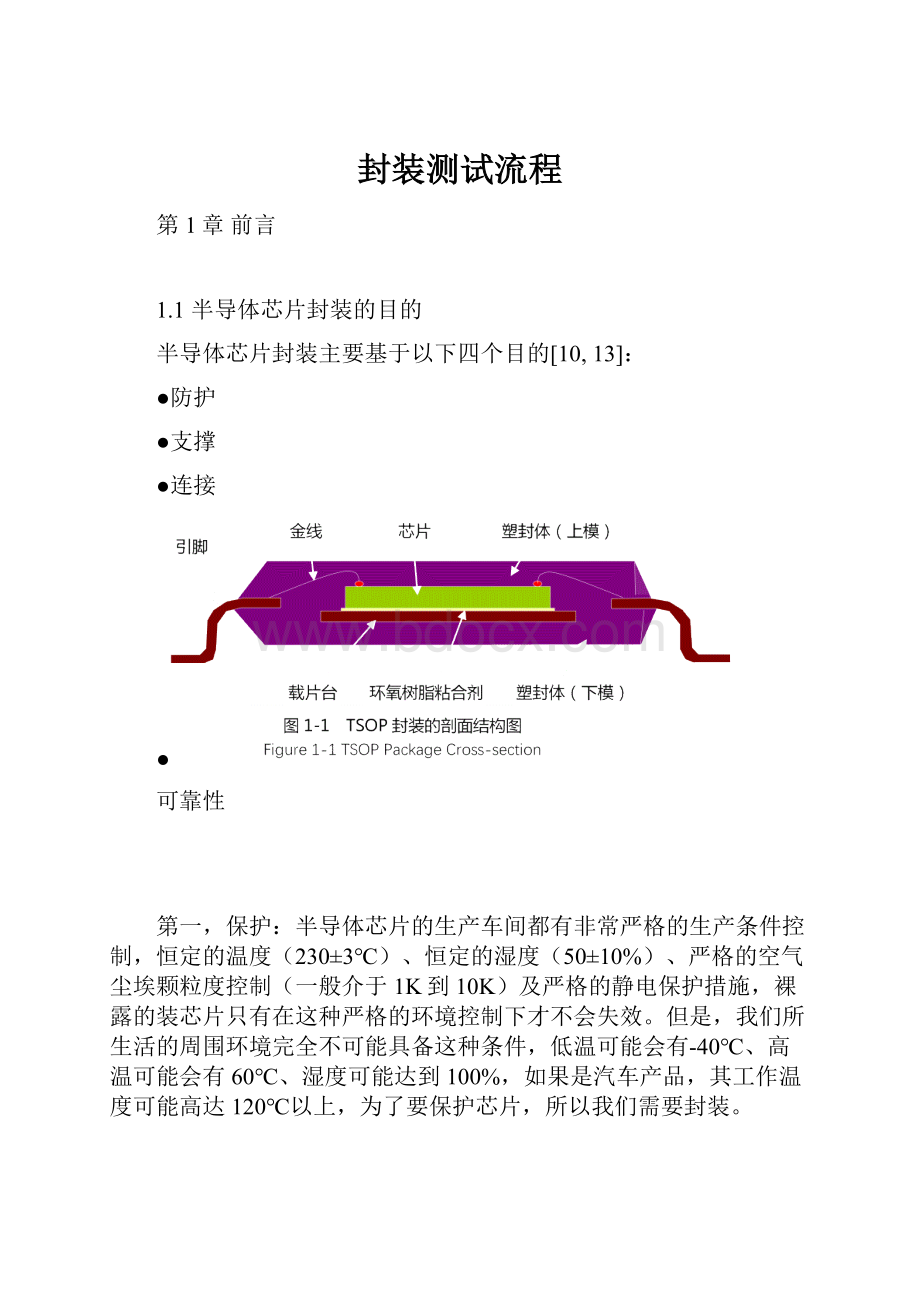

●连接

●

可靠性

第一,保护:

半导体芯片的生产车间都有非常严格的生产条件控制,恒定的温度(230±3℃)、恒定的湿度(50±10%)、严格的空气尘埃颗粒度控制(一般介于1K到10K)及严格的静电保护措施,裸露的装芯片只有在这种严格的环境控制下才不会失效。

但是,我们所生活的周围环境完全不可能具备这种条件,低温可能会有-40℃、高温可能会有60℃、湿度可能达到100%,如果是汽车产品,其工作温度可能高达120℃以上,为了要保护芯片,所以我们需要封装。

第二,支撑:

支撑有两个作用,一是支撑芯片,将芯片固定好便于电路的连接,二是封装完成以后,形成一定的外形以支撑整个器件、使得整个器件不易损坏。

第三,连接:

连接的作用是将芯片的电极和外界的电路连通。

引脚用于和外界电路连通,金线则将引脚和芯片的电路连接起来。

载片台用于承载芯片,环氧树脂粘合剂用于将芯片粘贴在载片台上,引脚用于支撑整个器件,而塑封体则起到固定及保护作用。

第四,可靠性:

任何封装都需要形成一定的可靠性,这是整个封装工艺中最重要的衡量指标。

原始的芯片离开特定的生存环境后就会损毁,需要封装。

芯片的工作寿命,主要决于对封装材料和封装工艺的选择。

1.2半导体芯片封装技术的发展趋势

●封装尺寸变得越来越小、越来越薄

●引脚数变得越来越多

●芯片制造与封装工艺逐渐溶合

●焊盘大小、节距变得越来越小

●成本越来越低

●绿色、环保

以下半导体封装技术的发展趋势图[2,3,4,11,12,13]:

注:

1.xSOP是指SOP系列封装类型,包括SSOP/TSOP/TSSOP/MSOP/VSOP等。

2.3D是目前用于简称叠层芯片封装的最常见缩写。

TSOP封装技术出现于上个世纪80年代,一出现就得到了业界的广泛认可,至今仍旧是主流封装技术之一。

TSOP是“ThinSmallOutlinePackage”的缩写,意思是薄型小尺寸封装。

其封装体总高度不得超过1.27mm、引脚之间的节距0.5mm。

TSOP封装具有成品率高、价格便宜等优点,曾经在DRAM存存储器的封装方面得到了广泛的应用[14]。

从本世纪初开始,国外主要的半导体封装厂商都开始了叠层芯片(3D)封装工艺的研究,几乎涉及到所有流行的封装类型,如SIP、TSOP、BGA、CSP、QFP,等等。

2005年以后,叠层芯片(3D)封装技术开始普及。

2007年,我们将看到两种全新的封装类型,PiP(PackageinPackage)及PoP(PackageonPackage),它们就是叠层芯片(3D)封装技术广泛应用的结果。

1.3叠层芯片封装技术概述

叠层芯片封装技术,简称3D,是指在不改变封装体的尺寸的前提下,在同一个封装体内于垂直方向叠放两个或两个以上的芯片的封装技术,它起源于快闪存储器(NOR/NAND)及SDRAM的叠层封装。

叠层芯片封装技术对于无线通讯器件、便携器件及存储卡来讲是最理想的系统解决方案。

近年来,手机、PDA、电脑、通讯、数码等消费产品的技术发展非常快,这此行业的迅猛发展需要大容量、多功能、小尺寸、低成本的存储器、DSP、ASIC、RF、MEMS等半导体器件,于是叠层芯片技术于近几年得到了蓬勃发展[1]。

3D封装技术的有以下几个优点:

●多供能、高效能

●大容量高密度,单位体积上的功能及应用成倍提升

●低成本

例如,DRAM/NAND,为了增大单个器件的存储容量,一个通常的做法就是减小芯片的线宽、采用集成度更高的工艺,使得单芯片的容量增长。

不过,减小线宽,一是带来晶圆带来生产成本的上升,二是技术难度也会相应加大。

如果提高封装密度,即采用叠层芯片封装技术,同样可以将单个器件的容量成倍提升,但是生产成本的上升、工艺难度都比前者低,这就是为什么需要发展叠层芯片封装工艺的根本原因。

在一个封装体内放入两个芯片就可以将单个器件的容量提高一倍,这种方法要比我们提高集成度要简单得多。

举个例子,假如采用57nm工艺的单芯片的容量是1G,如果提升到2G则需要使用45nm的集成度,但是,目前市场上有大量的2GSD卡出售并未采用45nm的工艺,这就是得益于叠层芯片封装技术,即在一个器件内封装入两个芯片。

当然,如果将提高芯片的集成度结合叠层芯片技术,则就能得到更高的单个器件容量。

1.4TSOP叠层芯片技术研究和重要性和意义

TSOP封装曾经广泛应用于早期的动态随机存储器(DRAM)中。

由于TSOP封装的信号传输长度较长、不利于速度提升,容积率只有TinyBGA的50%,在DDR/DDRRII内存封装中被TinyBGA所取代。

但是,随着NAND快闪存储器的兴起,它了重新焕发了生机。

根据ICInsight所公布的报告,2005年NAND快闪存储器的增长率达64%,其增长率是整个半导体市场4%的增长率的16倍。

2006年NAND快闪存储器的增长率虽然放缓,但仍高达30%左右,是2006年整个半导体市场的增长率8%的3倍多。

根据市场调查机构DRAMeXchange的最新的2007年第三季NANDFlash营收市场占有率报告,NANDFlash品牌厂商在2007年第三季整体营收表现抢眼,逼近39亿美元,比第二季成长36.8%。

NAND的市场增长率远大于整个半导体市场的增长率,所以与NAND相关的主要封装类型TSOP及SiP的会继续高速增长。

正是基于强劲的市场需求,所以大力发展TSOP叠层芯片封装就显得十分重要。

对NAND而言,其两大主流封装形式是SiP及TSOP。

SiP的优点是一次成形,封装完成即是成品,不需要SMD。

和SiP相比,TSOP则更具有柔韧性,因为TSOP可能通过SMD制作成SD卡、MiniSD卡、CF卡或是集成到MP3/MP4、SDRAM中,而SiP则不具有这种特点,SiP一旦完成组装,它就是成品了、不能再根据市场需求来进行调整。

和另一种同样可以通过SMD组装的PBGA封装形式相比,TSOP具有非常明显的成本优势。

正是因为TSOP的成本优势,半导体业的巨头Intel将它的NAND/NORPBGA封装转成了TSOP封装。

而且,Intel还通过和Micron的合资公司IMFT(IMFlashTechnology),大力推进NANDTSOP的生产。

据称,苹果电脑公司目前在iPod中使用的NAND闪存芯片占全部NAND闪存芯片产量的20%。

作为闪存定单,苹果电脑公司已经同意支付5亿美元平分给英特尔公司和美光科技公司,2007年合资公司生产的25%的NAND闪存将提供给苹果电脑公司。

TSOP封装的封装材料成本大概占总成本的55%,如果采用叠层芯片封装,封装成本增加主要是金线和环氧树脂芯片粘合,因此只需要增加少量成本就能将单位封装体积上的功能及应用成倍提升,不光如此,它还带来后序工序的成本降低。

叠层芯片技术是一项非常重要的技术,它的兴起带了封装技术的一场革命。

因此,TSOP叠层芯片封装技术的研究有十分深远的历史及现实意义。

第2章单芯片TSOP封装技术介绍

芯片封装工艺分为两段,分别叫前道(Front-of-line,FOL)和后道(End-of-line,EOL),前道(FOL)主要是将芯片和引线框架(Leadframe)或基板(Substrate)连接起来,即完成封装体内部组装。

后道(EOL)主要是完成封装并且形成指定的外形尺寸[7]。

2.1前道生产工艺

第九步,检查键合后的质量。

第八,引线键合。

第七步,烘烤。

第六步,贴片。

第五步,再次检查芯片的质量。

第四步,划片,将晶圆上的芯片彼此分离。

第三步,装片。

第二步,磨片结束后,对芯片进行质量检查。

第一步,磨片。

下面,用示意图来简单介绍主要的加工工艺:

1.晶圆(wafer):

图-3展示了一个从晶圆厂(WaferFab)出来的晶圆,上面布满了矩形的芯片,有切割槽的痕迹。

2.磨片(Backgrinding):

晶圆出厂时,其厚度通常都在0.7mm左右,比封装时的需要的厚度大很多,所以需要磨片。

图-4是磨片工艺示意图,晶圆被固定在高速旋转的真空吸盘工作台上,高速旋转的砂轮从背面将晶圆磨薄,将晶圆磨到指定的厚度。

通常,TSOP单芯片封装的晶圆厚度为0.28mm左右。

高速旋转的砂轮

真空吸盘工作台

图2-2晶圆背面剪薄工艺示意图

Figure2-2BackgrindingProcess

3.装片(WaferMount):

图2-3装片工艺示意图

Figure2-3WaferMountProcess

图-5装片工艺,上图展示了如何将晶圆粘贴到粘性蓝膜上。

首先将晶圆正面朝下固定在工作台的真空吸盘上,然后铺上不锈刚晶圆固定铁环(WaferRing),再在铁环上盖上粘性蓝膜(BlueTape),最后施加压力,把蓝膜、晶圆和铁环粘合在一起。

图-5下图展示了将晶圆固定在铁环上以后的情况:

中央的晶圆被固定在蓝膜上,蓝膜被固定在不锈钢铁环上,以便后续工序加工。

4.划片(DieSawing):

图2-4划片工艺示意图

Figure2-4WaferSawingProcess

图-6划片工艺,上图表示高速旋转的金刚石刀片在切割槽中来回移动,将芯片分离。

图-6下图是完成切割的晶圆,芯片被沿着切割槽切开。

5.贴片(DieAttach):

图-7a,芯片粘贴工艺,第一步:

顶针从蓝膜下面将芯片往上顶、同时真空吸嘴将芯片往上吸,将芯片与膜蓝脱离。

吸嘴

芯片

图2-5a贴片工艺示意图

Figure2-5aDieAttachProcess

图-7b,芯片粘贴工艺,第二步:

将液态环氧树脂涂到引线框架的台载片台上。

环氧树脂混合液

图2-5b贴片工艺示意图

Figure2-5bDieAttachProcess

图-7c,芯片粘贴工艺,第三步:

将芯片粘贴到涂好环氧树脂的引线框架上。

图2-5c贴片工艺示意图

Figure2-5cDieAttachProcess

6.引线键合(WireBonding):

图-8是用金线将引线框架的引脚和芯片的焊盘连接起来以后的示意,上图是截面图,下图俯视图。

引脚

金线

环氧树脂

载片台

图2-6芯片完成焊接后的示意图

Figure2-6AfterWireBonding

有关引线键合部份的工艺介绍,请参见4.3。

2.2后道生产工艺:

对外观及引脚进行100%检查。

用机械模具将器件冲压成形。

打上器件的身份识别。

镀锡后,对锡层进行高温老化处理。

在引脚外镀上一层纯锡,增强导电性能。

继续对环氧树脂封装体进行高温老化处理。

此工序主要是切断引脚之间的连筋。

用环氧树脂将芯片及用于承载芯片的引线框架一起封装起来,保护芯片。

1.塑封(Molding):

塑封是用环氧树脂将芯片及用于承载芯片的引线框架一起封装起来,保护芯片,并形成一定等级的的可靠性。

模具(上模)

模具(下模)

固体环氧树脂饼料

已经完成前道生产工序的引线框图架

模腔(通常上下模均有)

图2-7a封装工艺示意图

Figure2-7aMoldingProcess

图2-7b封装工艺示意图

Figure2-7bMoldingProcess

图-9a展示了塑封工序的工作原理。

模具分成上下模,模具上有根据封装体尺寸所预先定好的模腔,其工作温度在通常在165-185℃范围内。

将需要封装的引线框架放置到模具上,然后放入固体环氧树脂饼料,再合上模具并施加合模压力(至少在30吨以上)。

合模后,给注塑杆上施加压力,环氧树脂在高度高压下开始液化,于是在注塑杆的作用下,环氧树脂被挤入模腔中。

由于环氧树脂的特性是先液化再固化,于是在被挤入腔中后,它将再次固化,形成我们所需要的外形尺寸。

图-9b是注塑完成以后的示意,左图是俯视图,右图剖面图。

2.切筋(Trim):

图-10是切筋以后的情况,对比图-9b我们可以发现,引脚之间的连筋已经没有了。

切筋的作用是将引脚之间的连筋切开,以方便成形工艺。

图2-8切筋工艺示意图

Figure2-8TrimProcess

3.电镀(Plating):

图-11是电镀以后的情况,对比图-10我们可以发现,引脚之间的颜色有了变化。

电镀的作用是增强导电性能。

图2-9电镀工艺示意图

Figure2-9PlatingProcess

4.成形(Form):

图-12成形工艺示意图,引脚的外形是由冲压模具来完成,器件被固定在模具上,刀具从上往冲压成形,然后将器件与引线框架分离,得到图-1中的外形。

成形工艺是半导体封装的最后一步,其外形尺寸有严格的行业标准,TSOP封装的具体尺寸请参见JEDECMO-142,THINSMALLOUTLINEPACKAGEFAMILYTYPEI,现行标准公布于2000年7月[5]。

TSOP封装的总高度不得超过1.27mm、引脚节距0.5mm,塑封体厚度为1.0mm,目前最流行的TSOP48的长X宽=12X20。

图2-10成形工艺示意图

Figure2-10FormProcess

第3章实验环境、设备及材料

实验环境为温度23+/-3摄氏度、湿度50+/10%。

表-1是实验设备清单,表-2是实验材料清单。

表3-1实验采用的设备清单

工艺

设备

单芯片封装

叠层芯片封装

磨片(B/G)

磨片机

DISCODFG-850

TSKPG300

装片(W/M)

装片机

TAKATORIATM-8100

TSKPG300

划片(D/S)

划片机

DISCODFD640/651

TSKA-WD-300,DISCODFD6361,DISCODFD651

贴片(D/A)

贴片机

ESEC2007/2008HS

ESEC2008XP

ASMAD889

ASMAD8912

引线键合(W/B)

金线焊接机

SHINKAWAUTC-250

SHINKAWAUTC1000/2000

K&S8028

K&S8028PPS及以上型号

表3-2实验采用的材料清单

工艺

材料类型

单芯片封装

叠层芯片封装

装片(W/M)

贴片胶带

蓝膜

蓝膜或环氧树脂薄膜胶带(EpoxyFilmTape)

贴片(D/A)

环氧树脂

混合银浆

混合银浆及环氧树脂薄膜(EpoxyFilm)

贴片(D/A)

引线框架

铜引线框架

铜引线框架或合金引线框架

引线键合(W/B)

金线

纯度99.99%金线

塑封(MOLD)

塑封料

住友电木,EME-G700

住友电木,EME-G700V

电镀(PLATING)

电镀溶液

纯锡电镀液

第4章TSOP叠层芯片封装技术的实现

首先介绍叠层芯片封装的识别,比如,“TSOP2+1”就是指一个TSOP封装体内有两个活性芯片(ActiveDie)、一个空白芯片(Spacer),“VFBGA3+0”,那就是说一个VFBGA封装体内有三个活性芯片、没有空白芯片,以此类推。

下图是最典型的TSOP2+1的封装形式剖面图,上下两层是真正起作用的芯片,中间一层是为了要给底层芯片留出焊接空间而加入的空白芯片。

空白芯片由单晶硅制成,里面没有电路。

上层芯片

中间空白芯片

环氧树脂层

图4-1TSOP2+1

Figure4-1TSOP2+1

下层芯片

4.1三种实现叠层芯片的封装的工艺

叠层芯片封装技术不改变封装体的尺寸,因此后道生产工艺不会有改变,我所有的研究都集中在对前道生产工艺的改进。

下面,我以简单两层芯片的TSOP2+X为例,介绍对前道生产工艺完成的研究。

4.1.1第一种方法,TSOP2+1,使用多次重复单芯片的工艺

通过实验,我发现可以通过重复单芯片的工艺来实现叠层芯片的封装,其工艺流程如下[8]:

烘烤芯片,使上层芯片完全固定在空白芯片上

完成上层芯片的键合

目视检查,保证上述各个工序的质量

烘烤芯片,使空白芯片完全固定在下层芯片上

用银浆将中间空白芯片贴下层芯片上

用银浆将下层芯片贴在引线框架上

烘烤芯片,使下层芯片完全固定在引线框架上

用银浆将上层芯片贴空白芯片上

完全下层芯片的键合

采用重复传统的单芯片生产工艺实现叠层芯片封装时,只需要在贴片(D/A)及引线键合(W/B)两道工序之间往返即可。

上述的TSOP2+1,需要三次贴片(D/A)、两次引线键合(W/B)。

第一种方法,看似非常简单,其实不然。

液态环氧树脂的流动性较强,非常容易扩散,经常出现树脂层不均匀,因此需要非常好的液态环氧树脂喷涂机构,而且,它还有一个非常致命的缺陷,即容易在封装完成后出现芯片破裂(DieCrack),并且这种芯片破裂只会出现在叠层芯片封装中。

关于芯片破裂的解决方案,我将在4.2中阐述。

4.1.2第二种方法,TSOP2+1,使用环氧树脂薄膜作为芯片贴合剂

由于液态环氧树脂有流动性强、不易受控的缺点,为了解决这个问题,于是我又尝试改变原材料的形态,用固态环氧树脂薄膜替代液态环氧树脂。

下图是使用固态环氧树脂薄膜胶带替代普通蓝膜后装片工序的情形,薄膜胶带上的白色圆盘即固态环氧树脂薄膜,其尺寸比晶圆直径稍大。

装片完成后,环氧树脂薄膜就已经和芯片粘在了一起:

图4-2采用环氧树脂薄膜时的装片工艺示意图

Figure4-1EpoxyFilmTapeWaferMountProcess

用固态环氧树脂薄膜替代液态环氧树脂混合液,其好处是在贴片工序时我们只需要将芯片贴到引线框架上,不需要喷涂液态环氧树脂,这就大大简化了工艺。

工艺流程如下[8]:

目视检查,保证上述各个工序的质量

完成上层芯片的引线键合

用环氧树脂薄膜将上层芯片贴在空白芯片上

完成下层芯片的引线键合

用环氧树脂薄膜将下层芯片贴到引线框架上

烘烤,将下层芯片完全固定在引线框架

用环氧树脂薄膜将空白芯片贴到下层芯片上

在第一种方法中,为了增加环氧树脂和引线框架之间或芯片的粘结力,每完成一次贴片之后都需要烘烤。

但是,第二种方法,由于固态环氧树脂薄膜和芯片之间的粘结力已经足够,只需要做一次烘烤即可,生产工艺简单、生产周期比第一种方法短,而且,由于多次烘烤会造成引线框架氧化及芯片粘污,烘烤次数减少对提高成品率和减少可靠性失效也很有好处。

4.1.3第三种方法,TSOP2+0

为了进一步简化工艺,于是,在第二种方法的基础上,通过改变芯片的焊盘布局、将焊盘都放置在芯片的一端,去掉中间的空白芯片,于是得到了第三种方法,如下图所示,仅一端有焊线[8]。

图4-3TSOP2+0

Figure4-3TSOP2+0

目视检查,保证上述各个工序的质量

用环氧树脂薄膜将下层芯片贴到引线框架上

烘烤,将芯片完全固定在引线框架上

完全引线键合

用环氧树脂薄膜将上层芯片贴在下层芯片上

第三种方法,如果贴片机可以同时完成多次贴片,则工序就更加简单,和单芯片封装一样、仅需要一次贴片、一次引线键合,而且,由于不需要液态环氧树脂的喷涂机构,贴片工序甚至比单芯片封装还好简单。

这样的改进,使得叠层芯片封装的优势非常明显:

工艺简单、成本低、成品率高、易于推广。

4.1.4三种方法的对比

通过反复实验对比,对上述三种实现两芯片叠层(TSOP2+X)封装工艺的优缺点总结如下:

表4-1三种工艺的对比

叠层芯片工艺

贴片工艺难度

键合工艺难度

成品率

生产周期

单颗封装成本

其它

采用传统工艺,使用液态银浆作为芯片粘合剂

难

难

低

长

低

不需要改变芯片制作工艺

采用环氧树脂薄膜作为粘合剂,两次引线键合

简单

难

一般

一般

一般

不需要改变芯片制作工艺

采用环氧树脂薄膜作为粘合剂,一次引线键合

简单

简单

高

短

低

需要改变芯片焊盘的布局

上述三种叠层芯片的封装工艺,第一种,使用环氧树脂银浆,成本低,但是工艺难度很高、成品率低,成品率能达到99.5%就几乎不可能再提升了。

第二种,虽然环氧树脂薄膜成本高,但是由于环氧树脂薄膜是在装片(W/M)的时候粘贴到芯片背面,不必考虑液态环氧树脂工艺的复杂性,所以工艺比第一种简单、生产周期相应缩短,成品率也较、成品率可达99.8-99.9%,其缺点是焊接工序比较复杂。

第三种,由于只有两次贴片(D/A)、一次引线键合(W/B),所以不仅工艺简单、成本低,而且成品率极高、可以稳定在99.90%以上。

当然,第三种工艺有局限性,需要改变芯片的制作布局,将焊盘布置在芯片的一端。

第一种方法虽然工艺复杂、成本率低,但是由于液态环氧树脂成本比固态环氧树脂膜薄低,仍然具有其实际推广价值;第三种方法虽然最值得推广,但在实际应用中可能会因为芯片的布局难以改变而不能使用,所以,实际应用广泛采纳的是第二种方法。

4.2使用液态环氧树脂银浆作为粘合时的芯片破裂(DieCrack)的解决

采用液态环氧树脂银浆作为芯片粘合剂,其最难解决的技术问题是如何解决塑封工序以后的芯片破裂问题,其破裂呈现出网状:

图4-4芯片破裂

Figure4-4DieCrackPattern

在单芯片封装中,不会出现这样的芯片,通常我们在单芯片封装中看到大多都是一条或几条裂纹,而且是在贴片工序后我们就能通过目视检查出。

而这种多芯片的网状芯片破裂,是出现在塑封(MOLDING)以后而不是贴片工序。

塑封结束后,通常需要采用有损检查(即开盖)才能发现芯片破裂。

在这个案例中,开盖检查虽然能发现上层芯片的问题,但是对于下层芯片照样很难看到,所以就很难知道什么情况下会发生芯片破裂,也就很难解决这个问题。

而且,开盖是一种有损检查,采用强酸将芯片上面的环氧树脂腐蚀掉,将芯片重新裸露在外,显然不能用于生产中来。

首先分析这种芯片破裂(DieCrack)发生的机理。

图4-5芯片破裂原理示意图

Figure4-5PrincipleofWhyDieCrackHappened

在叠层芯片封装中,由于液态环氧树脂的流动性强,所以在贴片工艺中,通常难以保证环氧树脂能够完全充满两层芯片之间的空隙,如上图所示。

通常,半导体业界的一般标准是75%和覆盖率就算合格。

注塑工序所使用的环氧树脂,主要由25-100um的颗粒组成。

通常,我们在贴片(D/A)形成的环氧树脂层的厚度介于12-38um,这就意味着,只有少量小颗粒的注塑工序所使用的环氧树脂混合物可以进入这层空间,而大量大颗粒则只能在外围。

于是,在注塑过程中,由于我们在施加很大的压力(通常压强在10MPa左右),由于中间的空隙不能被塑封料填充,于是芯片就在外力的作用下被压碎。

这就是使用液态环氧树脂作为芯片粘合剂时为什么会在注塑工序完成后会有网状的芯片破裂(DieCrack)的原因。

单芯片封装中,由于芯片度较大,所以即使就空洞,也没会出现