四位二进制加法计数器课程设计.docx

《四位二进制加法计数器课程设计.docx》由会员分享,可在线阅读,更多相关《四位二进制加法计数器课程设计.docx(21页珍藏版)》请在冰豆网上搜索。

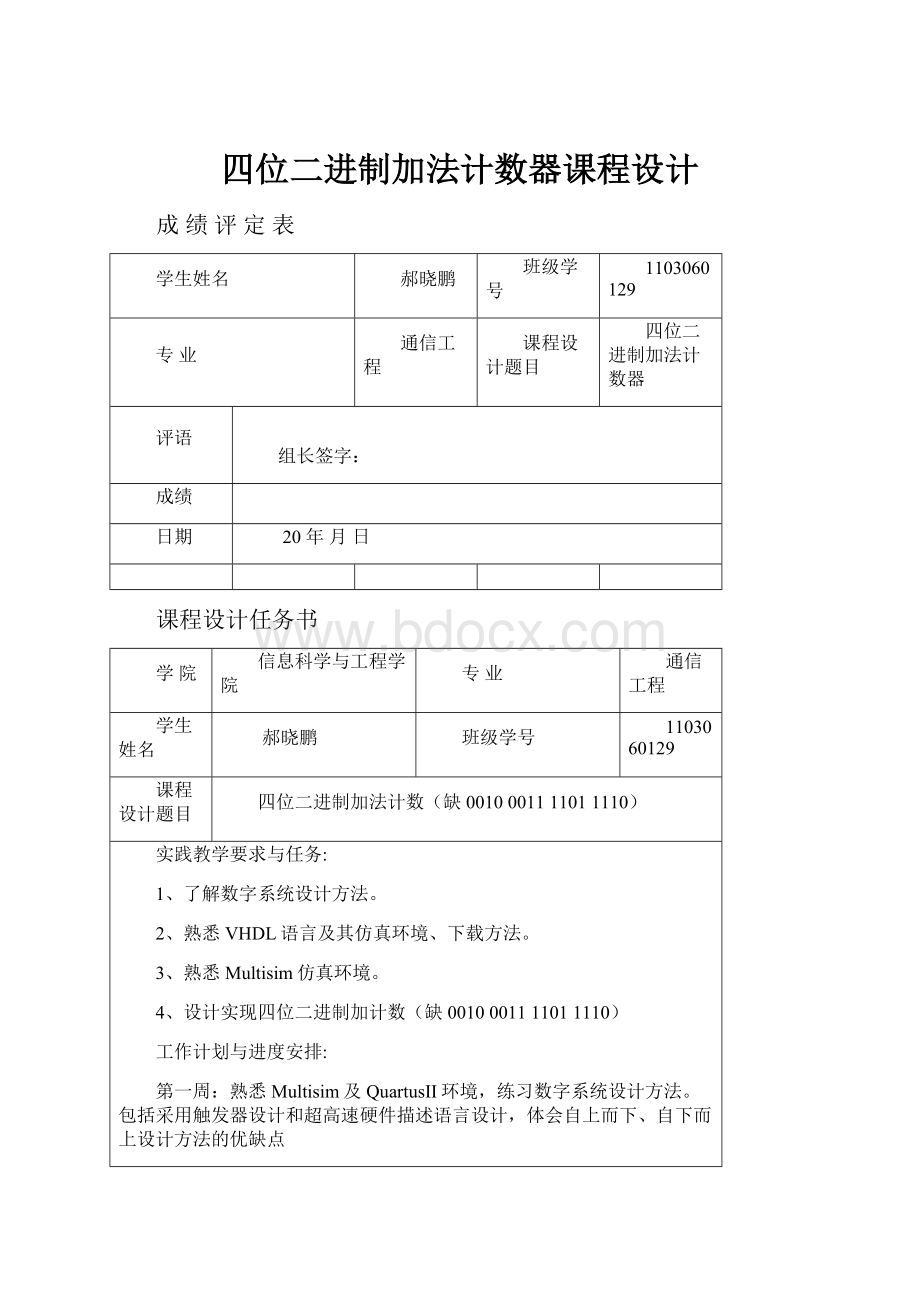

四位二进制加法计数器课程设计

成绩评定表

学生姓名

郝晓鹏

班级学号

1103060129

专业

通信工程

课程设计题目

四位二进制加法计数器

评语

组长签字:

成绩

日期

20年月日

课程设计任务书

学院

信息科学与工程学院

专业

通信工程

学生姓名

郝晓鹏

班级学号

1103060129

课程设计题目

四位二进制加法计数(缺0010001111011110)

实践教学要求与任务:

1、了解数字系统设计方法。

2、熟悉VHDL语言及其仿真环境、下载方法。

3、熟悉Multisim仿真环境。

4、设计实现四位二进制加计数(缺0010001111011110)

工作计划与进度安排:

第一周:

熟悉Multisim及QuartusII环境,练习数字系统设计方法。

包括采用触发器设计和超高速硬件描述语言设计,体会自上而下、自下而上设计方法的优缺点

第二周:

1.在QuartusII环境中仿真实现四位二进制加计数(缺0100010110011010)。

2.在Multisim环境中仿真实现四位二进制加计数,缺(0100010110011010),并通过虚拟仪器验证其正确性。

指导教师:

201年月日

专业负责人:

201年月日

学院教学副院长:

201年月日

摘要

本文采用在MAXPLUSⅡ环境中用VHDL语言实现四位二进制加法计数(缺0010001111011110),在仿真器上显示结果波形,并下载到目标芯片上,在实验箱上观察输出结果。

在Multisim环境中仿真实现四位二进制加法计数器(缺0010001111011110),并通过虚拟仪器验证其正确性。

关键词:

MAXPLUSⅡ环境;VHDL语言;四位二进制加计数;Multisim环境

一课程设计目的

(1)熟悉Multisim环境及QuartusⅡ环境,练习数字系统设计方法,包括采用触发器设计和超高速硬件描述语言设计,体会自上而下、自下而上设计方法的优缺点。

(2)在QuartusⅡ环境中用VHDL语言实现四位二进制加计数器(缺0010001111011110)的建立,在仿真器上显示结果波形,并下载到目标芯片上,在实验箱上观察输出结果。

(3)在Multisim环境中仿真实现四位二进制加计数器(缺001000111101

1110)的建立,并通过虚拟仪器验证其正确性。

二课设题目实现框图

在本课程设计中,四位二进制加计数用四个CP下降沿触发的JK触发器实现,其中有相应的跳变,即跳过了0010001111011110四个状态,这在状态转换图中可以清晰地显示出来。

图2状态转换图

三实现过程

1.VHDL

1.1建立工程

启动QUARTUS后的界面如图3-1所示,首先需要创建一个工程,具体操作过程如下:

图3-1QUARTUS软件的启动界面

(1)点击File–>NewProjectWizard创建一个新工程,系统显示如图3-2;

图3-2工程创建向导的启始页

(2)点击Next,为工程选择存储目录、工程名称、顶层实体名等,如图3-3所示;

图3-3输入工程名称、存储目录

(3)点击Next,若目录不存在,系统可能提示创建新目录,如图3-4所示,点击“是”按钮创建新目录,系统显示如图3-5所示;

图3-4提示是否创建新文件夹

(4)系统提示是否需要加入文件,在此不添加任何文件,点击Next,进入设备选择对话框,如图3-6,这里选中实验箱的核心芯片CYCLONE系列FPGA产品EP1C6Q240C8;

图3-5提示是否添加文件

图3-6芯片型号选择

(5)点击Next,系统显示如图3-7,提示是否需要其他EDA工具,这里不选任何其他工具;

(6)点击Next后,系统提示创建工程的各属性总结,若没有错误,点击Finish,工程创建向导将生成一个工程,这时软件界面如图3-8,在窗口左侧显示出设备型号和该工程的基本信息等。

图3-7提示是否利用其他EDA设计工具

图3-8工程阐述汇总

1.2VHDL源程序

(1)点击File->New创建一个设计文件,选择设计文件的类型为VHDLFile系统显示如图3-9,点击OK,系统显示如图3-10,窗口右侧为VHDL的编辑窗口;

图3-9创建一个设计文件

图3-10新建的一个VHDL源文件的编辑窗口

(2)在编辑窗口中编辑以下程序:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

entityzs_2is

PORT(cp,r:

INSTD_LOGIC;

q:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

endzs_2;

ARCHITECTUREBehavioralOFzs_2IS

SIGNAL

count:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(cp,r)

BEGIN

ifr='0'thencount<="0000";

elsiFcp'EVENTANDcp='1'THEN

ifcount="0001"THENcount<="0100";

elsifcount="1100"THENcount<="1111";

ELSEcount<=count+1;

ENDIF;

endif;

ENDPROCESS;

q<=count;

ENDBehavioral;

(3)输入程序后,存盘,如图3-11所示:

图3-11存盘

1.3编译及仿真过程

(1)点击Processing->StartCompilation编译该文件,系统将开始编译,结束后,给出提示信息和编译结果,如图3-12所示:

图3-12编译结果显示

(2)建立时序仿真文件,如图3-9所示,选择“VectorWaveformFile”,出现图3-13的界面,在Name空白处击右键,Insert→InsertNodeorBus。

图3-13

图3-14

在图3-14中单击

图3-15

在图3-15中单击

,再单击

→OK→OK,为仿真输入赋值。

如想赋值‘1’,单击

,仿真文件存盘时,文件名字必须与顶层文件同名,即zs_2,默认即可。

(3)单击菜单进行仿真,仿真结果如图3-16

图3-16

图3-17仿真波形

1.4引脚锁定及下载

图3-18引脚锁定

图3-19引脚下载

1.5仿结果分析

由图可知波形图中由2跳到7,再由7跳到9。

因为我的题目是四位二进制加法计数器(缺0011,0100,0101,0110,1000),所以波形仿真图波形跳变过程符合开始的设计框图。

2.电路设计

2.1设计原理

1.选择触发器

选用由于JK触发器功能齐全、使用灵活,在这里选用4个CP上升沿触发的边沿JK触发器。

2.求时钟方程、状态方程

(1)求时钟方程

采用同步方案,故取CP0=CP1=CP2=CP3=CP

CP是整个要设计的时序电路的输入时钟脉冲

(2)求状态方程

由图2所示状态转换图可直接画出如图3-20所示的电路次Q3n+1Q2n+1Q1n+1Q0n+1的卡诺图,再分解开便可以得到如图3-21所示的各触发器的卡诺图。

Q1nQ0n

Q3nQ2n

00

01

11

10

00

0001

0010

XXXX

XXXX

01

0101

0110

1000

0111

11

1111

XXXX

0000

XXXX

10

1001

1010

1100

1011

图3-20次态Q3n+1Q2n+1Q1n+1Q0n+1的卡诺图

Q1nQ0n

Q3nQ2n

00

01

11

10

00

0

0

X

X

01

0

0

1

0

11

1

X

0

X

10

1

1

1

1

(a)Q3n+1的卡诺图

Q1nQ0n

Q3nQ2n

00

01

11

10

00

0

1

X

X

01

1

1

0

1

11

1

X

0

X

10

0

0

1

0

(b)Q2n+1的卡诺图

Q1nQ0n

Q3nQ2n

00

01

11

10

00

0

0

X

X

01

0

1

0

1

11

1

X

0

X

10

0

1

0

1

(c)Q1n+1的卡诺图

Q1nQ0n

Q3nQ2n

00

01

11

10

00

1

0

X

X

01

1

0

0

1

11

1

X

0

X

10

1

0

0

1

(d)Q0n+1的卡诺图

图3-21各触发器的卡诺图

根据卡诺图进行相应化简即得到状态方程,如下:

3.求驱动方程

JK触发器的特性方程为

与特性方程做比较,可得

2.2基于Multisim设计电路图

根据所选用的触发器时钟方程、输出方程、驱动方程,便可以画出如图3-22所示的逻辑电路图。

图3-22逻辑电路图

2.3逻辑分析仪显示的波形

图3-23逻辑分析仪显示的波形

2.4仿结果分析

Multisim是一种虚拟仪器,可以用来验证电路设计的正确性。

根据相关计算,得出时序电路的时钟方程、状态方程、驱动方程,从而选择合适的触发器来连接实现。

本设计中,选用四个时钟脉冲上升沿触发的JK触发器来实现四位二进制加法计数器。

逻辑电路图中,四个小红灯即为显示器,从右到左显示时序图中的11种状态,其中,灯亮表示“1”,灭表示“0”,从而达到计数的目的。

由于其中缺少0010001111011110四种状态,所以在计数过程中会发生跳变,即从0001跳到0100,再从1100跳到1111,周而复始。

逻辑分析仪类似于ISE环境下的波形仿真,是对计数器的另一种直观的描述。

其中,高电平表示“1”,低电平表示“0”,也可以对计数器的功能进行测试及检验。

四设计体会

在本次数字电路课程设计之中,我下载了QuartusII和Multisim软件,花费许多时间回顾课本知识以及查阅资料,在两种环境下反复进行练习。

由于是第一次接触数字电路的课程设计,所以我一开始对于相关设计过程和分析方法并不太熟练。

没有形成一种逻辑分析技巧,但经过我反反复复的练习和计算,最终还是熟练掌握了对此的计算步骤以及设计方法,这一点很值得欣慰,通过本次数字电路课程设计,让我对数字电路设计有了更高层次的认识和掌握,我想这对于我以后学习相关的课程以及进行类似的设计操作会有很大的帮助,为我更深一步掌握数字电路奠定了很好的基础。

在初步设计过程中,我也出现了各种各样的问题,有些是由于我的粗心引起的,还有一些是因为我没掌握好数字的相关知识,比如在设计过程中求驱动方程,由于知识掌握不扎实出了好几次错误,但通过我不懈的努力和耐心的练习,最终求出了驱动方程,画出了逻辑电路图并且测试成功,还较好地掌握了数字电路的知识,并且很快完成了数字电路课程设计,顺利的通过了考核。

由此,我体会到,对于数字电路课程设计先要掌握好课本上的知识,还要有反复练习和理解相关原理的坚持和耐心,最终才会顺利完成本次课程设计。

通过本次数字电路课程设计,让我掌握了好多以前不知道的知识,这些收获一定会对我以后的学习和操作有很大的帮助。

五参考文献

(1)阎石主编。

数字电子技术基础(第5版),北京:

高等教育出版社,2006.05。

(2)余孟尝主编。

数字电子技术基础简明教程,北京:

高等教育出版社,2006.07。

(3)候建军编。

数字电子技术基础(第2版),北京:

高等教育出版社,2007.12。

(4)李春茂改编。

电子技术基础-Electronics(英文改编版),北京:

电子工业出版社,2005.08。

(5)弗洛伊德(Floyd,T.L.)(美)著,余璆改编。

DigitalFundamentals(NinthEdition),北京:

电子工业出版社,2008.05。

(6)罗杰主编,电子技术基础(数字部分第5版)习题全解,北京:

高等教育出版社,2008.1。