调研报告最佳范文.docx

《调研报告最佳范文.docx》由会员分享,可在线阅读,更多相关《调研报告最佳范文.docx(29页珍藏版)》请在冰豆网上搜索。

调研报告最佳范文

RAM调研与总结

、RAM调研

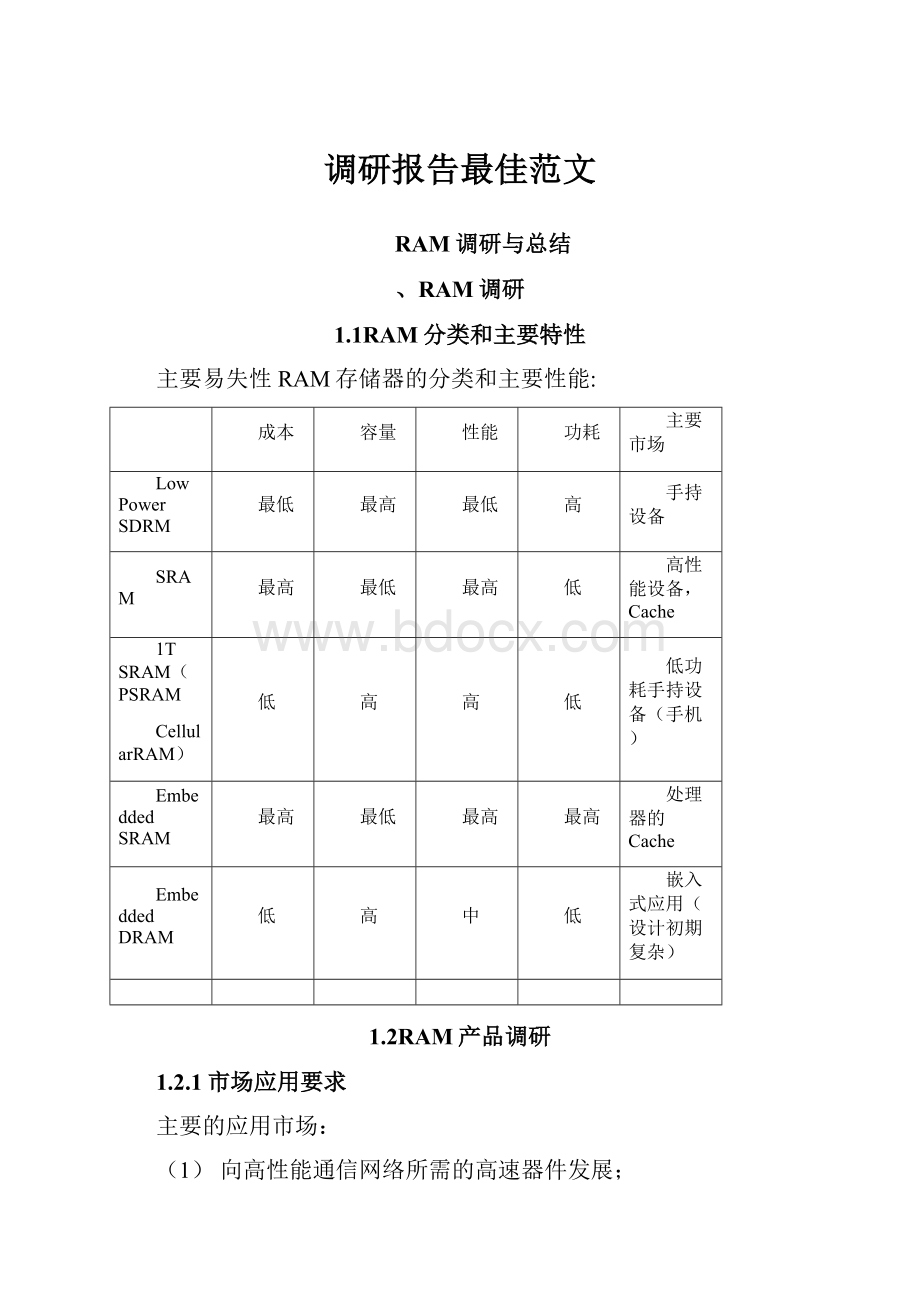

1.1RAM分类和主要特性

主要易失性RAM存储器的分类和主要性能:

成本

容量

性能

功耗

主要市场

LowPowerSDRM

最低

最高

最低

高

手持设备

SRAM

最高

最低

最高

低

高性能设备,Cache

1TSRAM(PSRAM

CellularRAM)

低

高

高

低

低功耗手持设备(手机)

EmbeddedSRAM

最高

最低

最高

最高

处理器的Cache

EmbeddedDRAM

低

高

中

低

嵌入式应用(设计初期复杂)

1.2RAM产品调研

1.2.1市场应用要求

主要的应用市场:

(1)向高性能通信网络所需的高速器件发展;

(2)降低功耗,以适应蓬勃发展的便携式应用市场;

不同的应用市场对RAM需求:

SRAM(Cache)

1TSRAM/SDRAM

容量

性能

容量

性能

ServerProcessors

4M

>3GHz

Embeddedprocessors

CellBroadbandEngineProcessors(IBM推出高端)

2M

>3GHz

MobileApplication

1一64+M

1.2.2Memory芯片公司产品分布

Memory芯片公司的产品分布情况:

表1各个产品在各个公司中的分布

\、产品

公司、、、

Async

SRAMs

Dual-port

SRAMs

Sync

SRAMs

ULP

SRAM

SDRA

M

Cellular

RAM

PSRA

M

NVM

Cypress

V

V

V

V

Micron

V

V

富士通

V

Hynix

V

Winbond

V

Powerchip

V

Kilopass

V

Mosys

V

表2各个公司的产品性能

公司

产品

性能

Cypress

AsyncSRAMs

8-35ns,4K-16M(产品数289)

Dual-portSRAMs

6-55ns,8K-32M(261)

SyncSRAMs

100-550MHZ,2M-72M(858)

ULPSRAM

45-70ns,64k-64M(276)

Micron

SDRAM

64M-512M,电源电压3.3V,时钟频率133-200MHz

CellularRAM

16M,Cutsaccesstimeinhalf,makingfirstdataavailableinaslittleas35ns

富士通

PSRAM

MB82DBS08164D:

128Mb,时钟存取时间6ns,最大工作频率

83MHz,工作电压1.8V

Hynix

PSRAM

HY64SD16645M:

4Mx16,速度70ns,

66MHz下

Winbond

PSRAM

W965A6FKA:

32Mb,65ns,-25to85C;W966A6GKA:

64Mb,65ns,-25to85C等等

Powerchip

SDRAM

64Mb-256Mb,datatransferspeed:

133Mbps-400Mbps

Kilopass

NVM

Itera?

:

32b-1Mb;工艺:

65nm-40nm

Mosys

PSRAM

到目前为止,采用这种存储单元(1TSRAM存储单元)的芯

片销量达到5,000万只左右

发展趋势:

高速网络方面:

FCRAM和RLDRAM快速发展,可能会和SRAM竞争。

便携式应用领域:

CellularRAM和MobileFCRAM等PSRAM产品,SRAM。

老手机存储器大多使用LPSRAM,因为SRAM比DRAM省电,现在手机功能越来越多,因此手机对存储容量的需求逐渐攀升,1TSRAM及LPDRAM在容量方面都比SRAM高,而仃SRAM消耗的电量比较少,所以1TSRAM在此领域使用的优势相对较高【1】。

目前PSRAM阵营包括了由柏士半导体(Cypress)、英飞凌(Infineon)、美光(Micron)、日本瑞萨科技(Renesas)合组的CellularRAM联盟;由NEC、富士通、东芝等日系业者合组的CosmoRAM联盟主要也是针对行动装置应用的PSRAM架构阵营,不过由于其接脚及

一些定义上与CellularRAM不兼容,所以一般较少见到其应用;以及韩国二大存储器厂三星及Hynix合组的PSRAM联盟。

诸如华邦、力晶、南亚科及茂德等台湾存储器厂商,多集中

在CellularRAM这个阵营,如力晶与瑞萨合作,南亚科、华邦与英飞凌合作,茂德则是与柏

士半导体合作(在PSRAM方面)。

目前也已经有容量高达256Mbit的PSRAM产品出现。

1.2.3RAMIP核公司产品分布

MemoryIP公司的产品分布情况:

表3memoryIP公司的各个产品统计表

公司

产品

性能

AnalogBits

ABI-T-13LV-1PSRAM

130nm,800MHz,pipelined,synchronuousdesign

ABI-T-13LV-DPSRAM

800MHz,pipelined,dualportSRAMmacros

ABI-T-90G-1PSRAM

800MHz,pipelined,1PSRAM

macros

ARM

CLN40GL

Highspeed,singleport,40nm

ChipStart

CS-DTI-IB130N

singleport,180nm

CS-DTI-IB130N

Dualport,180nm

Mosys

PSRAM

到目前为止,采用这种存储单元(1TSRAM存储单元)的芯片销量达到5,000万只左右

SRAM-Memory

-CLHS16KX128PRLLWTS018

200Mb,180nm,200MHz,PipelinedReadAccessTiming

SRAM-Memory

-CLHS24KX256rPREWTS90

6Mb,90nm,250MHz,PipelinedReadAccessTiming

SRAM-Memory

-CLLP_8KX64_FREW_SM018

0.5Mb,180nm,100MHz,Flow-ThroughReadAccess

Timing

DolphinIntegration

SpRAMuLLNEPTUNE180nm

180nm,Ultralowleakageeveningenericprocess,

Functionalityfrom2Vdownto1.4V

SpRAM-uLLNEPTUNE130nm

130nm,Ultra-low-leakageeveningenericprocess,Power-downmodeforswitchingofftheperipherywhenthememoryisinsleepmode

eSilicon

28nmSPSRAM

28nm;MUX:

4:

1,8:

1,16:

1;words:

256-8192;bits:

4-256

Novelics

?

coolSRAM-6Tembeddedmemory-1024x8SRAM-Dongbu110G

110nm,Singleportarchitecture,Basedonfoundry-provided6TSRAMcell

samsung

K1B5616BFB

16Mbx16,SynchronousBurstUni-Transistor,supplyvoltage:

1.7-1.95VcontainingInternalTCSR(TemperatureCompensatedSelfRefresh),Max.clockfrequencv:

108MHz

K1B5616BKB

16Mbx16,supplyvoltage:

1.7-1.95VcontainingInternalTCSR(TemperatureCompensatedSelfRefresh)

1.3RAM国内外研究情况

1.3.1RAM国内研究情况

国内主要研究机构在RAM方面的研究方向:

1)复旦大学

近年来复旦大学所发表论文情况如下表所示

期刊论文

相变及阻变存储器

SRAM

Cache

其他

总数

7

3

3(低功耗)

7

20

学位论文

(SRAM电

路)

低功耗

高速

其他

总数

3

1

13

18

学位论文

(Cache)

高性能

低功耗

其他

总数

2(算法)

4

4

10

上表表明在存储器方面,复旦大学主要研究方向为低功耗SRAM电路设计,新型存储器结

构设计,Cache方面的研究主要在低功耗方面。

2)清华大学

期刊论文

铁电存储器

SRAM

Cache

总数

3

3

5(算法、调度、低功耗)

34

SCI

SRAM

1(双端口)

学位论文

(SRAM电

路)

编译器设计

其他

总数

3

3

6

学位论文

(Cache)

高性能

低功耗

总数

4

清华大学在存储器方面的研究主要在新型铁电存储器,SRAM编译器设计方面

3)北京大学

期刊论文

新型存储器

SRAM

Cache

总数

4

1

5(算法、调度、低功耗)

34

SCI

FinSRAM

adibaticSRAM(绝热)

2

1

学位论文

(SRAIV电

路)

编译器设计

高速

低功耗

其他

2

2

2

9

学位论文

(Cache)

高性能

低功耗

其他

总数

6

1

17

24

学位论文中的高性能只是在具体的系统设计中提到,基本上都是在Cache调度及算法优化两

方面提高Cache性能。

132RAM国外研究情况

调研机构:

Intel,IBM,purdue大学,MIT,Standford,Leuven(ESAT-MICASLaboratory)。

这些机构2005—2011关于RAM方面的研究情况:

Intel

SRAMPapers

2005

Sleeptransistorforleakagereduction,65nm

LowpowerSRAMtechniquesforhandheldproducts(Leakage)®0nm

2006

Dynamicpowersupply,improvestabilityandleakage,3GHz,65nmDualsupply,4.2GHz,operatedownto0.7V,65nm

Wordlineandbitlinepulsingschemesforstability,65nm

Addressthestabilityandleakage,4.2GHz,65nm

2007

Powersupplynoiseeffectonstability,LowpowerSRAM,1.1GHz,65nm

2008

ReadwriteassistcircuitforVccmin

Stabilityandleakage,3.5GHz,45nmhigh-K

2009

3DSRAMforhighperformanee,Voltage-scalableSRAMforpower,32nmhigh-k,4GHzDNFCellsanddynamicmulti-VCCforstability,45nmDynamicstabilityandleakage,45nmhigh-k,3.8GHz

2010

PVTandagingadaptivewordlinefor8T,45nm,

AdaptivedynamicstabilityforVccmin,32nmhigh-k,

Tunablereplicabitsfor8TSRAM,

ImprovingVminandyieldusingvariation-awareBTIstress,45nm

2011

Ultralow-voltagePVTSchmitt-trigger-basedSRAM,130nm,BitcelloptimizationandcircuittechniquesfornanometerSRAM,

Intel

CachePapers

2005

Asynchronous24MBL3cache,5-cyclearrayoperate,2GHz/0.8VBitlineleakagecompensationandleakagereduction,3GHz,90nmLowpowerL1cache,2.5GHz,90nm

Improvedinstructionfetchingwithanewblock-base,

Leakagepoweron-chipcache

Datacacheusing3D

2006

16MbL3cache,

ClockgenerationanddistributionforL3cacheCachereplacementalgorithms

Improvedatacacheefficiency

2007

16MBL3cache,65nm

Fine-grainmonitoringofsharedcaches

DRAMcachearchitecture

2008

On-linefailuredetectionandconfinement

512KBL2Cache,2GHz,45nm

2009

Lowvccminfault-tolerantcache

24MBL3cache,45nm

Hardware/softwareco-simulationforLLC

2010

L2cachemodelsinverilogHDL

Performaneeandenergyofmany-corecaches

2011

Architecturalerror-tolerantforVCCmincache

Adaptivecachedesigntoenablereliablelow-voltage

Smartschedulingforasymmetriccache

IBM

SRAM

2005

LowleakageSRAMcache;

LowpowerembeddedSRAMforacellprocessor;

2007

SRAMarraysforP0WER6;

ReadandwriteassistcircuitstoexpandVcc;Processvariationtolerantself-repairingSRAM;

2008

AgingeffectsandmanufacturingvariationonSRAMSER;DesignPD/SOISRAMgateleakageandVthvariation;600mVSRAMarraywithdynamiccellbiasing;

8TSRAM;

ImpactofrandomdevicevariationonSRAMcell;6GHzSRAMforcellbroadbandenginein65nmSOI;

Lowenergyprotonsingle-event-upset;

2009

RelaxingreadandwritestabilityusingasymmetrictransistorAssessSRAMstabilityonrandomdopantfluctuations8MbSRAMin45nmSOI

Designsub-90nmlow-powervariationtolerantPD/SOISRAMSingle-eventupsetsandmultiple-bitupsetson45nmSOISRAM

2011

Anovelcolumn-decoupled8Tcellforlowpower

Leuven(ESAT-MICASLaboratory)WimDehaene

Focusoncircuitleveldigitaldesign.Thephysicalaspectsandlimitationsofdigitalcircuitsarehandled.Thistranslatesintotwomainresearchbranches.

(1)DesignofSRAMmemoriesinadvaneedCMOStechnologies,takingthetypicalscalingeffects,leakageandvariability,intoaccountanddealingwiththem.

(2)DesignofultralowenergycircuitsforWirelessSensorNetworks(WSN).Thisbranchalsocontainstheresearchtowardstheimplementationofultralowvoltage,sub-thresholdlogic.

Leuven

2005

Energyefficientmemoryarchitectureforhighspeeddecoding;

Variablescaleparetobufferandrun-timeconfigurationforlowpowerembeddedSRAM;Asmallgranularcontrolledleakagereduction;

2006

Readandwritestabilityanalysis;

2007

LowpowerembeddedSRAMforwirelessapplications;Impactofrandomsoftoxidebreakdownonenergy/delaydrift

2009

A3.6pJ/Access480MHz,128kbOn-ChipSRAMWith850MHzBoostModein90nmCMOS;

2011

Cross-cellInterfereneeVariabilityAwareModelofFullyPlanarNANDFlashMemory

IncludingLineEdgeRoughness

Purdue

SRAMPapers

2005

AfeasibilitystudyofsubthresholdSRAMacrosstechnologygenerations,[J]

EfficienttestingofSRAMwithoptimizedmarchsequencesandanovelDFTtechniqueforemergingfailuresduetoprocessvariations,[J]

ModelingandtestingofSRAMfornewfailuremechanismsduetoprocessvariationsinnanoscaleCMOS,[J]

ModelingoffailureprobabilityandstatisticaldesignofSRAMarrayforyieldenhancementinnanoscaledCMOS,[J]

Fastandaccurateestimationofnano-scaledSRAMreadfailureprobabilityusingcriticalpointsampling,[C]

LeakageCurrentBasedStabilizationSchemeforRobustSense-AmplifierDesignforYieldEnhancementinNano-scaleSRAM,[C]

Modelingandoptimizationapproachtorobustandlow-powerFinFETSRAMdesigninnanoscaleera,[C]

Technology-circuitco-designinwidth-quantizedquasi-planardouble-gateSRAM,[C]Reliableandself-repairingSRAMinnano-scaletechnologiesusingleakageanddelaymonitoring,[C]

2006

Techno