高速数据采集系统设计.doc

《高速数据采集系统设计.doc》由会员分享,可在线阅读,更多相关《高速数据采集系统设计.doc(8页珍藏版)》请在冰豆网上搜索。

基于FPGA和SoC单片机的

高速数据采集系统设计

一.选题背景及意义

随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分。

高速数据采集系统在自动测试、生产控制、通信、信号处理等领域占有极其重要的地位。

随着SoC单片机的快速发展,现在已经可以将采集多路模拟信号的A/D转换子系统和CPU核集成在一片芯片上,使整个数据采集系统几乎可以单芯片实现,从而使数据采集系统体积小,性价比高。

FPGA为实现高速数据采集提供了一种理想的实现途径。

利用FPGA高速性能和本身集成的几万个逻辑门和嵌入式存储器块,把数据采集系统中的数据缓存和控制电路全部集成在一片FPGA芯片中,大大减小了系统体积,提高了灵活性。

FPGA还具有系统编程功能以及功能强大的EDA软件支持,使得系统具有升级容易、开发周期短等优点。

二.设计要求

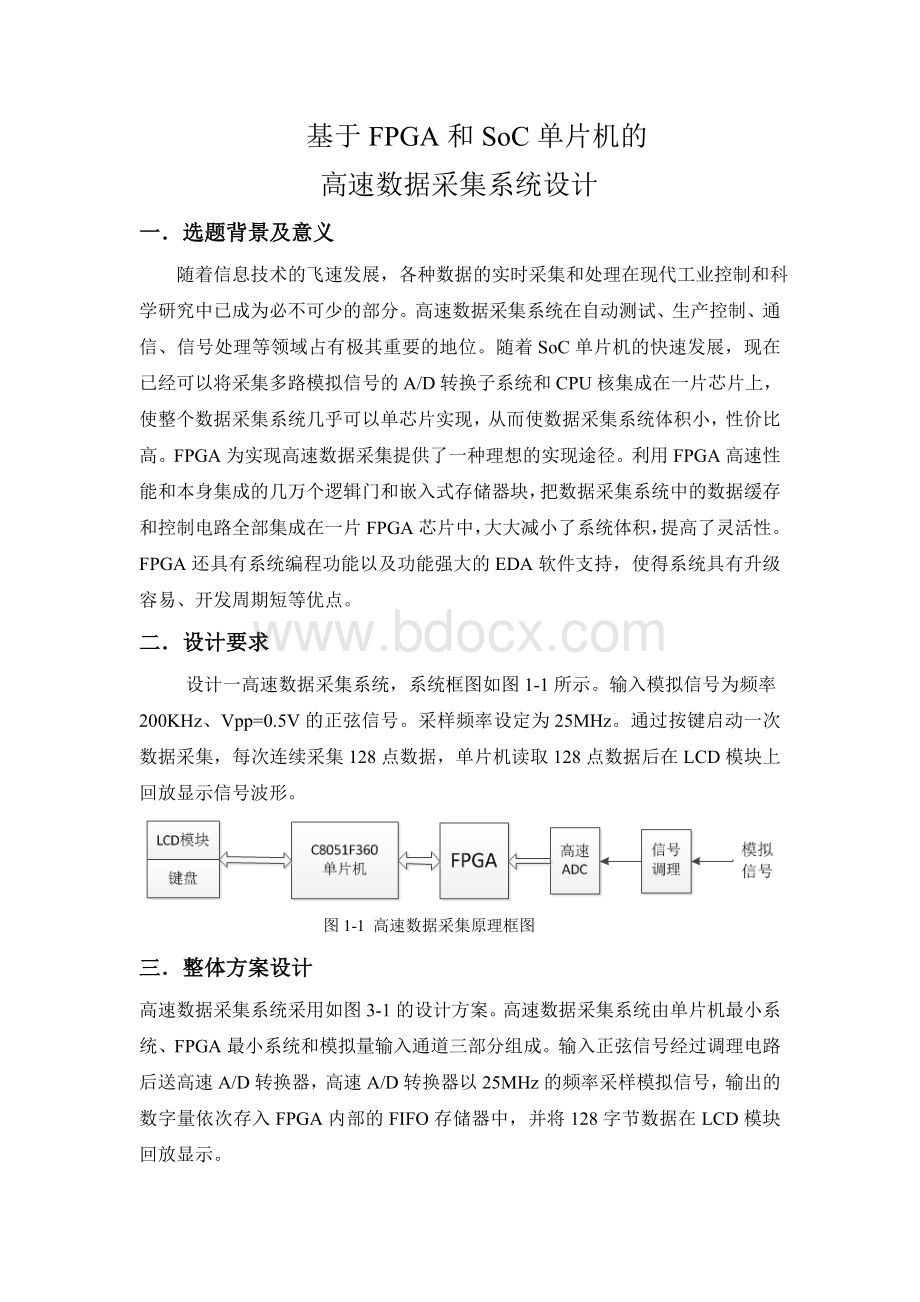

设计一高速数据采集系统,系统框图如图1-1所示。

输入模拟信号为频率200KHz、Vpp=0.5V的正弦信号。

采样频率设定为25MHz。

通过按键启动一次数据采集,每次连续采集128点数据,单片机读取128点数据后在LCD模块上回放显示信号波形。

图1-1高速数据采集原理框图

三.整体方案设计

高速数据采集系统采用如图3-1的设计方案。

高速数据采集系统由单片机最小系统、FPGA最小系统和模拟量输入通道三部分组成。

输入正弦信号经过调理电路后送高速A/D转换器,高速A/D转换器以25MHz的频率采样模拟信号,输出的数字量依次存入FPGA内部的FIFO存储器中,并将128字节数据在LCD模块回放显示。

图3-1高速数据采集系统设计方案

四.硬件电路设计

1.模拟量输入通道的设计

模拟量输入通道由高速A/D转换器和信号调理电路组成。

信号调理电路将模拟信号放大、滤波、直流电平位移,以满足A/D转换器对模拟输入信号的要求。

2.高速A/D转换电路设计

五.FPGA模块设计

本设计的数据缓冲电路采用FIFO存储器。

FIFO数据缓冲电路原理如图5-1。

图5-1FIFO数据缓冲电路原理

FIFO的写端口的数据线与ADS931的数据线直接相连,FIFO的写时钟和ADS931采用同一时钟信号CLK0。

FIFO的读端口与单片机并行总线相连,数据输出端口加了三态缓冲器。

地址译码器的片选信号和读信号相或非后作为FIFO的读时钟电路和三态缓冲的使能信号。

FIFO数据顶层原理图如图5-2。

图5-2FIFO数据顶层原理图

六.F360单片机模块设计

主程序完成C8051F360单片机初始化、检测有无按键输入等功能。

在此系统中我们加入了一个频率测试显示功能。

主程序流程图如图6-2。

图6-2主程序流程图

主程序源代码如下:

voidmain()

{

ucharxdata*addr1;

uinti;

floatf,ts;

ucharfuzhi;

intup,down,m,n;

up=0;down=0;m=0;n=0;ts=0.04;

InitDevice(); //F360初始化

InsitiLcd(); //LCD模块初始化

DispHan(hanzi10,0x80,0x10);

DispHan(hanzi11,0x92,0x08);

DispHan(hanzi12,0x8a,0x08);

DispHan(hanzi13,0x98,0x08);

DispHan(hanzi14,0x9c,0x08);

addr1=LEDENCS;

*addr1=0x01;

START=0;

EOC=1;

while

(1)

{

if(keysign==1)

{

keysign=0;

if(keycode==0x00) //k0键

{

START=1;

while(EOC==0);//等待数据采集完

START=0;

addr1=CS1;

while(EOC==1)//等待读出第一个有效数据

{

WaveData[0]=*addr1;

}

for(i=1;i<128;i++)

{

WaveData[i]=*addr1;

if(i>3)

{

if(WaveData[i]>=WaveData[i-2])up=1;

if((WaveData[i]<=WaveData[i-2])&&(up==1)){up=0;m=i-1;}

}

}

if(m>64)

{

for(i=m-5;i>=1;i--)

{

if(WaveData[i]>=WaveData[i-2])down=1;

if((WaveData[i]<=WaveData[i-2])&&(down==1)){down=0;n=i-1;}

}

}

else

{

for(i=m+5;i<=128;i++)

{

if(WaveData[i]>=WaveData[i+2])down=1;

if((WaveData[i]<=WaveData[i+2])&&(down==1)){down=0;n=i+1;}

}

}

if(m>=n)f=1/(4*(m-n)*ts);

elsef=1/(4*(n-m)*ts);

fuzhi=WaveData[m]-WaveData[n];

InsitiLcd();

ShowWave();

}

if(keycode==0x01) //k1键

{

InsitiLcd();

DispHan(hanzi15,0x90,0x06);

xiaoshu(f,0x93);

DispHan(hanzi17,0x96,0x03);

// DispHan(hanzi16,0x8a,0x06);

}

}

}

}

七.系统调试与结果

将各个模块连接后,进行调试。

首先在LCD上显示如图7-1的界面。

图7-1LCD初始界面

在信号调理电路的模拟输入端输入频率200KHz、Vpp=0.5V的正弦信号,按K0键,LCD显示正弦波如图7-2。

7-2按K0后的波形显示

按K1,LCD显示频率如图7-3。

7-3LCD频率显示

与输入频率相比有误差,不过在可以接受的范围内。