FPGA实验指导书.docx

《FPGA实验指导书.docx》由会员分享,可在线阅读,更多相关《FPGA实验指导书.docx(80页珍藏版)》请在冰豆网上搜索。

FPGA实验指导书

山东工商学院

实验指导书

信息与电子工程学院

[在此处键入文档摘要。

摘要通常为文档内容的简短概括。

在此处键入文档摘要。

摘要通常为文档内容的简短概括。

]

第一部分实验开发系统概述及使用说明

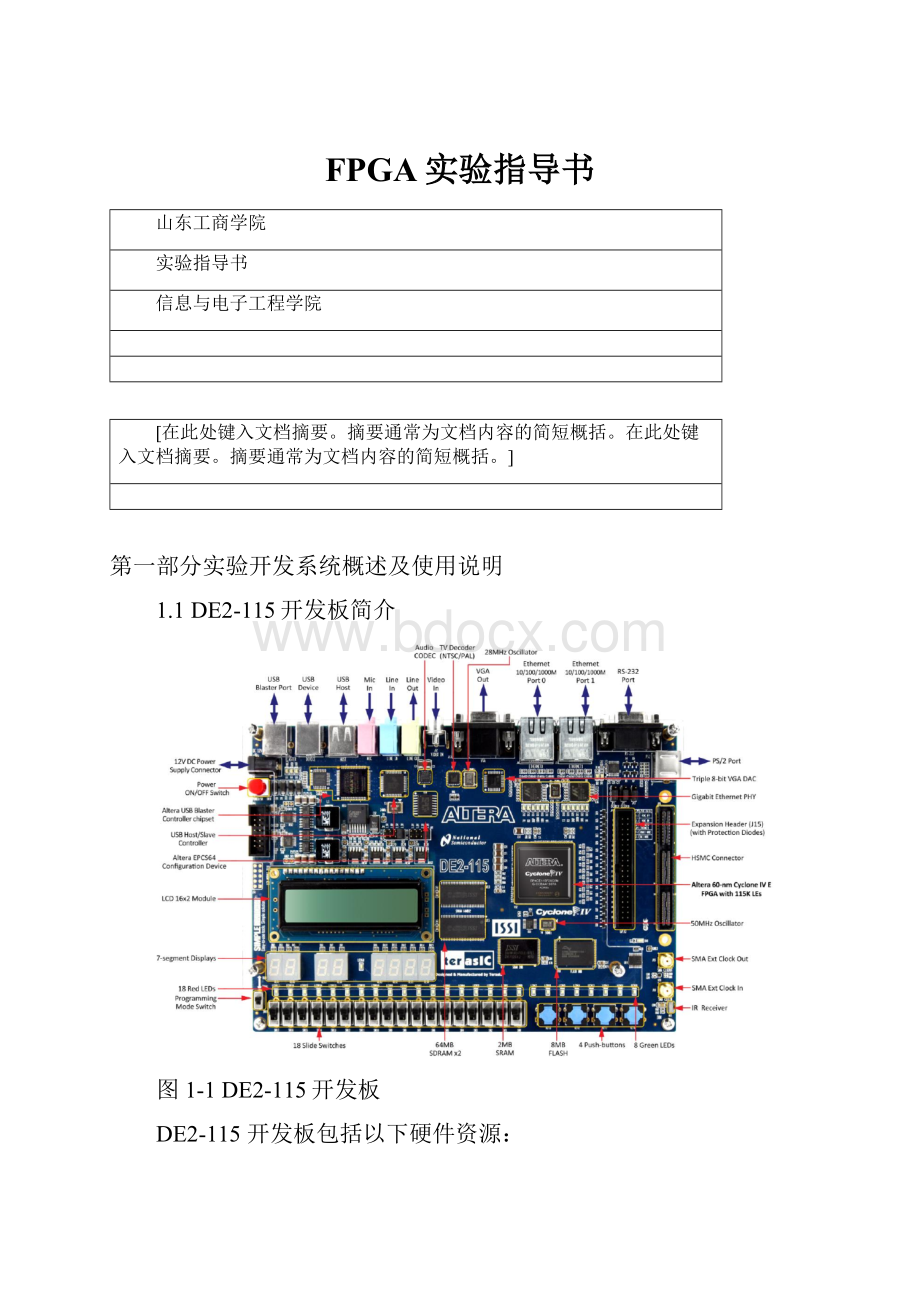

1.1DE2-115开发板简介

图1-1DE2-115开发板

DE2-115开发板包括以下硬件资源:

●AlteraCycloneIV4CE115FPGA器件

●Altera系列配置–EPCS64

●板上USBBlaster用于编程,同时支持JTAG模式和AS模式

●2MBSRAM

●2片64MBSDRAM

●8MB闪存

●SD卡插槽

●4个按钮开关

●18个滑动开关

●18个红色LEDs

●9个绿色LEDs

●50MHz晶振提供给时钟源

●24-bitCD-品质声道CODEC带有线路输入,线路输出和麦克风输入接口

●VGADAC(8-比特高速三通道DACs)带有VGA输出接口

●TV解码器(NTSC/PAL/SECAM)和TV输入接口

●2千兆以太网PHY带RJ45连接器

●带有A类和B类USB接口的USB主从控制器

●RS-232收发器和9针连接器

●PS/2鼠标/键盘接口

●IR收发器

●2个SMA接头,用于外部时钟输入/输出

●1个40-pin扩展口,带二极管保护

●1个HSMC连接器

●16x2LCD模组

除了这些硬件功能外,DE2-115开发板还支持标准I/O接口和用于评估各项组件的控制面板等软件工具。

该软件也提供用于验证DE2-115开发板高级功能的大量实例演示。

1.2DE2-115系统框图

图1-2给出了DE2-115的系统框图。

所有的连接都是通过CycloneIVEFPGA器件来实现的。

用户可以通过配置FPGA来实现各种系统设计。

图1-2DE2—115系统框图

下面是图1-2中各功能块的详细信息:

FPGA器件

●CycloneIVEP4CE115F29器件

●114,480个逻辑单元

●432M9K内存模块

●3,888Kbits嵌入式存储器位

●4个锁相环

FPGA配置

●同时支持JTAG模式和AS模式

●提供系列配置器件——EPCS64

●内建USBBlaster电路

存储器配置

●128MB(32Mx32bit)SDRAM

●2MB(1Mx16)SRAM

●8位8MB(4Mx16)Flash存储器8M×4×8位闪存

●32KbEEPROM

SD卡接口

●提供SPI模式和4位SD模式用于SD卡接入

连接器

●2个10/100/1000以太网接口

●1个HSMC

●可配置的I/O标准(电平:

3.3/2.5/1.8/1.5V)

●A型和B型USB接口

◆完全兼容USB2.0的主从控制器

◆支持全速和低速数据传输

◆可用于PC驱动

●40针扩展口

●可配置的I/O标准(电平:

3.3/2.5/1.8/1.5V)

●VGA输出接口

●VGADAC(三通道高速视频DACs)

●提供带有流控制的RS-232端口的DB9连接器

●提供PS/2鼠标/键盘连接器

时钟输入

●3个50MHz晶振

●1个SMA外部时钟输入

音频CODEC

●24位编码器/解码器CODEC

●包括线路输入,线路输出和麦克风输入

显示输出

●16x2LCD模组

开关和显像管

●18个滑动开关和4个按钮开关

●18个红色和9个绿色LEDs

●8个七段显像管

其他特征

●红外遥控接收模块

●TV解码器(NTSC/PAL/SECAM制式)和TV-in连接器

电源

●直流电源输入

●开关和降压调节器LM3150MH

1.3DE2-115引脚列表

表1拨码开关引脚配置

信号名

FPGA引脚号

描述

I/O标准

SW[0]

PIN_AB28

SlideSwitch[0]

DependingonJP7

SW[1]

PIN_AC28

SlideSwitch[1]

DependingonJP7

SW[2]

PIN_AC27

SlideSwitch[2]

DependingonJP7

SW[3]

PIN_AD27

SlideSwitch[3]

DependingonJP7

SW[4]

PIN_AB27

SlideSwitch[4]

DependingonJP7

SW[5]

PIN_AC26

SlideSwitch[5]

DependingonJP7

SW[6]

PIN_AD26

SlideSwitch[6]

DependingonJP7

SW[7]

PIN_AB26

SlideSwitch[7]

DependingonJP7

SW[8]

PIN_AC25

SlideSwitch[8]

DependingonJP7

SW[9]

PIN_AB25

SlideSwitch[9]

DependingonJP7

SW[10]

PIN_AC24

SlideSwitch[10]

DependingonJP7

SW[11]

PIN_AB24

SlideSwitch[11]

DependingonJP7

SW[12]

PIN_AB23

SlideSwitch[12]

DependingonJP7

SW[13]

PIN_AA24

SlideSwitch[13]

DependingonJP7

SW[14]

PIN_AA23

SlideSwitch[14]

DependingonJP7

SW[15]

PIN_AA22

SlideSwitch[15]

DependingonJP7

SW[16]

PIN_Y24

SlideSwitch[16]

DependingonJP7

SW[17]

PIN_Y23

SlideSwitch[17]

DependingonJP7

表2按钮开关引脚配置

信号名

FPGA引脚号

描述

I/O标准

KEY[0]

PIN_M23

Push-button[0]

DependingonJP7

KEY[1]

PIN_M21

Push-button[1]

DependingonJP7

KEY[2]

PIN_N21

Push-button[2]

DependingonJP7

KEY[3]

PIN_R24

Push-button[3]

DependingonJP7

表3LED引脚配置

信号名

FPGA引脚号

描述

I/O标准

LEDR[0]

PIN_G19

LEDRed[0]

2.5V

LEDR[1]

PIN_F19

LEDRed[1]

2.5V

LEDR[2]

PIN_E19

LEDRed[2]

2.5V

LEDR[3]

PIN_F21

LEDRed[3]

2.5V

LEDR[4]

PIN_F18

LEDRed[4]

2.5V

LEDR[5]

PIN_E18

LEDRed[5]

2.5V

LEDR[6]

PIN_J19

LEDRed[6]

2.5V

LEDR[7]

PIN_H19

LEDRed[7]

2.5V

LEDR[8]

PIN_J17

LEDRed[8]

2.5V

LEDR[9]

PIN_G17

LEDRed[9]

2.5V

LEDR[10]

PIN_J15

LEDRed[10]

2.5V

LEDR[11]

PIN_H16

LEDRed[11]

2.5V

LEDR[12]

PIN_J16

LEDRed[12]

2.5V

LEDR[13]

PIN_H17

LEDRed[13]

2.5V

LEDR[14]

PIN_F15

LEDRed[14]

2.5V

LEDR[15]

PIN_G15

LEDRed[15]

2.5V

LEDR[16]

PIN_G16

LEDRed[16]

2.5V

LEDR[17]

PIN_H15

LEDRed[17]

2.5V

LEDG[0]

PIN_E21

LEDGreen[0]

2.5V

LEDG[1]

PIN_E22

LEDGreen[1]

2.5V

LEDG[2]

PIN_E25

LEDGreen[2]

2.5V

LEDG[3]

PIN_E24

LEDGreen[3]

2.5V

LEDG[4]

PIN_H21

LEDGreen[4]

2.5V

LEDG[5]

PIN_G20

LEDGreen[5]

2.5V

LEDG[6]

PIN_G22

LEDGreen[6]

2.5V

LEDG[7]

PIN_G21

LEDGreen[7]

2.5V

LEDG[8]

PIN_F17

LEDGreen[8]

2.5V

表4七段数码管引脚配置

信号名

FPGA引脚号

描述

I/O标准

HEX0[0]

PIN_G18

SevenSegmentDigit0[0]

2.5V

HEX0[1]

PIN_F22

SevenSegmentDigit0[1]

2.5V

HEX0[2]

PIN_E17

SevenSegmentDigit0[2]

2.5V

HEX0[3]

PIN_L26

SevenSegmentDigit0[3]

DependingonJP7

HEX0[4]

PIN_L25

SevenSegmentDigit0[4]

DependingonJP7

HEX0[5]

PIN_J22

SevenSegmentDigit0[5]

DependingonJP7

HEX0[6]

PIN_H22

SevenSegmentDigit0[6]

DependingonJP7

HEX1[0]

PIN_M24

SevenSegmentDigit1[0]

DependingonJP7

HEX1[1]

PIN_Y22

SevenSegmentDigit1[1]

DependingonJP7

HEX1[2]

PIN_W21

SevenSegmentDigit1[2]

DependingonJP7

HEX1[3]

PIN_W22

SevenSegmentDigit1[3]

DependingonJP7

HEX1[4]

PIN_W25

SevenSegmentDigit1[4]

DependingonJP7

HEX1[5]

PIN_U23

SevenSegmentDigit1[5]

DependingonJP7

HEX1[6]

PIN_U24

SevenSegmentDigit1[6]

DependingonJP7

HEX2[0]

PIN_AA25

SevenSegmentDigit2[0]

DependingonJP7

HEX2[1]

PIN_AA26

SevenSegmentDigit2[1]

DependingonJP7

HEX2[2]

PIN_Y25

SevenSegmentDigit2[2]

DependingonJP7

HEX2[3]

PIN_W26

SevenSegmentDigit2[3]

DependingonJP7

HEX2[4]

PIN_Y26

SevenSegmentDigit2[4]

DependingonJP7

HEX2[5]

PIN_W27

SevenSegmentDigit2[5]

DependingonJP7

HEX2[6]

PIN_W28

SevenSegmentDigit2[6]

DependingonJP7

HEX3[0]

PIN_V21

SevenSegmentDigit3[0]

DependingonJP7

HEX3[1]

PIN_U21

SevenSegmentDigit3[1]

DependingonJP7

HEX3[2]

PIN_AB20

SevenSegmentDigit3[2]

DependingonJP6

HEX3[3]

PIN_AA21

SevenSegmentDigit3[3]

DependingonJP6

HEX3[4]

PIN_AD24

SevenSegmentDigit3[4]

DependingonJP6

HEX3[5]

PIN_AF23

SevenSegmentDigit3[5]

DependingonJP6

HEX3[6]

PIN_Y19

SevenSegmentDigit3[6]

DependingonJP6

HEX4[0]

PIN_AB19

SevenSegmentDigit4[0]

DependingonJP6

HEX4[1]

PIN_AA19

SevenSegmentDigit4[1]

DependingonJP6

HEX4[2]

PIN_AG21

SevenSegmentDigit4[2]

DependingonJP6

HEX4[3]

PIN_AH21

SevenSegmentDigit4[3]

DependingonJP6

HEX4[4]

PIN_AE19

SevenSegmentDigit4[4]

DependingonJP6

HEX4[5]

PIN_AF19

SevenSegmentDigit4[5]

DependingonJP6

HEX4[6]

PIN_AE18

SevenSegmentDigit4[6]

DependingonJP6

HEX5[0]

PIN_AD18

SevenSegmentDigit5[0]

DependingonJP6

HEX5[1]

PIN_AC18

SevenSegmentDigit5[1]

DependingonJP6

HEX5[2]

PIN_AB18

SevenSegmentDigit5[2]

DependingonJP6

HEX5[3]

PIN_AH19

SevenSegmentDigit5[3]

DependingonJP6

HEX5[4]

PIN_AG19

SevenSegmentDigit5[4]

DependingonJP6

HEX5[5]

PIN_AF18

SevenSegmentDigit5[5]

DependingonJP6

HEX5[6]

PIN_AH18

SevenSegmentDigit5[6]

DependingonJP6

HEX6[0]

PIN_AA17

SevenSegmentDigit6[0]

DependingonJP6

HEX6[1]

PIN_AB16

SevenSegmentDigit6[1]

DependingonJP6

HEX6[2]

PIN_AA16

SevenSegmentDigit6[2]

DependingonJP6

HEX6[3]

PIN_AB17

SevenSegmentDigit6[3]

DependingonJP6

HEX6[4]

PIN_AB15

SevenSegmentDigit6[4]

DependingonJP6

HEX6[5]

PIN_AA15

SevenSegmentDigit6[5]

DependingonJP6

HEX6[6]

PIN_AC17

SevenSegmentDigit6[6]

DependingonJP6

HEX7[0]

PIN_AD17

SevenSegmentDigit7[0]

DependingonJP6

HEX7[1]

PIN_AE17

SevenSegmentDigit7[1]

DependingonJP6

HEX7[2]

PIN_AG17

SevenSegmentDigit7[2]

DependingonJP6

HEX7[3]

PIN_AH17

SevenSegmentDigit7[3]

DependingonJP6

HEX7[4]

PIN_AF17

SevenSegmentDigit7[4]

DependingonJP6

HEX7[5]

PIN_AG18

SevenSegmentDigit7[5]

DependingonJP6

HEX7[6]

PIN_AA14

SevenSegmentDigit7[6]

3.3V

表5时钟信号引脚配置信息

信号名

FPGA引脚号

描述

I/O标准

CLOCK_50

PIN_Y2

50MHzclockinput

3.3V

CLOCK2_50

PIN_AG14

50MHzclockinput

3.3V

CLOCK3_50

PIN_AG15

50MHzclockinput

DependingonJP6

SMA_CLKOUT

PIN_AE23

External(SMA)clockoutput

DependingonJP6

SMA_CLKIN

PIN_AH14

External(SMA)clockinput

3.3V

表6LCD模块引脚配置

信号名

FPGA引脚号

描述

I/O标准

LCD_DATA[7]

PIN_M5

LCDData[7]

3.3V

LCD_DATA[6]

PIN_M3

LCDData[6]

3.3V

LCD_DATA[5]

PIN_K2

LCDData[5]

3.3V

LCD_DATA[4]

PIN_K1

LCDData[4]

3.3V

LCD_DATA[3]

PIN_K7

LCDData[3]

3.3V

LCD_DATA[2]

PIN_L2

LCDData[2]

3.3V

LCD_DATA[1]

PIN_L1

LCDData[1]

3.3V

LCD_DATA[0]

PIN_L3

LCDData[0]

3.3V

LCD_EN

PIN_L4

LCDEnable

3.3V

LCD_RW

PIN_M1

LCDRead/WriteSelect,0=Write,1=Read

3.3V

LCD_RS

PIN_M2

LCDCommand/DataSelect,0=Command,1=Data

3.3V

LCD_ON

PIN_L5

LCDPowerON/OFF

3.3V

LCD_BLON

PIN_L6

LCDBackLightON/OFF

3.3V

表7HSMC接口引脚配置

信号名e

FPGA引脚号

描述

I/O标准

HSMC_CLKIN0

PIN_AH15

Dedicatedclockinput

DependingonJP6

HSMC_CLKIN_N1

PIN_J28

LVDSRXorCMOSI/Oordifferentialclockinput

DependingonJP7

HSMC_CLKIN_N2

PIN_Y28

LVDSRXorCMOSI/Oordifferentialclockinput

DependingonJP7

HSMC_CLKIN_P1

PIN_J27

LVDSRXorCMOSI/Oordifferentialclockinput

DependingonJP7

HSMC_CLKIN_P2

PIN_Y27

LVDSRXorCMOSI/Oordifferentialclockinput

DependingonJP7

HSMC_CLKOUT0

PIN_AD28

Dedicatedclockoutput

DependingonJP7

HSMC_CLKOUT_N1

PIN_G24

LVDSTXorCMOSI/Oordifferentialclockinput/output

DependingonJP7

HSMC_CLKOUT_N2

PIN_V24

LVDSTXorCMOSI/Oordifferentialclockinput/output

DependingonJP7

HSMC_CLKOUT_P1

PIN_G23

LVDSTXorCMOSI/Oordifferentialclockinput/output

DependingonJP7

HSMC_CLKOUT_P2

PIN_V23

LVDSTXorCMOSI/Oordifferentialclockinput/output

DependingonJP7

HSMC_D[0]

PIN_AE26

LVDSTXorCMOSI/O

DependingonJP7

HSMC_D[1]

PIN_AE28

LVDSTXorCMOSI/O

DependingonJP7

HSMC_D[2]

PIN_AE27

LVDSTXorCMOSI/O

DependingonJP7

HSMC_D[3]

PIN_AF27

LVDSTXorCMOSI/O

DependingonJP7

HSMC_RX_D_N[0]

PIN_F25

LVDSRXbit0norCMOSI/O

DependingonJP7

HSMC_RX_D_N[1]

PIN_C27

LVDSRXbit1norCMOSI/O

DependingonJP7

HSMC_RX_D_N[2]

PIN_E26

LVDSRXbit2norCMOSI/O

DependingonJP7

HSMC_RX_D