FinFET.docx

《FinFET.docx》由会员分享,可在线阅读,更多相关《FinFET.docx(36页珍藏版)》请在冰豆网上搜索。

FinFET

FinFET简介

FinFET称为鳍式场效晶体管(FinField-EffectTransistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管。

闸长已可小于25奈米。

该项技术的发明人是加州大学伯克利分校的胡正明教授。

Fin是鱼鳍的意思,FinFET命名根据晶体管的形状与鱼鳍的相似性。

发明人

该项技术的发明人是加州大学伯克利分校的胡正明(ChenmingHu)教授[1]。

胡正明教授1968年在台湾国立大学获电子工程学士学位,1970年和1973年在伯克利大学获得电子工程与计算机科学硕士和博士学位。

现为美国工程院院士。

2000年凭借FinFET获得美国国防部高级研究项目局最杰出技术成就奖(DARPAMostOutstandingTechnicalAccomplishmentAward)。

他研究的BSIM模型已成为晶体管模型的唯一国际标准,培养了100多名学生,许多学生已经成为这个领域的大牛,曾获Berkeley的最高教学奖;于2001~2004年担任台积电的CTO。

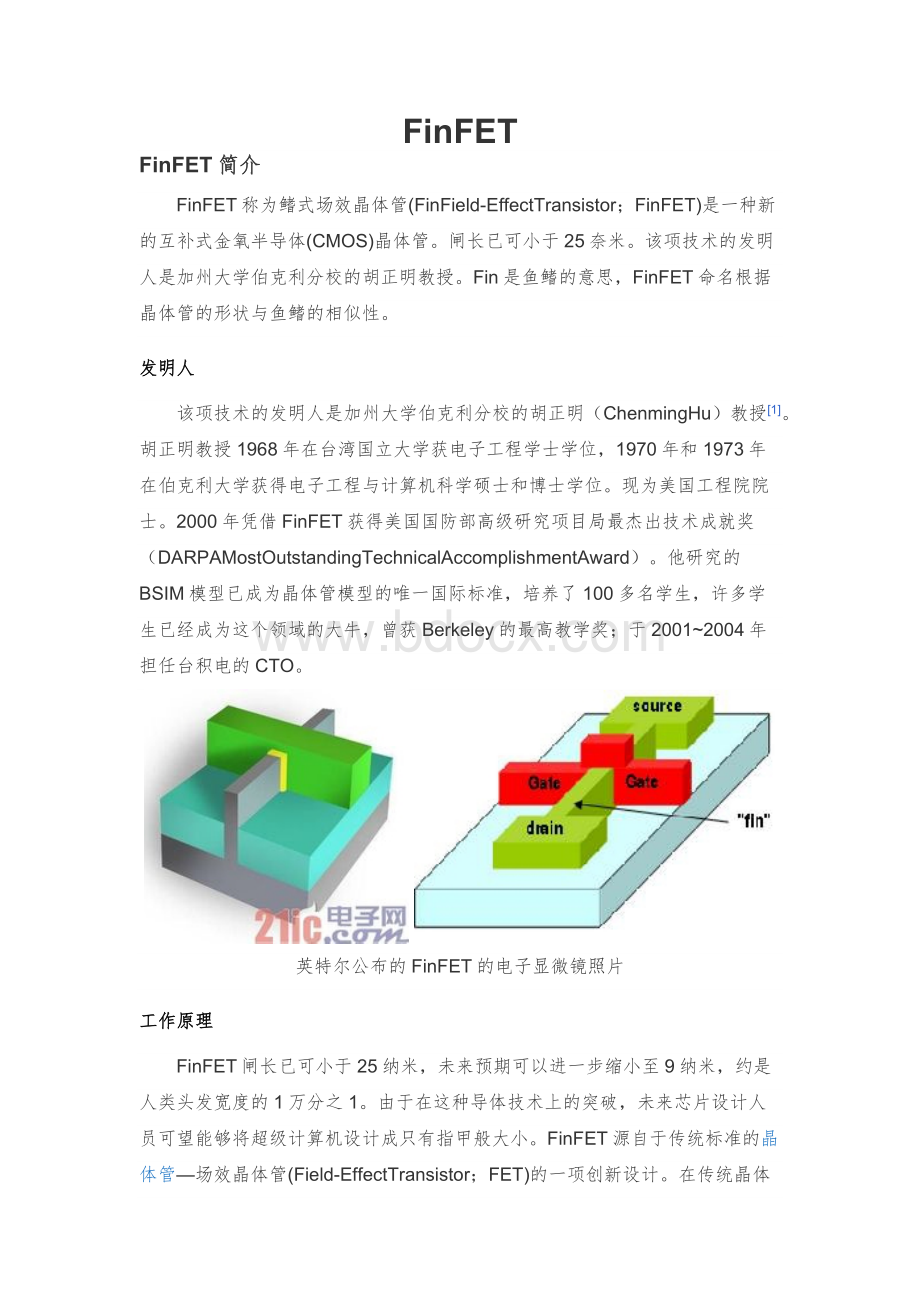

英特尔公布的FinFET的电子显微镜照片

工作原理

FinFET闸长已可小于25纳米,未来预期可以进一步缩小至9纳米,约是人类头发宽度的1万分之1。

由于在这种导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。

FinFET源自于传统标准的晶体管—场效晶体管(Field-EffectTransistor;FET)的一项创新设计。

在传统晶体管结构中,控制电流通过的闸门,只能在闸门的一侧控制电路的接通与断开,属于平面的架构。

在FinFET的架构中,闸门成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。

这种设计可以大幅改善电路控制并减少漏电流(leakage),也可以大幅缩短晶体管的闸长。

[2]

发展状态

在2011年初,英特尔公司推出了商业化的FinFET,使用在其22纳米节点的工艺上[3]。

从IntelCorei7-3770之后的22纳米的处理器均使用了FinFET技术。

由于FinFET具有功耗低,面积小的优点,台湾积体电路制造股份有限公司(TSMC)等主要半导体代工已经开始计划推出自己的FinFET晶体管[4],为未来的移动处理器等提供更快,更省电的处理器。

从2012年起,FinFET已经开始向20纳米节点和14纳米节点推进。

finfet和普通cmos的区别

CMOS(ComplementaryMetalOxideSemiconductor),互补金属氧化物半导体,电压控制的一种放大器件。

是组成CMOS数字集成电路的基本单元。

在计算机领域,CMOS常指保存计算机基本启动信息(如日期、时间、启动设置等)的芯片。

有时人们会把CMOS和BIOS混称,其实CMOS是主板上的一块可读写的RAM芯片,是用来保存BIOS的硬件配置和用户对某些参数的设定。

在今日,CMOS制造工艺也被应用于制作数码影像器材的感光元件,尤其是片幅规格较大的单反数码相机。

SOI和体硅FinFET的比较

RRAM发表于:

2010-4-0620:

47来源:

半导体技术天地

本文比较了SOI和体硅FinFET器件在性能、加工工艺及其成本上的差异。

如果要使SOI和体硅的FinFET器件具有相类似的性能,体硅FinFET器件的制备流程将更为复杂。

在SOI晶圆上,氧化埋层隔离了分立的晶体管,而在体硅器件中,隔离作用则必须通过晶圆工艺来形成。

我们将证明,由于体硅FinFET工艺更为复杂,使得器件的差异性达到SOI的140%~160%,并会对制造和工艺控制产生严峻的挑战。

虽然SOI基片更为昂贵一些,但更为复杂的体硅FinFET工艺成本的增加大体上已抵消了这部分开销,从而使得在大批量生产时其成本能与体硅工艺大体上相当。

HoracioMendez,SOIIndustryConsortium,Austin,Texas,USA;DavidM.Fried,IBM,EastFishkill,NYUSA;SrikanthB.Samavedam,FreescaleSemiconductor,EastFishkill,NYUSA;ThomasHoffmann,IMEC,Leuven,Belgium;Bich-YenNguyen,Soitec,Austin,Texas,USA

当半导体业界向22nm技术节点挺进时,一些制造厂商已经开始考虑如何从平面CMOS晶体管向三维(3D)FinFET器件结构的过渡问题。

与平面晶体管相比,FinFET器件改进了对沟道的控制,从而减小了短沟道效应。

平面晶体管的栅极位于沟道的正上方,而FinFET器件的栅极则是三面包围着沟道,能从两边来对沟道进行静电控制。

3D结构的挑战

3D结构将会产生新的寄生电容和特征尺寸,这些都必须加以控制以优化晶体管的性能。

FinFET器件的栅长是在平行于“鳍”方向的长度,而沟道的宽度是两倍于“鳍”高度再加上“鳍”的宽度。

“鳍”的高度限制了驱动电流和栅电容,而“鳍”厚度会影响到对阈值电压和短沟道的控制,还会影响到其二级效应,如功耗。

在一个22nm技术节点的器件中,“鳍”宽度可能为10~15nm范围,理想的“鳍”高是宽度的两倍或更多,因为增加“鳍”的高度可以提高晶体管的集成密度,以在更小的占位面积上形成更大的有效栅宽。

然而,对体硅FinFET器件而言,更高的“鳍”使得对“鳍”的刻蚀、“鳍”壁的凹槽刻蚀,以及隔离注入变得更为困难,这些将在下面的文章中进行讨论。

在器件的制造中要控制如此小尺寸的3D结构,这就给工艺控制带来新的挑战。

构建“鳍”结构的沟槽刻蚀,必须保持好2:

1或者更大深宽比结构的垂直轮廓,使其边墙具有最小的粗糙度。

差异性及良品率问题是制造厂商决定采用哪种制备工艺的重要考虑因素。

本文将分析两种具有应用前景的FinFET工艺流程的性能、差异性及其成本,其中一种是采用绝缘体上硅(SOI)基片,另外一种是使用离子注入形成PN结来进行“鳍”隔离的体硅基片。

采用SOI基片的工艺流程。

基于SOI的FinFET工艺最为简单。

形成“鳍”的刻蚀过程将会在进行到晶圆氧化埋层时自动中止,“鳍”的高度将完全取决于初始SOI上Si层的厚度。

此外,由于存在着氧化埋层,相邻的“鳍”之间在电学上是完全隔离的,不需要再进行额外的隔离工艺。

在全耗尽的情况下,该技术节点将考虑采用未经掺杂沟道的器件,因而只需要制作栅极并对源/漏进行注入掺杂就可以完成整个器件的制造工艺。

采用体硅基片的工艺流程。

与SOI相比,如果采用体硅基片,就无法在“鳍”的底部形成清晰的界面,而且不存在本征隔离层(氧化层)。

因而就必须采用额外的器件隔离工艺。

在形成PN结隔离的工艺流程中(图1),完成“鳍”的刻蚀后紧跟着要进行氧化物的填充步骤。

氧化物要能够很好地填充很深的、且深宽比大的沟槽,要保证不产生孔洞和其它类型的缺陷。

随后磨削抛光氧化物直至硅暴露,以确定“鳍”的高度,再进行对氧化层进行凹槽刻蚀以便在“鳍”之间清理出空间。

这种氧化层凹槽刻蚀和最初的硅沟槽刻蚀相类似,都没有明显的刻蚀终止层,其刻蚀深度完全取决于刻蚀的时间,随着设计中“鳍”间隔变化而使“鳍”密度发生变化时,刻蚀就会受到微负载(图形)效应的影响。

虽然填充的氧化物会将相邻的“鳍”绝缘隔离,但是晶体管依然可以通过氧化物下部的硅衬底相连,这就需要通过高剂量的、大角度离子注入以在“鳍”的底部形成掺杂PN结,才能最终形成器件的隔离结构。

图1.采用PN结隔离的体硅FinFET器件的工艺流程。

“材料隔离”工艺流程。

一些研究还在考虑采用“材料隔离”工艺(图2),在该工艺中,氧化物从沟槽向“鳍”的底部生长并穿透形成隔离,需要采用一种硬掩模边墙来保护“鳍”的两壁。

在这种工艺中,氧化物生长程度取决于其生长的时间,这就要求所有的“鳍”都必须具有相同的厚度,才能形成完全的氧化物隔离。

氧化物隔离生长过程本身就非常难以控制,而且与PN结隔离工艺相比还增加了多个工艺步骤。

由于其自身的复杂性,我们认为“材料隔离”方法在实际生产中并不可行,所以在随后的分析讨论中我们将不再考虑这种工艺。

图2.“材料隔离”体硅FinFET器件的工艺流程。

SOI和体硅工艺都可以达到类似的性能

对于器件的直流DC性能而言,尺寸类似的SOI和体硅FinFET器件可以获得相似的开/关电流比[1]。

但在考虑PN结漏电流和寄生电容等参数时,两种器件的表现就会开始显现出差别。

由于SOI本身就具有底部的平面氧化层,使其更容易实现22nm技术节点器件的目标性能。

正如前面所述,在采用PN结进行隔离的FinFET器件中,其隔离是通过在“鳍”底部形成高剂量(1018/cm3)的掺杂层来实现的。

该掺杂层可以在凹槽氧化物淀积和刻蚀之前或者之后通过离子注入形成,但在PN结和氧化层之间的对准就变得至关重要,它对器件性能的影响与平面晶体管中边墙-沟道间的对准要求相类似。

在凹槽氧化物淀积和刻蚀之前就进行离子注入会放大凹槽刻蚀的非均匀性,从而对器件性能产生影响,而凹槽刻蚀工艺步骤的本身就已经是一个技术上的挑战。

所以,为了能商业化应用大多数工艺考虑都先进行氧化物淀积和刻蚀,使用氧化层来对准PN结的离子注入。

即使是采用这种工艺顺序,优化了注入工艺的参数,以在“鳍”的底部形成适当的掺杂PN结,但它同样也是充满了挑战性。

即使是在最佳条件下,离子注入工艺也会产生掺杂梯度,由于在“鳍”体的内部存在注入掺杂的梯度分布,使得要在“鳍”底形成足够剂量的注入掺杂成为一件非常困难的事情。

要使SOI和体硅FinFET器件可以达到相当的漏电性能,体硅FinFET中掺杂剂量的随机涨落都将影响到晶体管的性能(图3)。

SOI器件由于不需要进行PN结隔离的离子注入,就不会有这种效应。

图3.SOIFinFET、体硅FinFET和平面晶体管的性能比较[2]。

PN结隔离和SOI氧化埋层隔离在结构的不同还会影响到器件的寄生电容。

由于设计结构不同,所有的FinFET器件都比类似的平面晶体管更容易产生寄生效应[3]。

氧化埋层的存在有利于减少SOI器件的寄生电容,而PN结隔离的体硅器件却需要接受“PN结”带来的额外电容。

然而,当“鳍”的高度增加时器件的总电容会增大,使得PN结电容的贡献将变成次要的因素。

如果“鳍”高度大于40~50nm,PN结电容的存在将只会使环形振荡器的性能影响5%~6%。

减少差异性

虽然可以通过对其性能的对比来评价不同的候选工艺,但是“最好”的工艺往往由于其由于设计不同而差别很大。

高性能的设计可能并不太关注器件的总体成本,而是更为关注器件性能的差异性以及如何来降低它们的差异性。

一种低功耗的消费类芯片可能最为关心的是漏电流和功耗问题,但也可能对成本非常敏感。

与其试图解决所有这些问题,还不如将我们的分析聚焦于在简化了的通用工艺的差异性和成本问题上。

从器件成本和差异性的观点来看,我们的模型可以被看作是最好的案例:

它只考虑一个具有单一阈值电压的数字电路单元。

假设只考虑一个“鳍”的节距,这是一个可能的假定,就像制造商可能会通过在一个给定的器件上增加“鳍”的数量来调整晶体管的线度一样。

采用单个“鳍”节距可以简化光刻和蚀刻工艺,这是一个重要的简化考虑,因为上述两种工艺本身都很可能在22nm技术节点时面临着挑战。

更实际的器件可能需要增加成本和增加工艺的步骤数。

添加阈值电压调整就需要增加新的离子注入掩模,而添加金属层需要增加更多的金属层淀积、图形光刻以及抛光等工艺步骤。

我们希望读者能够在我们所提供的框架内来评价它们本身的工艺。

为了对器件差异性进行分析,我们假设SOI和体硅的FinFET器件都采用类似的工艺设备集合,例如,我们认为SOI沟槽刻蚀并不比体硅相应的工艺能达到更严格的容差,我们还假设两种工艺设备集合在随后都能进行相同的工艺改进。

然而,体硅FinFET器件所需要增加的额外工艺步骤切实增加了其差异性。

在SOI工艺流程中(表1),最主要的差异性来源是基片硅层本身(它决定了“鳍”的高度)、“鳍”刻蚀的