数字电路与逻辑设计A卷.docx

《数字电路与逻辑设计A卷.docx》由会员分享,可在线阅读,更多相关《数字电路与逻辑设计A卷.docx(12页珍藏版)》请在冰豆网上搜索。

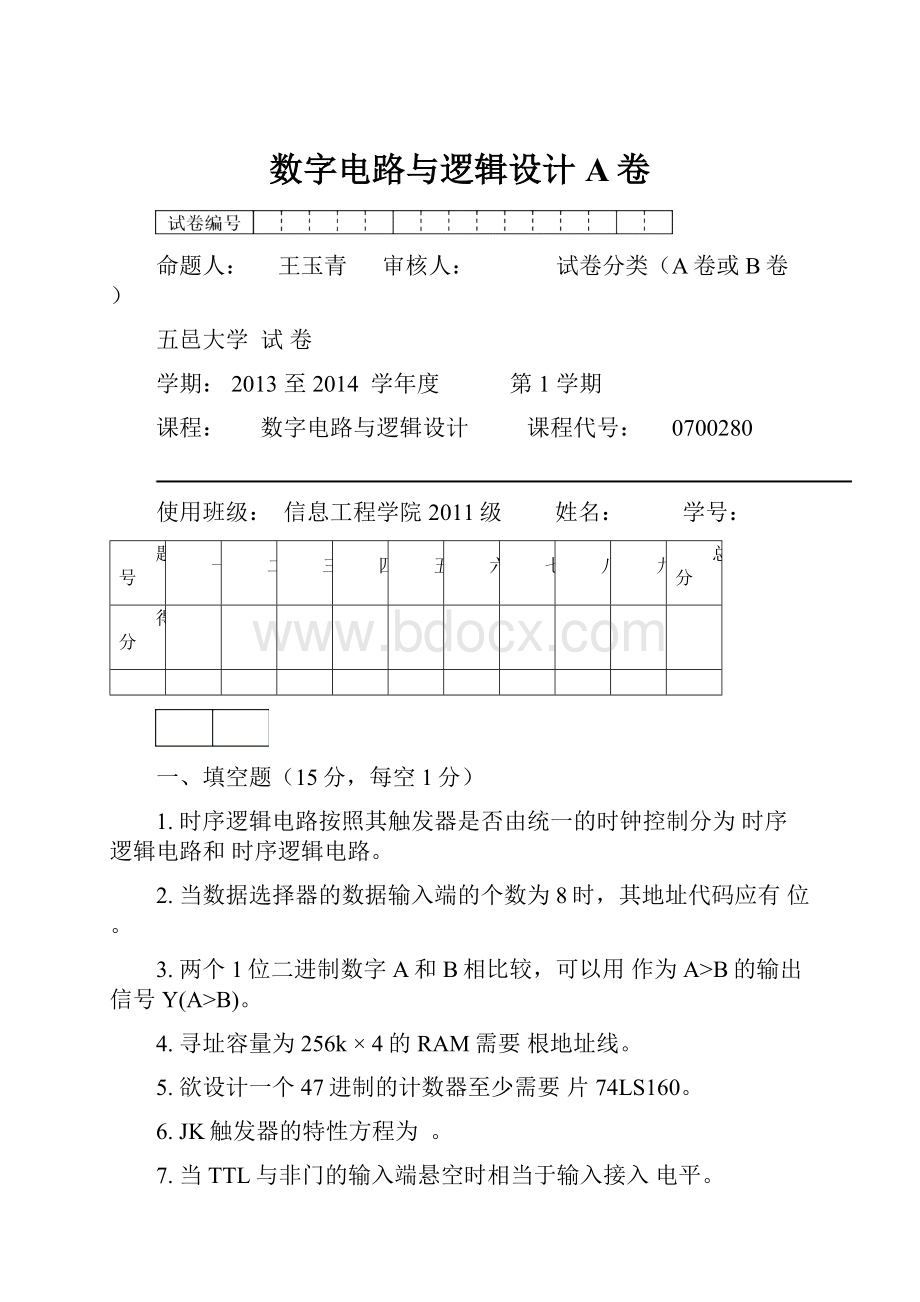

数字电路与逻辑设计A卷

命题人:

王玉青 审核人:

试卷分类(A卷或B卷)

五邑大学试卷

学期:

2013至2014学年度 第1学期

课程:

数字电路与逻辑设计 课程代号:

0700280

使用班级:

信息工程学院2011级 姓名:

学号:

题号

一

二

三

四

五

六

七

八

九

总分

得分

一、填空题(15分,每空1分)

1.时序逻辑电路按照其触发器是否由统一的时钟控制分为时序逻辑电路和时序逻辑电路。

2.当数据选择器的数据输入端的个数为8时,其地址代码应有位。

3.两个1位二进制数字A和B相比较,可以用作为A>B的输出信号Y(A>B)。

4.寻址容量为256k×4的RAM需要根地址线。

5.欲设计一个47进制的计数器至少需要片74LS160。

6.JK触发器的特性方程为。

7.当TTL与非门的输入端悬空时相当于输入接入电平。

8.模数转换器(ADC)两个最重要的指标是转换精度和。

9.A/D转换通常经过、、、四个步骤。

10.TTL门电路中,输出端能并联使用的有和。

二、选择题(11分,每空1分)

1.下列各式中哪个是三变量A、B、C的最小项?

。

A.

B.

C.

D.

2.下列公式中哪个是错误的?

。

A.

B.

C.

D.

3.采用集电极开路的OC门主要解决了。

A.TTL门不能相“与”的问题

B.TTL门的输出端不能“线与”的问题

C.TTL门的输出端不能相“或”的问题

4.触发器有两个稳态,,存储4位二进制信息需要个触发器。

A.2B.4C.8D.16

5.欲使D触发器按

工作,应使输入端D=。

A.0B.1C.QD.

6.要构成容量为4k×8的RAM,需要片容量为256×4的RAM。

A.2B.4C.8D.32

7.3线-8线译码器处于译码状态时,当输入A2A1A0=010时,输出

=。

A.11101111B.11111011C.11111101D.11011111

8.多谐振荡器可产生。

A.正弦波B.矩形脉冲C.三角波D.锯齿波

9.555定时器构成施密特触发器时,其回差电压为。

A.VCCB.VCC/2C.VCC/3D.2VCC/3

10.D/A转换器能够将转变成。

A.正弦信号B.数字信号C.模拟信号D.方波信号

三、判断题(8分,每题1分)

()1.编码器是时序逻辑电路。

()2.施密特触发器可用于将三角波变换成正弦波。

()3.单稳态触发器的暂稳态时间与输入触发脉冲宽度成正比。

()4.四变量的最小项共有8种组合。

()5.具有推拉输出的TTL门的输出端不可以并列使用。

()6.CMOS门的输入端不可以悬空。

()7.将TTL与非门作非门使用,则多余输入端应接低电平。

()8.T触发器,在T=1时,加上时钟脉冲,则触发器翻转。

四、(共9分)

用卡诺图法化简逻辑函数

五、(共17分)

已知同步时序电路如图1所示。

试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并说明该电路的功能。

图1

六、(共15分)

试利用74LS161和反馈预置数法设计一可控进制计数器:

当控制变量X为1时为12进制计数器,X=0时为10进制计数器,并画出电路图。

74LS161功能表

七、(共6分)

若将1024×1位的RAM芯片组成2048×2位的RAM电路,

(1)应需几片1024×1位的芯片?

(2)还需要哪种集成芯片?

(3)试画出扩展电路,1024×1位的ROM芯片的逻辑符号如下图所示。

(8分)

八、(共6分)

图2(a)所示为由555定时器构成的声控报警电路。

声音经接收放大后的信号如图2(b)所示,vI的峰值4V。

(1)分别说出555定时器1和555定时器2所构成单元电路的名称;

(2)请计算报警的时间;

九、(共13分)

某汽车驾驶员培训班进行结业考试。

有3名评判员,其中A为主评判员,B、C为副评判员。

评判时按少数服从多数原则,但若主评判认为合格,也可通过。

试设计一个逻辑电路实现上述功能。

要求:

1.列出输出和输入的真值表;2.写出逻辑函数表达式;3.试用4选1数据选择器74HC153实现评判的规定逻辑功能。

任课老师:

试卷分类(A卷或B卷)A

五邑大学试卷参考答案及评分标准

学期:

2013至2014学年度 第1学期

课程:

数字电路与逻辑设计 课程代号:

0700280

使用班级:

信息工程学院2011级

一、填空题(15分,每空1分)

5.时序逻辑电路按照其触发器是否由统一的时钟控制分为异步时序逻辑电路和同步时序逻辑电路。

6.当数据选择器的数据输入端的个数为8时,其地址代码应有3位。

7.两个1位二进制数字A和B相比较,可以用

作为A>B的输出信号Y(A>B)。

8.寻址容量为256k×4的RAM需要18根地址线。

5.欲设计一个47进制的计数器至少需要2片74LS160。

6.JK触发器的特性方程为

。

7.当TTL与非门的输入端悬空时相当于输入接入高电平。

8.模数转换器(ADC)两个最重要的指标是转换精度和速度。

9.A/D转换通常经过采样、保持、量化、编码四个步骤。

10.TTL门电路中,输出端能并联使用的有OC门和三态门。

二、选择题(11分,每空1分)

3.下列各式中哪个是三变量A、B、C的最小项?

C。

A.

B.

C.

D.

4.下列公式中哪个是错误的?

C。

A.

B.

C.

D.

4.采用集电极开路的OC门主要解决了B。

A.TTL门不能相“与”的问题

B.TTL门的输出端不能“线与”的问题

C.TTL门的输出端不能相“或”的问题

5.触发器有两个稳态,,存储4位二进制信息需要B个触发器。

A.2B.4C.8D.16

5.欲使D触发器按

工作,应使输入端D=D。

A.0B.1C.QD.

6.要构成容量为4k×8的RAM,需要D片容量为256×4的RAM。

A.2B.4C.8D.32

7.3线-8线译码器处于译码状态时,当输入A2A1A0=010时,输出

=B。

A.11101111B.11111011C.11111101D.11011111

8.多谐振荡器可产生B。

A.正弦波B.矩形脉冲C.三角波D.锯齿波

9.555定时器构成施密特触发器时,其回差电压为C。

A.VCCB.VCC/2C.VCC/3D.2VCC/3

10.D/A转换器能够将B转变成C。

A.正弦信号B.数字信号C.模拟信号D.方波信号

三、判断题(8分,每题1分)

(×)1.编码器是时序逻辑电路。

(×)2.施密特触发器可用于将三角波变换成正弦波。

(×)3.单稳态触发器的暂稳态时间与输入触发脉冲宽度成正比。

(×)4.四变量的最小项共有8种组合。

(√)5.具有推拉输出的TTL门的输出端不可以并列使用。

(√)6.CMOS门的输入端不可以悬空。

(×)7.将TTL与非门作非门使用,则多余输入端应接低电平。

(√)8.T触发器,在T=1时,加上时钟脉冲,则触发器翻转。

四、(共9分)

用卡诺图法化简逻辑函数

解:

(填1共5分,圈1共2分,结果2分)

五、(共17分)

已知同步时序电路如图1所示。

试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,并说明该电路的功能。

图1

解:

电路的驱动方程、状态方程和输出方程分别为:

(7分,其中驱动方程3分,状态方程3分,输出方程1分)

根据状态方程和输出方程,可做出的状态转换图如图解1所示(6分:

每个次态输出0.5分,共4分;输出Y共2分),(设电路的初态为000)。

解1状态转换图

综上分析可知:

电路对时钟信号进行计数。

每经过7个时钟脉冲,电路输出一个脉冲。

所以是7进制计数器,Y输出是进位脉冲。

(4分)

六、(共15分)

试利用74LS161和反馈预置数法设计一可控进制计数器:

当控制变量X为1时为12进制计数器,X=0时为10进制计数器,并画出电路图。

解:

假设预置数信号DCBA=0000(此处可任意设置,故答案不唯一,2分)

则对应X=0和X=1的状态转换表如下:

(6分)

置位信号为:

(2分)

实现的电路图如下:

(5分)

七、(共6分)

若将1024×1位的RAM芯片组成2048×2位的RAM电路,

(1)应需几片1024×1位的芯片?

(2)还需要哪种集成芯片?

(3)试画出扩展电路,1024×1位的ROM芯片的逻辑符号如下图所示。

(8分)

答案:

(1)需要4片;

(2)还需要非门;(3)如下图

八、(共6分)

图2(a)所示为由555定时器构成的声控报警电路。

声音经接收放大后的信号如图2(b)所示,vI的峰值4V。

(1)分别说出555定时器1和555定时器2所构成单元电路的名称;

(2)请计算报警的时间;

解:

(1)555定时器1构成施密特触发器(2分),555定时器2构成单稳态触发器;(2分)

(2)计算报警的时间:

(2分)

九、(共13分)

某汽车驾驶员培训班进行结业考试。

有3名评判员,其中A为主评判员,B、C为副评判员。

评判时按少数服从多数原则,但若主评判认为合格,也可通过。

试设计一个逻辑电路实现上述功能。

要求列出输出和输入的真值表;写出逻辑表达式;试用4选1数据选择器74HC153实现评判的规定逻辑功能。

解:

根据逻辑设计要求,设定3个输入变量A、B、C,并规定如下:

主评判员A的意见:

A=1认为合格,A=0认为不合格。

(1分)

副评判员B和C的意见:

B=1和C=1认为合格,B=0和C=0认为不合格。

(1分)

输出变量Y=1认为通过,Y=0认为不通过。

(1分)

列真值表(4分)(画图3分)

A

B

C

Y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

1

写出逻辑函数表达式:

(3分)